一种数字化中频接收机的研究与实现

2012-07-13邱冬冬鲁新龙金华松

邱冬冬,鲁新龙,董 炯,金华松

(中国卫星海上测控部 江苏 江阴 214431)

软件无线电(Software Radio)的概念自上世纪末提出以来,最近几年取得了引人注目的进展。数字化中频接收机是软件无线电的重要部分。软件无线电的主要原理是将数字化推向前端,即是把模数/数模转换器(ADC/DAC)尽量放在射频端,这是数字化接收机的发展方向,也是软件无线电的理想实现方法。早期的数字化接收机受ADC发展水平的限制,采用正交双通道零中频的实现方案,即将射频通过变频变换到零中频(基带),正交解调得到模拟的正交信号之后再进行数字化。该方案的频率变换主要都在模拟部分实现,数字化较少,不是真正意义上的数字化接收机。而且,此方案实现起来设备量较大,方案中的正交混频器是模拟器件,得到的正交I,Q信号也难以保证幅相正交的精度[1]。目前比较成熟的数字化接收机理论和实现方案是中频数字化接收机,即将射频信号经一次或二次下变频后,在中频(或高中频)直接采样,再数字下变频到基带,得到正交I,Q信号。

软件无线电技术的迅猛发展,使其在航天测控领域的应用成为了可能。在我国当前的C频段微波统一测控系统中,中频接收机主要由模拟电路构成,这种结构已经逐渐不能达到测控系统的精度要求。数字化已经成为中频接收机的必然发展趋势,关于这方面的研究,已经开展了很多[2-6]。文中设计了一种数字化中频接收机,该方案采用软件无线电思想,并给出了采用FPGA和DSP实现该接收机的方法。

1 系统工作原理

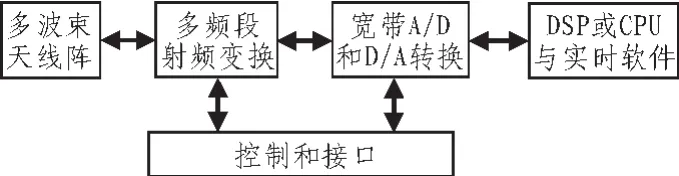

软件无线电的目标和思路是在标准化、完全可编程的硬件平台上,用不同的软件适应通信、测控等业务的各种体制,并实现尽可能多的无线功能,其原理框图如图1所示。在理想的软件无线电中,系统的所有功能都在一个通用的处理器上用软件实现,原则上允许同一硬件平台支持任何物理层和更高的协议层。

图1 软件无线电的结构框图Fig.1 Software radio structure diagram

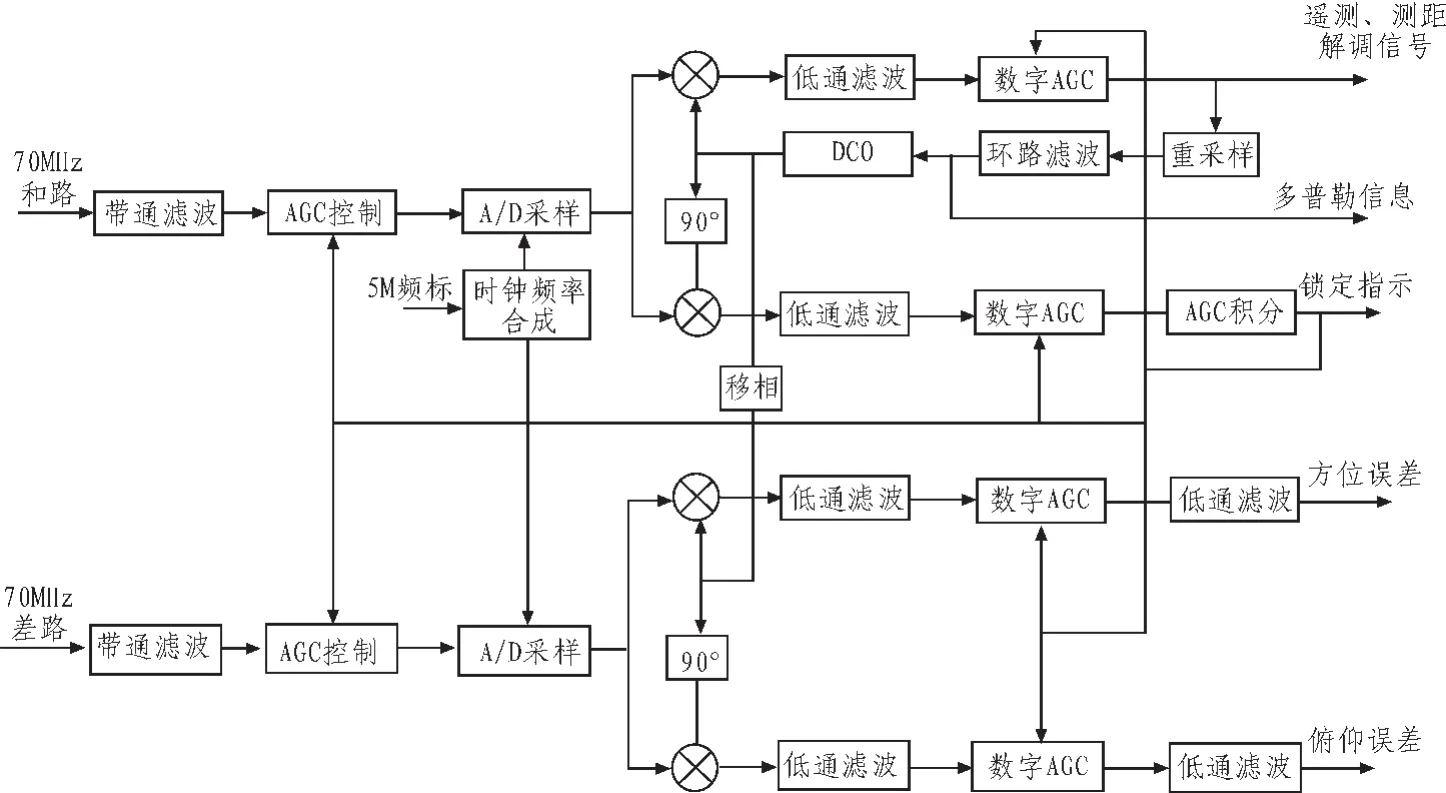

文中所设计的数字化中频接收机的应用了软件无线电的设计思路,在中频70 MHz上进行带通采样。输入的信号有和路和差路,其中和路信号包含有测距、遥测等信息,而差路信号则含有角误差信息。

图2 数字化中频接收机原理框图Fig.2 Principle diagram of digital intermediate frequency receiver

和路和差路的输入信号经过滤波和放大后,被A/D采样变为数字信号,分成I、Q两条支路,分别完成数字信号的下变频。其中和路信号分成两条支路分别解调出遥测、测距信息并完成信号幅度检测。环路鉴相输出的误差信号经数字滤波后控制数字压控振荡器(DCO)的频率和相位完成闭环,并给出多普勒频率偏移信息。和路信号为移相后的环路DCO输出后信号,该信号与差路信号进行鉴相检测出方位和俯仰角误差信息。移相器与DCO进行一体化设计,实现和路对差路信号幅度的归一化的AGC控制信号由和路产生。图2所示的是系统原理框图。

2 关键技术及器件选择

2.1 ADC的设计

带通采样适用于带通输入信号,因此将其作为理想的高速中频采样方案[7]。

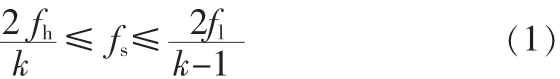

为了保证采样后不发生频谱混叠,采样频率必须满足:

其中k取满足以下条件的整数:

其fs是采样频率,fh是信号最高频率,fl是最低频率。本方案中,载波中心频率为70 MHz,信号带宽为3 MHz。则有:

由以上公式,为了保证采样变频输出各段频谱不重叠采样率,fs的可选择范围很大。

ADC的性能必须满足自身和采样后系统的处理能力,其位数则必须符合一定的动态范围要求及数字处理部分的精度要求。用于中频频段的A/D转换器件,一般要求动态范围在 60~80 dB。

ADC选用Analog Devices公司的芯片AD9432。AD9432为单片式12位的芯片,具有精度高、速度高和性能高的优点,内部有采样保持电路,在整个工作频率范围内具有较好的动态性能指标。对于输入带宽为25 MHz的信号,它的无杂散动态范围可达80 dB,一般情况信噪比为67 dB,模拟输入带宽能达到300 MHz,其最高采样速率可达105 MHz,非常适合用来进行中频采样。实际应用中,考虑到组合干扰等因素,采样频率设定为55 MHz,设为此值可以降低后续滤波器的设计难度。

由于输入信号动态范围为-52~8 dBm,最低幅度低于ADC的最小分辨率,所以要加一个放大器。而且考虑到由于电路设计中,还有许多电磁干扰因素,中频数据采集ADC的有效位数定低于12位,较好的情况下能达到10位~11位,使得实际动态范围不一定达到60 dBm,因此该放大器还需兼顾一定的AGC功能。这里选用了NS公司的数控放大器CLC5526。

2.2 数字下变频器的设计

在ADC采样后,信号的频率下移到15 MHz附近,还需在鉴相时进行数字下变频才能完成载波信号的解调。

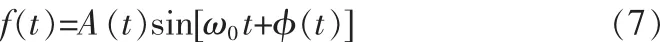

设输入的中频模拟信号为:

采样后的信号为:

式中:

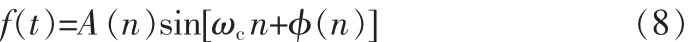

DCO产生的信号为 sin(ωcn),经 90°移相后变为正交信号cos(ωcn),与采样信号在混频器相乘后得:

通过低通滤波器滤除其中的倍频分量后,得到所需的正交 I,Q 信号:

由于信号的采样频率较高,即I(n)和Q(n)的速率很高,一般远大于窄带信号的带宽,这时可对其进行速率转换(抽取),以降低此时的输出数据率。不过,应当注意的是抽取后的数据率应大于信号带宽。

DCO的功能是产生频率可变的正交正、余弦样本,并作为数字下变频器的本振信号。输入的信号与DCO产生的正弦波样本在数字鉴相器中进行鉴相。由于数字载波中心频率为15 MHz,所以DCO产生的正弦波样本信号的基频应为15 MHz。这样,鉴相的同时完成了数字下变频的功能。乘法器输出的乘积样本再经过低通滤波器,信号频谱被搬移到基带,这样就完成了载波信号解调。DCO是决定数字下变频(DDC)性能的主要因素之一。

数字下变频部分的运算量很大,如果全部由DSP来完成,对DSP需要具有很高的处理速度,比较难以实现[8]。目前,数字下变频功能的实现方式主要有两种:一种是使用专门的数字下变频芯片,如Intersil公司的HSP50214、HSP50216;另一种是采用FPGA,自行设计数字下变频器。

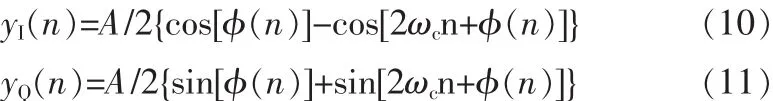

现场可编程门阵列(FPGA)的主要优点就是其完全可编程性[9]。在设计中需要处理很多信息,为了提高可编程性和系统的集成度,设计中采用了FPGA实现数字下变频的方案。本文设计的中频数字接收机,有4路70 MHz的中频信号输入。在本文的设计方案中,FPGA选用ALTERA公司APEX系列的EP2A15,其最大门数可达1 900 000门,最高工作频率可达200 MHz以上,能满足系统的要求。方案中,不仅4路中频采样信号的数字下变频在FPGA中实现,而且抽取、滤波、以及DCO均集成在FPGA中,FPGA的资源利用率达到了 70%~80%。

3 硬件平台结构

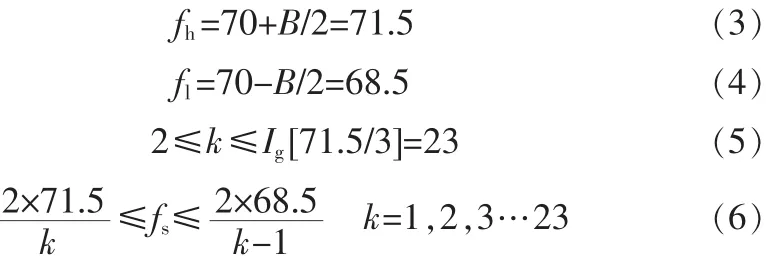

数字处理平台基于FPGA+DSP的结构来构建,将FPGA的可编程性及高速特性与DSP的复杂运算能力相结合,共同实现数字解调锁相环,完成载波跟踪、环路锁定指示和相关AGC电压的产生。数据处理平台与微机CPU进行的数据交换采用PCI总线接口。结构框图如图3所示。

图3 中频接收机硬件平台结构图Fig.3 Intermediate frequency receiver hardware structure chart

这种硬件平台结构具有通用、标准和模块化的特点,通过软件编程来实现接收机的各种功能。同时,设计注重结构的开放性和全面可编程性,通过软件的更新改变硬件的配置结构,实现新的功能。采用标准的、高性能的开放式总线结构(PCI),有利于硬件模块的升级和扩展。

4 结束语

鉴于目前硬件水平的限制,直接对射频信号进行数字化存在困难,只能先将射频信号下变频至中频信号。数字中频接收机是对中频信号进行带通采样数字化,同时还将信号频谱向下复制到零频附近。中频接收机的数字化是测控系统终端数字化的关键。文中设计了一种基于软件无线电、采用FPGA和DSP架构的中频数字化接收机实现方案,并分析了其系统工作原理和关键技术细节。该方案基于一个标准的硬件平台,通过不同的加载软件,该平台可以演进成适应多种调制方式的中频接收机,其处理能力可以满足目前测控系统中绝大部分场合的要求。该平台现已应用于国内某C频段统一测控系统中,大大提高了该系统的整体性能。

[1]何勤,束永江.一种通用中频数字化接收机的实现[J].现代电子技术,2009(11):94-97.

HE Qin,SHU Yong-jiang.Implementation of general IF digital receiver[J].Modern Electronics Technique,2009(11):94-97.

[2]雷兵.雷达数字化借手机设计[J].信息化研究,2010,36(8):54-56.

LEI Bing.Design of the radar digital receiver[J].Informationization Research,2010,36(8):54-56.

[3]汪敏,胡泽,肖斌.基于FPGA的中频数字化接收机系统实现[J].信息技术,2007(7):113-115

WANG Min,HU Ze,XIAO Bin.Realization of IF digital receiver system based on FPGA[J].Information Technology,2007(7):113-115.

[4]张晓明,陈禾,仲顺安.脉冲多普勒小型数字化中频接收机的设计与实现[J].电视技术,2008,48(11):5-9.

ZHANG Xiao-ming,CHEN He,ZHONG Shun-an.Design and implementation of the miniaturized and digitized IF receiver for a PD radar seeker[J].Telecommunication Engineering,2008,48(11):5-9.

[5]薛继华.一种中频数字化接收机中的自动增益控制方案[J].南通纺织职业技术学院学报,2007,7(2):11-14.

XUE Ji-hua.A scheme of auto gain control applied in digital intermediate frequency receiver[J].Journal of Nantong Textile Vocational Technology College,2007,7(2):11-14.

[6]靳鹏飞,杨海涛.中频数字化接收机系统设计与实现[J].科学技术与工程,2008,8(11):2972-2976.

JIN Peng-fei,YANG Hai-tao.Design and implementation of a digital intermediate frequency receiver[J].Science Technology and Engineering,2008,8(11):2972-2976.

[7]陈礼光,徐福安,张进,等.软件无线电接收机中频数字化设计[J].现代电子技术,2004(11):94-97.

CHEN Li-guang,XU Fu-an,Zhang Jin,et al.Design of software radio receivers IF digitalization system[J].Modern Electronics Technique,2004(11):94-97.