FPGA在多轴步进电机控制器中的应用

2012-07-04王邦继刘庆想周磊李相强张健穹

王邦继, 刘庆想, 周磊, 李相强, 张健穹

(西南交通大学物理科学与技术学院,四川成都610031)

0 引言

步进电机是一种将输入的脉冲转化为相应的角位移的执行元件。其输入为脉冲序列,输出为相应的角度增量。在正常的工作状态下,输出与输入具有严格的对应关系,不受电压波动和负载变化等影响。步进电机的步进角由转子齿数及相数决定,由于结构限制,不能做到太小,从而限制了其应用。近年来,随着细分驱动技术的发展,步进角大大减小,且输出力矩有所增加,使得步进电机在速度及负载具有较宽变化范围时,能够实现平滑稳定的运动,扩展了其应用范围[1]。

传统的步进电机控制器大多以DSP为核心,再辅以必要的外围分立器件构成[2-3]。这种结构的步进电机控制器的优点在于其硬件结构清晰,能够运行复杂的控制算法,缺点是其硬件资源限制以及控制算法的串行运行,不能满足多轴步进电机控制要求。随着FPGA技术的飞速发展以及IP设计思想的普遍认同,SOPC正在成为FPGA最重要的发展方向之一。将微处理器、存储器、通信模块、多个电机IP核等功能模块集成到单一FPGA芯片上,就构成了一个多轴电机控制器的SOPC系统。目前国内外关于多轴电机控制器的研究相对较少[4-5],且大部分都集中在一些基本部件的开发方面[6]。

在IP设计思想的指导下,设计了一种高性能步进电机IP核,在此基础上,进一步集成了微处理器、存储器、通信模块等,构建了多轴步进电机控制器的SoPC系统,可应用于多轴伺服系统的工业领域。

1 步进电机IP核

1.1 硬件描述

通过设定其内部寄存器值,步进电机IP核能控制步进电机按设定的速度曲线模式运行。该IP核有3个主要功能模块构成,如图1所示。

1)Avalon总线接口:它使该IP核具有Avalon总线接口,可与其它具有相同接口的IP核互联。

2)QEP电路:用于连接一个光电编码器获取电机转子位置等信息,用于判断电机运行是否失步,使本系统可根据用户需要成为闭环控制系统。

3)速度剖面产生:根据设定的速度曲线参数,计算出每个步进脉冲的步进周期,并输出步进脉冲序列到步进电机驱动器,从而驱动步进电机按设定的速度曲线模式运行。它由状态机,步进周期计算模块和PWM电路三部分构成。

图1 步进电机IP核Fig.1 Stepper motor IP core

每个步进电机IP核控制一台步进电机,为了控制多台步进电机,它需要被复用多次。由于所有IP核都具有Avalon总线接口,嵌入到FPGA中的NiosⅡ软核能控制各个步进电机IP核。NiosⅡ软核负责各个步进电机运动轨迹的计算,它为不同IP核提供速度曲线参数。

1.2 Avalon总线接口

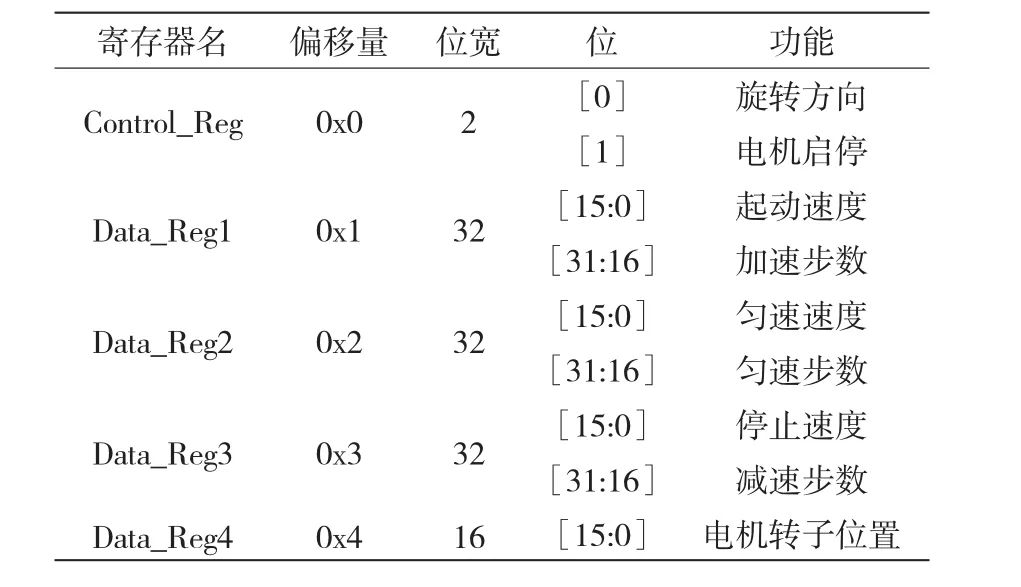

Avalon总线接口为步进电机IP核提供了一个标准的Avalon总线从端口,NiosⅡ软核通过此接口能对步进电机IP核中的寄存器进行读写操作,从而实现步进电机的运动控制。步进电机IP核中的寄存器和接口映像如表1所示。

表1 寄存器和接口映像Table 1 The registers and interface image

1.3 QEP电路

本文采用增量式光电编码器作为位置检测装置,其输出为3路信号,其中两路为正交的A、B脉冲信号,一路为零位检测脉冲信号Z。在正常工作时,准确的检测转子位置是非常重要的,通常通过对正交的A、B脉冲进行四倍频计数,可以得到转子的位置。本文设计的QEP电路如图2所示,包括数字滤波器、方向判断电路、四倍频电路和增/减计数器等。其中,数字滤波器用来滤除电机旋转时在编码器A、B和Z三相输出端产生的数字信号噪音。方向判别和四倍频电路可得到电机转子的旋转方向与四倍频输出,再经过增/减计数器,便可以得到(n+1)位的电机转子位置信号。

图2 QEP电路框图Fig.2 Block diagram of QEP circuit

1.4 速度剖面产生

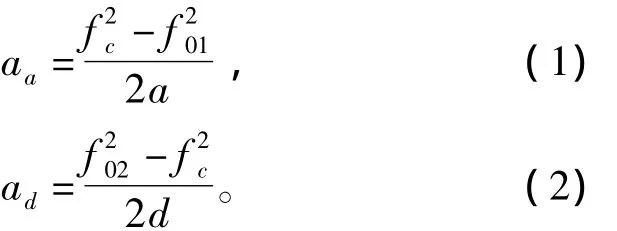

速度剖面产生模块可以实现三种速度曲线模式:匀速模式、三角形加减速模式和梯形加减速模式。这个模块的输入是一组速度曲线参数,包括起动速度f01、匀速速度fc、停止速度f02、加速步数a、匀速步数c和减速步数d。若按线性加速或减速运行的话,则加速阶段和减速阶段的加速度aa、ad分别为

由步进电机运行原理及运动学方程,可求得加速阶段、匀速阶段和减速阶段每个步进脉冲的步进周期 tx、ty和 tz分别为[7]

根据上述分析,该模块需要计算出每个步进脉冲的步进周期t,并产生步进脉冲序列。

1.4.1 状态机

状态机是该模块中最重要的部分,它负责内部状态的转换,步进周期计算和PWM电路的初始化,以及各部分之间的时序调度。

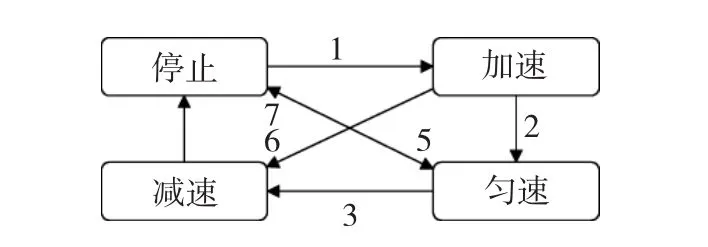

它有4种状态:停止、加速、匀速和减速,它们之间的转换关系如图3所示。当应用程序开启或者电机转动完成时,保持在停止状态。控制寄存器的启停位置1后,若加速步数大于0(1),进入加速状态;否则(5),进入匀速状态。

图3 速度剖面产生模块的状态机Fig.3 State machine of velocity profile generator

在加速状态,应用程序把步进电机从起动速度加速到匀速速度,在该过程中正好走完加速步数。加速步数完成后,若匀速步数大于0(2),进入匀速状态;否则(6),进入减速状态。

在匀速状态,应用程序驱动步进电机匀速运行,直到走完匀速步数。匀速步数完成后,若减速步数大于0(3),进入减速状态;否则(7),进入停止状态。

在减速状态,应用程序把步进电机从匀速速度减速到停止速度,在该过程中刚好走完减速步数。减速步数已经完成后(4),进入停止状态。

当从匀速状态或减速状态进入停止状态时,控制寄存器的启停位被清0,这表明此次运动已经完成,可以进入新的运动周期了。

1.4.2 步进周期计算模块

由式(3)~式(5)可知,步进周期Δt的计算是非常复杂的,要经过两次乘法、一次开方和一次除法等运算才能得到。在FPGA开发应用中,大多数EDA软件(如QuartusⅡ)都提供乘除法、开方运算的设计向导,或提供LPM宏函数,但普遍占用资源量大。在我们的应用中,要求计算精度高、资源敏感而计算时延要求并不高,这时我们需要一种保证计算正确且资源开销低的FPGA实现方法。本文采用递推结构的乘法、除法和开方运算的串行实现方法[8],该方法以处理时间换取资源,具有占用硬件资源少,实现简单等特点。

1.4.3 脉冲信号产生

步进电机高速运行时,步进周期Δt的数值一般都在微秒量级,因此,必须设计精确的计时方法。本文在FPGA上设计一个32位计数器(FPGA工作频率f为50 MHz),它的最大计数周期约为85.9 s,最基本的计数单位T为0.02 μs。因此,通过向计数器写入不同的计数初值c0,就可以在不同的定时时刻计时,而且定时精度可达0.02 μs。

用计算出的步进周期Δt除以计数器的基本计数单位T,可以得到一个计数初值c0,将这个值写入到计数器中,并使之开始减1计数。同时在FPGA上设计一个32位比较器,比较器的值为计数初值c0的一半。当计数器计数值大于比较器的值时,脉冲信号输出为低;反之,脉冲信号输出为高。

1.5 仿真验证

在步进电机IP核的对外接口中,除了Avalon总线接口信号外,dir为电机的正/反转信号,pulse为电机的步进脉冲信号,encoder为编码器的脉冲信号。通过Avalon总线接口向IP核中的三个数据寄存器写速度曲线参数(三角形加减速模式:起动速度和停止速度为0,匀速速度为2 560 step/s,加速步数、匀速步数和减速步数分别为64、0和64 step),并把控制寄存器中的方向位置1,该IP核的仿真结果如图4所示。从图4可以看出,仿真波形完全符合预期的设计需求。

图4 步进电机IP核的仿真结果Fig.4 Simulink waveform of stepper motor IP core

2 多轴控制器SoPC

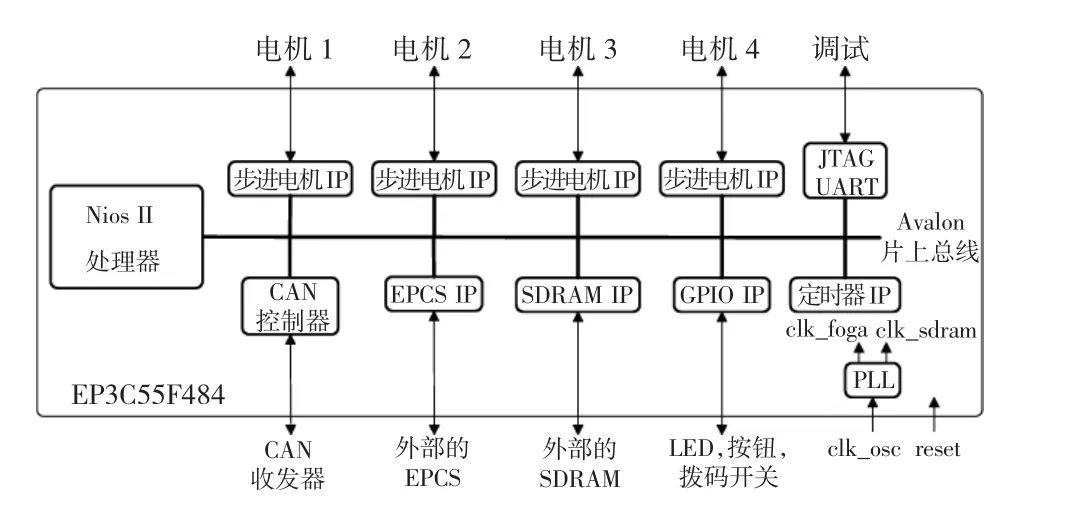

把所设计的步进电机IP核嵌入到复杂的SOPC系统中,从而可以构建多轴步进电机控制器。图5为4轴步进电机控制器SoPC系统框图,其系统功能模块包括:

1)NiosⅡ软核。它是Altera公司的第二代用户可配置的32位RISC软核处理器,是Altera公司特有的基于FPGA架构的软CPU内核。它提供有32位指令集、32位数据宽度和2GB寻址空间。NiosⅡ软核通过软件方式来完成运动轨迹的计算,并协调各个IP核的操作。

2)存储器控制器。EPCS用于存放FPGA的配置信息、软件代码和数据;SDRAM作为软件代码和数据的运行空间。

3)CAN控制器。它支持CAN2.0B协议,支持标准帧和扩展帧两种帧格式。这极大地扩展了通信能力,可用于与上位机的通信,接收控制参数以及用于调试和监测的目的。

4)4个步进电机IP核。每个IP核控制一台步进电机。该IP核具有Avalon总线接口,因此NiosⅡ处理器能够读写所有步进电机IP核内部的控制和数据寄存器。

5)为了实现整个数字系统,还需要包括有定时器IP核和JTAG UART IP核。为了控制时钟倍频、分频和同步,使用了一个PLL模块。

图5 4轴步进电机控制器SoPC系统框图Fig.5 Block diagram of 4 axis stepper motor controller SoPC

表2给出了整个数字系统在Altera公司的中等容量CycloneⅢ器件EP3C55F484上的执行结果。该SoPC系统消耗了大约23%的逻辑资源和18%的乘法器。若升级到8轴 SoPC系统,那么将消耗38%的逻辑资源和35%的乘法器,而最高运行频率将降到52MHz。

每个步进电机IP核消耗2 170个逻辑资源和13个9×9乘法器。因此,使用该型号FPGA,能容易升级到16轴甚至更多轴的步进电机控制器SoPC系统。

表2 4轴步进电机控制器的执行结果Table 2 Implementation results of the 4 axis controller SoPC

该多轴步进电机控制器的所有功能模块均以硬件描述语言进行描述,在源代码通过功能仿真后,再进行综合生成RTL网表,并经过工艺映射、布局、布线、时序分析、编程等,最后在Altera公司的FPGA芯片EP3C55F484中实现了四轴步进电机控制器SoPC系统,其时钟频率可以运行在50 MHz以上。

为了实现整个数字系统,设计了8层的FPGA控制板和4层的步进电机驱动板。FPGA控制板包括以下几个部分:FPGA芯片EP3C55F484,CAN 收发器 CTM8251,64Mbit的SDRAM芯片IS42S16400F,64Mbit的串行配置器件EPCS64。

步进电机驱动板主要实现步进电机的细分驱动功能,采用Allegro公司的专门针对两相步进电机而设计的步进电机驱动器A4982集成芯片。A4982是双全桥脉宽调制电机驱动器,片内两个H桥各自能提供高达2A的持续电流,工作电压高达35V。它可以驱动步进电机工作在全步、半步、1/4步以及1/16步模式下。

3 实验结果

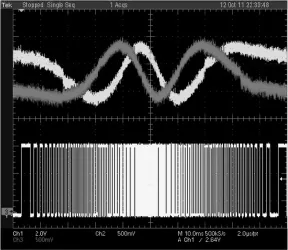

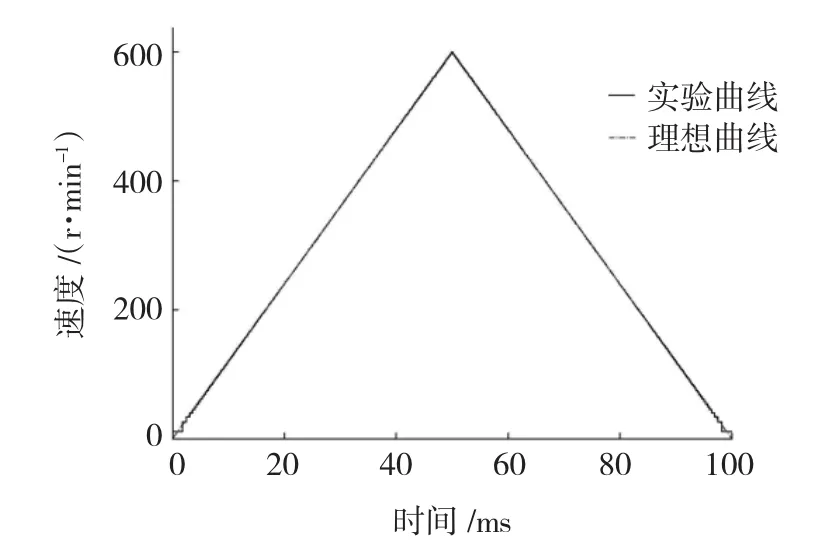

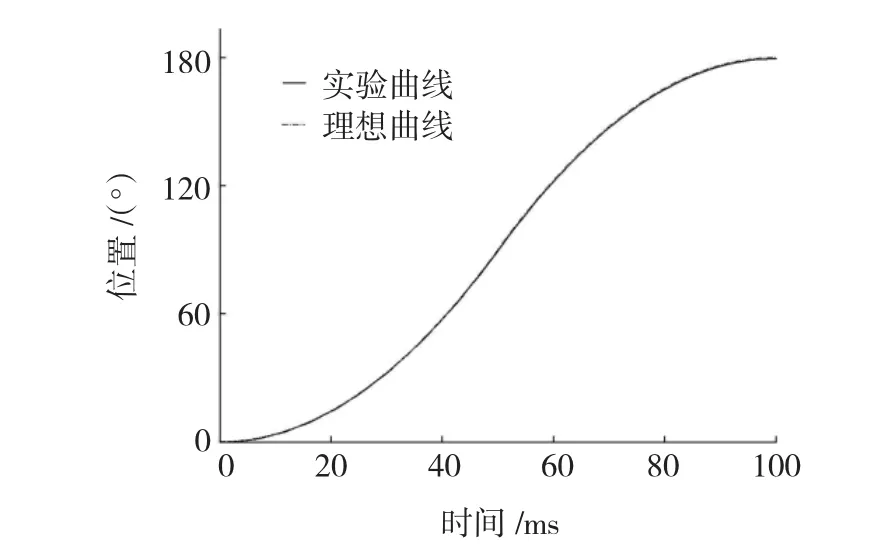

在测试伺服系统的控制性能实验中,驱动对象是4台相同的静转矩为0.09 N·m、额定电流为0.67 A、转动惯量为 9 ×10-7kg·m2、编码器线数为1 024的两相混合式步进电机。负载转动惯量约为3.3×10-6kg·m2,步进电机工作在1/16细分模式下。控制4台步进电机工作在三角形加减速模式下,其速度曲线参数均为:起动速度和停止速度均为0,匀速速度为2 560 step/s,加速步数和减速步数均为64 step,匀速步数为0。图6是电机控制器输出的其中一轴电机的脉冲信号和相应的绕组电流曲线。图7和图8分别是某次运动过程的速度曲线和位置曲线,实验结果与理想情况吻合得比较好,其最大误差在0.5%内。

图6 脉冲信号和电机绕组的电流曲线Fig.6 Pulse signal and winding current

图7 步进电机的速度曲线Fig.7 Velocity profile of stepper motor

图8 步进电机的位置曲线Fig.8 Position profile of stepper motor

4 结论

提出了一种应用FPGA实现多轴步进电机控制器的方法。开发了基于特定速度控制策略的高性能步进电机IP核,包括Avalon总线接口、位置检测、速度剖面生成、脉冲信号产生等算法模块。在此基础上,进一步集成了微处理器、存储器、通信模块等,构建了多轴步进电机控制器的SoPC系统。实验结果表明该多轴步进电机控制器具有良好的动态特性和稳态精确度。所设计的拥有自主知识产权的IP核通过了充分的软硬件仿真和实验测试,可以移植到不同工艺的FPGA平台中。

[1] ACARNLEY P.Stepping motors a guide to theory and practice[M].4th ed.London:The Institution of Electrical Engineers,2002.

[2] MASI A,CONTE G,LOSITO R,et al.DSP-based stepping motor drivers for the LHC collimators[J].IEEE Transactions on Nuclear Science,2008,55(1):341-348.

[3] 荣盘祥,张亚慧,张欢欢,等.基于DSP的运动控制卡的研究与开发[J].电机与控制学报,2011,15(3):35-39.

RONG Panxiang,ZHANG Yahui,ZHANG Huanhuan,et al.Research and development of multiple-axis motion control board based on DSP[J].Electric Machines and Control,2011,15(3):35-39.

[4] CHO Junguk,LE Quyngoc,JEON Jaewook.An FPGA-based multiple-axis motion control chip[J].IEEE Transactions on Industrial Electronics,2009,56(3):856-870.

[5] ASTARLOA A,LAZARO J,BIDARTE U,et al.FPGA technology for multi-axis control system[J].Mechatronics,2009,19(2):258-268.

[6] 周兆勇,王琳,漆亚梅,等.多轴伺服控制器的片上系统设计[J].电机与控制学报,2009,13(4):553-558.

ZHOU Zhaoyong,WANG Lin,QI Yamei,et al.System on chip design of multi-axis servo controller[J].Electric Machines and Control,2009,13(4):553 -558.

[7] WANG Bangji,LIU Qingxiang,ZHOU Lei,et al.Velocity profile algorithm realization on FPGA for stepper motor controller[C]//2011 2nd International Conference on Artificial Intelligence,Management Science and Electronic Commerce,August 8 -10,2011,Zhengzhou,China.2011:6072-6075.

[8] 陈国军,万明康,王大鸣,等.乘除法和开方运算的FPGA串行实现[J].微计算机信息,2008,24(5):167-168,192.

CHEN Guojun,WAN Mingkang,WANG Daming,et al.Serial implementation of multiplication,division and square root operation based on FPGA[J].Control& Automation,2008,24(5):167 -168,192.