基于Spartan3S400的LIN总线控制器IP核设计与车载应用

2012-07-03王琼,胡伟,夏光

王 琼,胡 伟,夏 光

(1.合肥工业大学 计算机与信息学院,安徽 合肥230009;2.合肥工业大学 汽车工程技术研究院,安徽 合肥230009)

随着现代汽车电子技术的发展,车身电子控制器件数目不断增加,整车控制系统的复杂度与生产成本不断提高,简化车载电子连接线束与降低汽车设计成本的要求促使副总线技术(LIN总线)应运而生。常见的LIN总线节点控制器是基于微控制器技术实现的,通过专属LIN总线收发器实现节点间数据通信。但是基于此技术设计的方案,其硬件成品体积较大,设计出的产品功耗值较高,同时,配套接口电路复杂,产品的后期深度应用与扩展受到局限。

本文提出一种基于FPGA芯片的LIN总线节点控制器IP核设计方法。基于FPGA技术的设计具有开发周期短、研发成本低的特点。另外,FPGA技术支持动态化下的可重构性应用,同时,大量已成熟的可应用FPGA资源,更便于广大汽车生产商将FPGA资源与其技术应用于最终产品上。

本设计基于Xilinx Spartan3S400芯片开发板,采用Verilog HDL设计语言进行设计功能描述,遵从LIN 2.0通信协议要求,最终实现片内可集成的LIN控制器IP核,将多个总线控制器IP核集成在单芯片内,实现单芯片下对多条LIN总线工作的控制。单功能核可实现总线主/从节点间信号收发、数据过滤、总线超时监测、帧结构的监测、ID位的校验、格式数据包提取、帧格式校验和计算等通信功能[1]。

在硬件实现方面,本设计方案很好地改善了传统芯片应用上的局限性,使车身控制网系统更加紧凑、稳定、可靠。采用的IP核设计技术在可缩放性、低功耗工作特点以及重构性等方面的优点,也是传统汽车硬件解决方案所不具备的。

1 基于Spartan3S400的LIN总线车身网络系统

1.1 Spartan3S400芯片性能

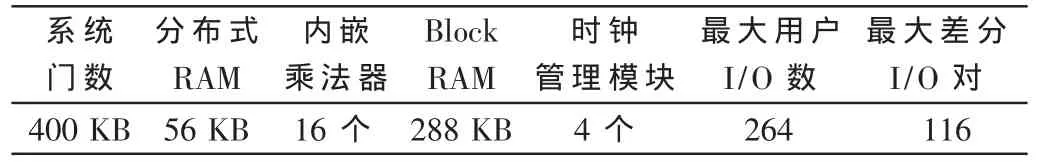

本设计选用赛灵思(Xilinx)公司的FPGA Spartan3-S400(IC SPARTAN-3 FPGA 400K 208-PQFP)芯片。 该款芯片具有低成本、强大的防克隆技术、低功耗等特性;芯片工艺在Spartan-ⅡE系列芯片设计工艺基础上,增加了逻辑设计单元、强化内RAM功能以及扩展I/O口;芯片还具有Virtex-Ⅱ架构内嵌硬乘法器和数字时钟管理模块。因此该芯片足以满足高容量设计需求。Spartan3S400芯片的特性如表1所示。

表1 Spartan3S400芯片特性

1.2 LIN总线车身网络拓扑结构

LIN总线技术广泛应用于车身非安全性节点间的组网[2],图 1为基于Spartan-3S400设计的LIN总线拓扑网络结构图,将多个具有LIN总线控制器功能的IP核集成在单一芯片内,实现车身主要非安全性节点的LIN总线控制,可改善因车身电子器件数目增加而带来硬件电路芯片数目过多的现状。

2 基于IP核的LIN总线控制器设计

系统设计思路:采用基于IP核的内嵌实现总线协议功能,有效缩短产品开发周期并大幅降低设计成本,通过对设计的内核参数进行修改调整,进一步对设计产品进行深度开发。

LIN控制器整体系统的设计分为:Spartan3S400芯片工作环境的硬件支撑部分设计、LIN总线通信协议的IP核软件部分设计与实现。

2.1 芯片工作环境硬件设计

Spartan3S400芯片的硬件电路设计主要包括电源管理模块、时钟、复位与下载调试接口几个部分。电源管理模块将5 V的Vcc转换为芯片工作时所需的内核电压(Vccin)1.2 V、Bank电压(Vcco)3.3 V和辅助电压(Vccau)2.5 V,设计采用 AS2830AT0812、AS2830AT3.30810和 AS2830-AT2.50920芯片依次进行电压值的转换,图2为3.3 V电压转换实现电路图[3]。

图2 3.3 V电压转换实现电路图

时钟源采用50 MHz外部时钟接入,下载调试接口采用XCF02S芯片配合Spartan3S400芯片进行PROMs方式下载,同时兼容JTAG方式下载。

2.2 LIN节点控制器IP核设计

控制器的软件设计采用自顶而下的设计思想,将控制器的功能划分为四大类:寄存器管理模块、时钟管理模块、收(发)转移寄存器模块和状态(收/发)模块[4]。在功能的整体实现过程,将底层子功能模块设计为:checksum_generator、configuration_registers、frame_state_machine、divider、majority_sampler、parity_generator、receiver和 transmitter,最后再经由顶层设计模块lin_module将各个子功能模块整合。开发工具是基于ISE的软件设计平台与CORE Generator的IP核设计平台,图3为控制器模块功能结构框图。

2.2.1 寄存器管理模块设计

在控制器管理模块设计中定义了不同功能的寄存器子模块,通过对寄存器的操作实现不同的控制功能。外界MCU通过对寄存器的读、写操作,实现寄存器数据的清除或设置,从而实现对LIN控制器的控制和状态检测。表2为寄存器配置模块中控制位的设置。

2.2.2 时钟管理模块设计

设计中引入一个除数因子divisor,设定divisor满足式(1),其中 CLK是外部给定的 50 MHz时钟,除数因子的高位存储在寄存器CLKDIV1中,除数因子的低位存储在寄存器CLKDIV2中。本次串口传输速率为9 600 b/s,根据公式可得出:divisor=(50 000 000/16)×9 600=(325)10=(0145)16,所以,设置时钟寄存器CLKDIV1=(01)16和CLKDIV2=(45)16。计算所得内部时钟再16分频形成一个新的“bitclk”时钟信号,以供接收模块端使用,接收模块端使用16倍于发送模块端的时钟信号,同时,接收计数器cnt=8时插入抽样分析点,抽样点在每位数据脉冲的中点位置,可提高抽样分析数值的准确性。

2.2.3 帧状态管理模块设计

该模块设计目的是通过对各种寄存器的设置来控制总线上所有位时序操作。由两部分组成:主机节点工作进程和从机节点工作进程。主机任务负责报文的调度表和发送正确帧头,并按照调度表维护帧间的正确时间间隔,在满足发送条件时,主机节点依次发送间隔场、同步场和标识符场[3],从机节点提供帧响应。主机节点软件流程图如图4所示。

表2 控制位的设置

2.2.4 收/发模块设计

将采集到的经驾驶员操作按键而产生的开关信号传至发送端帧处理模块,对信号进行总线相应传输数据格式处理,处理后的信号数据发送至总线上传输。通对接收端接口扫描,可检测总线信号变化,对总线上信号接收并对接收帧分析,正确接收到的数据信息送至相应寄存器模块处理。发送与接收模块是对外交流的窗口,在这两个功能模块中体现了LIN2.0协议传输中的接收与发送要求[4]。

图4 主机节点软件设计流程图

3 测试实验与结果分析

将设计完成的软件系统进行产品前测试[5],测试主要针对LIN2.0协议内容与功能实现的验证。测试实验分为两部分:(1)单节点功能测试,包括单节点对数据信号的接收与回弹反馈验证;(2)节点间组网通信测试,包括一个节点A(模拟总线主节点)对另一个节点B(模拟总线任一从节点)信号的发送与接收。因本次设计不涉及到其他数据信号的冲突,所以测试中不包含对外来信号的冲突纠错处理,也不针对总线平均负载与总线峰值负载方面的测试。

3.1 单节点测试

LIN的传输格式是基于UART的工作原理延伸而来的,基于FPGA的UART功能测试仿真图如图5所示。

单节点工作性能的测试实验在仿真软件Model-sim6.4b版本下进行,将通过XST后的lin.ise工程源文件lin.v与另外编写的测试程序 lin_test_testbench.v,经仿真软件编译后形成测试仿真波形,图6所示为lin_test测试的时序仿真图。

测试结果表明[6],总线上节点工作状况符合LIN总线协议要求。

3.2 两节点间通信测试

测试模块是利用Verilog HDL语言编写,测试架构包含两个节点的LIN总线通信,测试内容包括对发送寄存器的写、等待中断和响应中断操作,以及对接收寄存器的读取和寄存器的检查。部分子程序如下:

write_register1(REG_TRANSMIT,x”10”);

wait until(int2=’1’and int=’1’);

read_register1(REG_RECEIVE,date_read1);

read_register2(REG_RECEIVE,date_read2);

测试中通过对接收端的继电器工作吸合状态判定信号的传输与节点的正确接收。

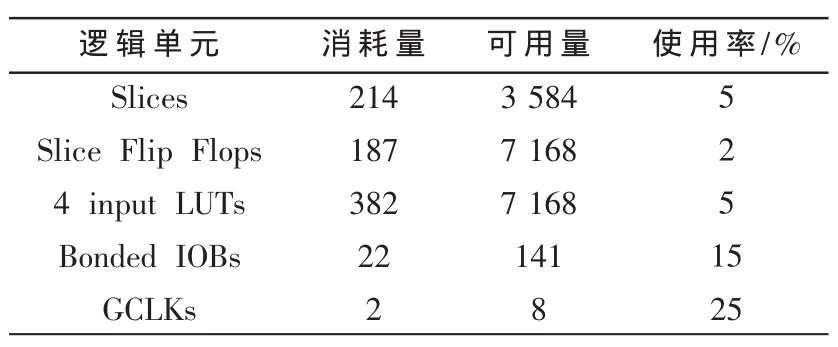

对单节点和两节点间通信测试结果的分析表明,此设计是合理的,总线上节点的设计满足LIN总线传输协议要求。ISE生成的片内资源占用情况如表3所示。

本文将FPGA设计技术与汽车LIN总线应用技术结合,提出了基于LIN总线控制器IP核实现LIN 2.0总线协议传输的方案,为IP技术的产品化以及产品在车载电器通信网络上的应用奠定了基础。经测试,系统运行稳定可靠,与使用通用单片机设计相比,本设计占用硬件资源少,硬件电路体积小,成本和产品功耗以及集成度方面都有明显改善。在未来能源车上将会有更广阔的应用空间。

表3 片内资源利用

[1]LIN Specification Package-revision 2.0.[2003-09-23].http://www.linsubbus.org.

[2]汪淼.基于LIN总线的车身控制系统设计[J].合肥工业大学学报(自然科学版),2009,32:93-96.

[3]Li Hongqiang,Miao Changyun,Wang Huaping.An integrated approach to car body control using SoPC technology[C].International Conference on Computer Science and Information Technology 2008:259-263.

[4]DESHPANDE A.Verification of IP-core based SoC’s[C].9thInternational Symposium on Quality Electronic Design,2008:433-436.

[5]黄锐,宋强.LIN总线控制器的关键技术研究与实现.航空计算技术,2007,37(1):114-116.

[6]DAS S R,HOSSAIN A,LI J F.Further studies on improved test efficiency in cores-based System-on-Chips using modelSim verification tool[C].Instrumentation and Measurement Technology Conference,2009(I2MTC′09.IEEE):1132-1137.