高速信号完整性分析及设计在继电保护装置中的应用

2012-07-03甘云华周华良汪世平邹志杨

甘云华,周华良,夏 雨,汪世平,邹志杨

(国网电力科学研究院/南京南瑞集团公司,江苏 南京 210003)

特高压输电技术以及智能电网技术的发展必然要求有先进的智能保护装置来支撑[1-3]。近年来,在国家电网公司特高压输电项目的带动下,继电保护技术的发展不断加速,继电保护与现代控制理论、电力电子技术和远程通信技术的结合日益密切[4-6],这些新的应用使得继电保护设备的主CPU工作时钟频率不断提高,外设接口不断丰富,系统集成度和布线密度不断加大。对硬件设计工程师来说,在继电保护装置研发过程中,传统的电路设计方法不再适用,而仅仅依靠经验来完成设计已不足以保证产品的合格率和可靠性,信号线的信号质量将成为产品硬件设计能否成功的关键。因此,要提高装置研发的效率和产品的可靠性,进而提高系统硬件研发的一次成功率,必须在板级设计阶段对系统关键信号进行详细的分析与设计。文中所述的高速信号完整性分析及设计方法已在ARP-300系列高压继电保护装置研发过程中实际使用,并在项目的高效快速研发中发挥了重要的作用。

1 装置的系统组成

ARP-300系列高压继电保护装置核心CPU板由高性能的CPU和数字信号处理器 (DSP)组成,CPU实现保护装置的总启动元件和人机界面及后台通信功能,DSP完成所有的保护算法和逻辑功能。保护装置采样率为每周波24点,在每个采样点对所有保护算法和逻辑进行并行实时计算,使得装置具有很高的固有可靠性及安全性。系统采用的关键芯片及资源有:

(1)CPU芯片采用Freescale公司的带协处理器功能的高性能PowerPC 【MPC8321】,系统主频333 MHz,片外RAM使用 DDR2内存【DDR2时钟为266 MHz】,同时支持3个独立MAC的100 Mbps以太网接口;

(2)DSP芯片采用 ADI公司的高性能浮点DSP 【ADSP21469】,系统主频 400 MHz,内置 5 MbitsSRAM,片外RAM使用DDR2内存【DDR2时钟为 200 MHz】。

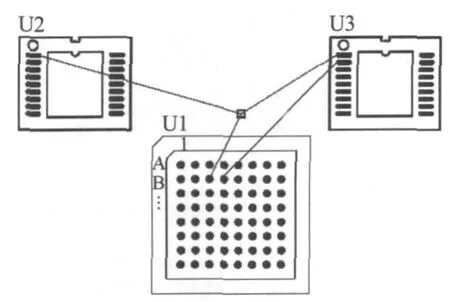

系统结构如图1所,系统以CPU和DSP芯片为核心,两处理器均有扩展外部DDR2高速存储器,数据线和地址线的布线密度大,时钟信号速率高;CPU扩展的3路以太网接口信号采用差分对走线,对线路阻抗控制有特殊要求。如果在硬件设计初期对这些问题处理不当,就会引发信号失真,导致多种错误的发生,造成系统达不到预期的设计效果甚至部分模块无法正常工作。解决这一问题比较有效的方法就是对系统进行信号完整性设计。

2 信号完整性设计

2.1 信号完整性

信号完整性是指信号线上的信号质量。通常,数字逻辑电路的频率达到或者超过50 MHz,而且工作在这个频率之上的电路占整个系统的1/3以上,就可以称其为高速电路[7]。在高速电路设计中,信号完整性对系统的影响主要体现在:时序裕量是系统在高低温下稳定运行的保障之一;电平裕量对于电路的电磁干扰的抗扰度有保障;减小信号回路面积大大削弱了信号环路的天线效应,一方面提高了电路对高频电磁场的抗扰度,同时也降低了电路对外发射的强度。影响信号完整性的因素主要包括反射、串扰、延时等。在高速电路设计中,随着时钟频率提高,信号边沿变陡,信号在器件之间的同步时间就会缩短,要满足所有门延时必须在越来越短的时间预算中实现,稍有不慎都可能导致器件时序或模块功能的混乱。

图1 系统结构

产生上述信号完整性问题的主要原因包括信号走线过长、总线结构走线之间不等长、信号走线安全间距不够以及信号传输路径上的阻抗不匹配等。通过对系统进行信号完整性分析与仿真,可以对相邻平行信号线进行耦合分析,确定信号线之间的安全预期间距或平行布线长度,减小串扰对信号造成的危害。另外通过对不同匹配电阻的扫描分析对比,可以寻求信号传输路径上阻抗端接匹配的最优化,抑制反射现象的发生。阻抗匹配是解决大部分信号完整性问题的重要手段,所以有必要介绍一下传输线的特征阻抗。

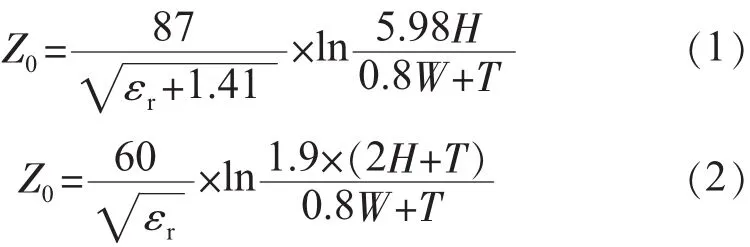

2.2 特征阻抗

高速电路设计中,信号走线的分布参数效应使其寄生电感和寄生电容不能被忽略,必须将信号走线当作传输线来处理。特征阻抗是传输线的一个重要特性[8]。传输线主要有2种形式:微带线和带状线,其中微带线分为表面微带线和嵌入式微带线,带状线分为对称带状线和不对称带状线。典型的表面微带线和对称带状线的特征阻抗Z0的近似计算公式分别如式(1)和(2)所示[9]:

式中:εr为绝缘介质介电常数;H为导线至参考平面之间的介质厚度;W为导线宽度;T为导线厚度。在选定基材后,εr变化很小,板厚和层压工艺决定H变化,T由铜箔厚度和加工工艺确定。由此可见,控制调整线宽是设计人员控制Z0最直接和最有效的方法。

传输线的Z0与印制板层叠设计密切相关。本文设计的CPU板对特征阻抗参数进行了理论计算,同时结合PCB加工厂家的工艺加工能力,确定采用8层结构板,并采用了如图2所示的叠层设计。

图2 PCB叠层结构

该系统中CPU主频为333 MHz,DSP芯片主频为400 MHz,片外RAM使用DDR2内存,DDR2时钟频率达到200 MHz及以上,时钟信号的质量直接影响整个系统的性能,因此时钟信号走线长度的控制、与相邻信号之间的干扰以及信号传输路径上的阻抗匹配是系统分析设计的重点;同时DDR2的地址线和数据线由于时序要求严格,需要控制网络之间的安全间距和数据组间等长,但由于系统布线密度较大,需综合考虑空间和信号完整性问题。另外系统扩展有3个独立MAC的100 Mbps以太网接口,采用差分对走线方式,对其进行阻抗控制以及等长匹配也是系统设计的关键。如对上述问题处理不当,容易造成信号传输路径上阻抗失配,引起反射、不同网络之间相互干扰和电路误触发或时序混乱,降低信号传输的质量,影响系统性能,导致系统无法正常工作。该系统中最为关键的信号处理点就是以上所述CPU和DSP的外部存储器DDR2以及高速以太网差分对的处理,下面就针对这2个关键点做具体的分析和设计。

3 关键信号分析

3.1 DDR2时钟信号线

系统中CPU和DSP均有扩展外部DDR2高速存储器,由于两者具有一定的共性,文中仅以DSP(ADSP21469)和 DDR2(MT47H64M16)连接为例进行分析。MT47H64M16芯片时钟信号由ADSP21469提供,由于信号速率较高,考虑表层布线,并采用抗干扰能力较强的差分对形式走线,信号拓扑结构如图3所示,TL_MS表示差分传输线,微带线结构,R1和R2为源端匹配电阻。

图3 时钟信号拓扑图

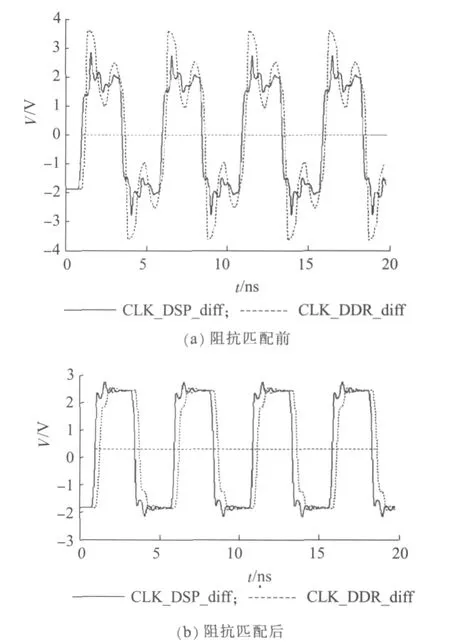

采用Cadence软件信号完整性分析模块,调入ADSP21469和MT47H64M16的IBIS行为级模型后,整体提取差分对网络拓扑结构在SigXplorer环境下进行仿真。采用图2的叠层设计,参考差分线阻抗为100 Ω控制要求,差分微带线结构中线宽为5.5 mil,线间距11 mil。采用点对点无匹配连接的情况下,在源端施加200 MHz周期激励,仿真波形如图4(a)所示,信号存在较严重的变形,这是由于信号在传输路径上的阻抗不连续点发生反射造成的,因此必须考虑在电路设计过程中加入匹配电阻。设计中采用在源端串接电阻的匹配方式,施加相同的激励源后仿真波形如图4(b)所示,信号传输延时227 ps,传输速度约为0.56倍光速。由仿真结果可知串接匹配电阻后,信号得到明显改善。通过使用软件sweep功能对不同匹配电阻进行扫描优化,可以确定电路中的较优匹配阻值,该仿真案例中匹配电阻在40 Ω左右,信号波形达到设计要求,实际电路中考虑电阻标称值,采用33 Ω匹配电阻。

3.2 以太网差分信号线

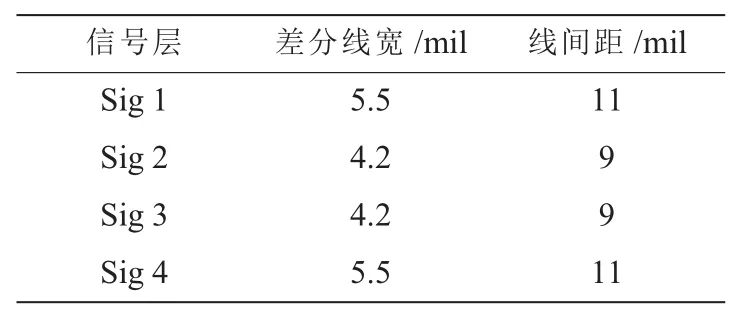

系统主要采用以太网接口与外部实现通信,以太网接口芯片为Broadcom公司的BCM5241,信号主要以差分对形式进行传输。差分线作为传输高速信号的有效载体,对其进行阻抗控制和匹配非常关键。根据系统差分线阻抗为100 Ω的控制要求,参照文中2.2节的叠层设计,计算得各信号层差分信号布线要求,如表1所示。

图4 时钟信号波形

表1 差分信号布线规则

差分线阻抗控制的一致性可以保证信号在传输过程中不易发生失真变形,但仅通过设置合适的布线宽度和线间距还不足以保证阻抗的连续性,从3.1节的分析中得知,必须在传输路径上对信号进行正确的端接匹配,以达到抑制或消除信号反射的目的。此外差分对的正负两端应尽量做到等长以抑制共模干扰。综合器件指导手册、阻抗设计要求及经验规则,对以太网接口差分的确认采用如下布线规则:(1)线宽/线间距为5.5 mil/11 mil(PCB板外层);(2)差分对两根走线等长误差为<25 mil。

按上述规则指导完成布线后,还可能存在一些信号完整性问题,如端接电阻阻值匹配不够理想,信号之间的串扰等。通过布线后仿真可对设计进行优化,做到使整个设计的信号完整性问题减到最少。

3.3 DDR2数据与地址总线

由以上分析可知,DDR2的数据和地址总线布线同样需要进行阻抗控制和匹配,除此以外,由于CPU和DSP对DDR2进行读写操作时,对各信号的时序要求比较严格,因此在设计中对不同信号的走线长度要进行控制。通常总线各位数据线需进行等长匹配设置,而为了避免信号反射等问题进行的端接匹配会使高速总线被电阻等无源器件分成好几段Net,这时等长控制最原始的做法就是对每段进行控制,比较繁琐。Cadence公司Allegro软件中解决这个问题的办法就是借助Xnet这一概念,即把连续的几段由无源器件连接的Net合称为一段Xnet,如图5所示。

图5 Xnet示意图

通过赋予无源器件ESpice模型,Net1、Net2和Net3会自动合成为1个Xnet,这样在软件的规则约束管理器中设置等长规则时只需对整个Xnet设置规则,无需对每一小段进行等长匹配处理。

总线的等长匹配有2种,分别为全局等长和局部等长。如图6所示。

图6 等长示意图

图中U1.B3到U3.1和U1.B4到U3.2的走线设置等长属于全局等长,一般数据总线或地址总线的不同位之间的走线等长属于这种形式。另外图6中T型连接点到U2.1和U3.1的走线设置等长属于局部等长,对于多片存储器共享数据和地址总线时属于这种形式,这种等长的设置和网络的拓扑结构有关。为避免传输线效应,减小信号组之间的串扰,走线应尽可能短,同时还要兼顾各信号之间的时序要求。综合考虑布线空间和信号质量,该系统中数据和地址总线布线要求如下:

(1)数据和地址线单线总长度控制在2000 mil以内;

(2)内层线宽 4.6 mil,外层线宽 6.8 mil,总线组内部间距>6 mil,总线组与其他走线之间的间距为>20 mil;

(3)总线之间等长误差<20 mil。

规则设置以后,对于等长的控制可以使用Allegro软件的蛇形走线工具,根据实时显示的走线长度确保总线等长匹配的精确性。布线完成后同样需要进行后仿真,通过分析仿真结果对一些规则进行优化,以使系统满足设计要求。

4 实际电路测试

根据上述的设计规则制作了CPU板的印制电路板和样机,并进行了实际测试。对单板通过Agilent Technologies公司的MSO7104A混合信号示波器进行测试,测得与ADSP21469相连的MT47H64M16时钟信号波形如图7所示。信号波形无振荡,上升时间为0.66 ns左右,满足CPU及DDR2的系统工作要求,CPU和DSP的DDR2内存均能正常稳定工作,进一步验证了设计前信号完整性分析与仿真的正确性和有效性。

图7 时钟信号波形

同时,基于此CPU板的保护整装置在国网电力科学研究院进行了多项试验,均按照最高级指标要求进行,主要针对性的测试项目包括:

(1)高温试验, 按 GB/T 2423.2—2001(IEC 60068-2-2:1974)标准,+55 ℃下 16 h;

(2)低温试验, 按 GB/T 2423.1—2001(IEC 60068-2-1:1990)标准,-25 ℃下 16 h;

(3)快速瞬变干扰试验,按GB/T 14598.10—2007(IEC 60255-22-4)标准 IV 级,电源、开入开出、交流:4kV,2.5 kHz,5/50 ns;通信端子:2kV,5 kHz,5/50 ns;

(4)电磁发射试验,按GB/T 14598.16—2002(GB 9254-2008、CISPR 22:2006)标准,B 级辐射骚扰限值,30~230 MHz准峰值 30dB(μV/m),230~1000 MHz准峰值 37dB(μV/m);

(5)静电放电试验,按GB/T14598.14—1998(IEC60255-22-2)标准 IV 级,接触放电:8kV,空气放电:15kV。

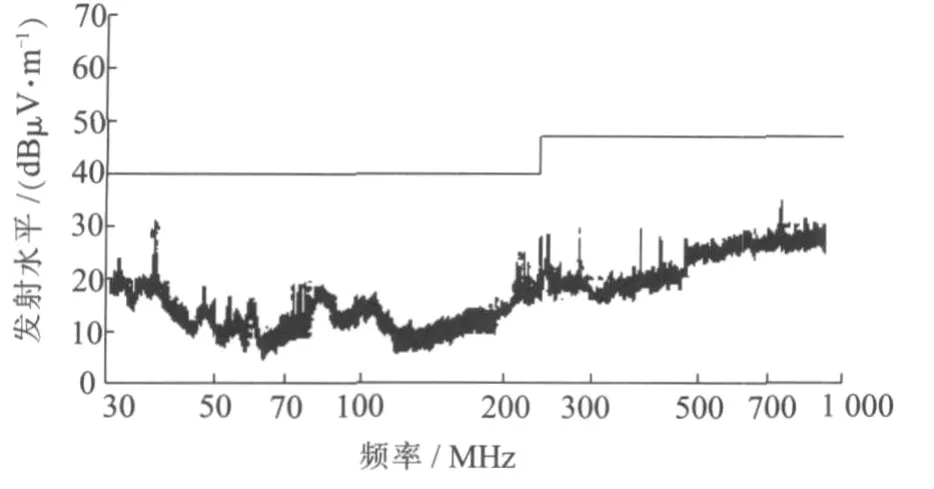

在整个试验测试过程中,CPU和DSP的DDR2内存均可靠工作,以太网口可靠通信,装置运行稳定。此外,装置完成的电磁发射试验,按GB/T 14598.16—2002 (GB 9254—2008、CISPR 22:2006)B级辐射骚扰限值进行,测试曲线如图8所示,结果如表2所示。该指标满足国外工程需求,进一步证明了在系统硬件设计阶段进行信号完整性分析与设计的正确性和可行性。

图8 电磁发射测试曲线

表2 电磁发射测试结果

5 结束语

针对电力系统保护装置发展过程中,系统芯片工作频率的不断提高和信号边沿的不断缩短等带来的问题,以新一代高压继电保护ARP-300系列装置硬件设计为平台,提出在硬件板级设计阶段引入高速信号完整性分析与设计方法,通过信号完整性分析指导器件布局、布线规则设置和阻抗匹配等。实际板卡的信号完整性测试结果表明,系统反射、串扰等信号完整性问题得到了有效控制,证明文中应用的高速信号完整性分析与设计方法正确,设计规则合理有效;同时对含有该CPU板的整装置进行了电磁兼容实验,系统可靠工作,进一步验证了该设计方法的正确性和可靠性。最后需要说明的是,高速信号完整性分析内容较深,本文仅对继电保护装置硬件研发过程中的信号完整性问题做了初步的探讨,对信号完整性分析与设计还有很多新方法及技巧有待今后进一步深入研究。

[1]陈德树,唐 萃,尹项根,等.特高压交流输电继电保护及相关问题[J].继电器,2007,35(5):1-3.

[2]刘成君,张恺凯.数字化变电站及其对继电保护的影响[J].电工电气,2010(4):4-7.

[3]邵宝珠,王优胤,宋 丹.智能电网对继电保护发展的影响[J].东北电力技术,2010(2):11-13.

[4]徐 政,卢 强.电力电子技术在电力系统中的应用[J].电工技术学报,2004,19(8):23-27.

[5]李峥峰,杨曙年,喻道远,等.继电保护中光纤通信技术应用[J].电力自动化设备,2007,27(2):75-79.

[6]刘 青,王增平,郑振华.基于MAS的含FACTS元件输电线路自适应协调配合方案的研究[J].华北电力大学学报,2009,36(1):15-19.

[7]周润景,袁伟亭.Cadence高速电路板设计与仿真[M].北京:电子工业出版社,2006.

[8]BOGATIN E.信号完整性分析[M].李玉山,李丽平,等译.北京:电子工业出版社,2005.

[9]IPC-2251,Design Guide for the Packaging of High Speed Electronic Circuits[S].2003.