自适应有限冲激响应滤波器的FPGA实现

2012-06-28王雷,李静

王 雷,李 静

(1.解放军92785部队,秦皇岛066200;2.北京航天科奥电子技术有限公司,北京100070)

0 引 言

自适应滤波器一直是信号处理领域的研究热点之一,并已经被广泛应用于数字通信、回波消除、天线阵波束形成、信道均衡等领域[1]。自适应滤波器是一种具有自我调整能力和跟踪能力的现代滤波器,可根据被控制对象的时变性做出相应的调整,满足某种准则的要求,从而实现最优滤波。同时,现代数字信号处理更趋向于高速、实时的信号处理。它需要极高的数据吞吐量和巨大的实时计算量。FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算的通用数字信号处理器(DSP)芯片,其并行性和可扩展性更好,在实时性要求较高的场合更能满足系统高速、实时的需要[2]。本文针对FPGA的特点设计了一种自适应有限冲激响应(FIR)滤波器的实现方法,并通过在Xilinx公司提供的ISE平台上采用Verilog HDL编程[3],利用 Modelsim 和 Matlab软件对双模式盲自适应均衡滤波器[4]进行仿真验证。

1 FIR滤波器原理

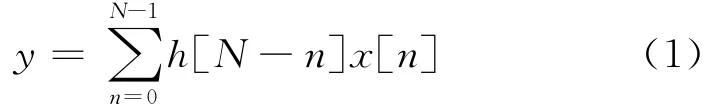

FIR滤波器的基本结构就像一个分节的延时线,将各节的输出加权累加,得到滤波器输出。其数学差分表达式为:

式中:xb[n]为在n时刻采样信号x[n]的第b位。

将式(2)代入滤波器的输出表达式(1),可得到:

假设滤波器的输入信号x[n]为B+1位补码形式,即:

对于式(3)中乘积项xb[n]h[N-n],当xb[n]为1时,其值为h[N-n];当xb[n]为0时,其值为0。由此可知,对于式(4)每个括号中的子式,N 位向量 (xb[0],xb[1],…,xb[N -1])有2N种情况,相应地有2N种组合值。

对于传统的固定系数的FIR滤波器,为了提高系统的运行速度,有人提出了一种分布式算法[5]。分布式算法(DA)是一种以实现乘加运算为目的的运算方法。它与传统实现乘加运算算法的不同之处在于:执行部分积运算的先后顺序不同。

该算法事先构造一个查找表,其中存储了上式括号中所有可能的组合值,并通过所有输入变量相对应的组合向量 (xb[0],…,xb[N-2],xb[N-1])对该表进行寻址。DA算法的特点是巧妙地运用查找表将固定系数的乘累加(MAC)运算转化为查表操作。但是,由于查找表在FPGA上实现需占据大量的逻辑资源,当设计的系统较大时,需要采用更大容量的FPGA。同时,分布式算法一般应用在传统的系数固定的滤波器中,自适应滤波器不象传统的固定系数滤波器,它的抽头系数是不断向着最优系数调整的,因此不可以将权系数的各种组合提前计算好并存储起来。本文依据分布式算法,研究了一种可用于自适应滤波器的FPGA实现方法。

2 自适应FIR滤波器的FPGA实现

滤波器的实质就是实现一个乘累加运算,而滤波器的阶数决定了乘累加运算的次数。因此,滤波器的FPGA实现主要是利用一些乘法器和加法器。为了实现高速自适应FIR滤波器的设计,可以采用Xilinx FPGA的硬核DSP48单元来实现乘加运算。每个DSP48模块含有一个18位×18位的有符号硬核乘法器,在乘法器后面级联了具有3个输入端口的硬核加法器及若干可选流水线寄存器。

虽然采用DSP48可以提高速度且占用较少Slice,但是在一些低端的FPGA 器件(如Spartan2E)中,其内部无内嵌的硬核乘法器DSP48。当调用IP核实现乘法器时,其实现方法只能用LUT查找表结构,因此有必要设计一种高效的自适应滤波器FPGA实现方法[6]。

本文设定自适应FIR滤波器的输入数据位宽为8位,权系数(w0,w1,…,w6)位宽为24位,输出数据位宽截取为8位,所有数据均是用二进制补码表示的有符号数。将自适应FIR滤波器划分为并/串转换模块、数据延迟模块、权系数组合模块和移位相加模块,其结构框图如图1所示。

图1 自适应FIR滤波器FPGA实现模块框图

数据延迟模块——将输入滤波器数据x[n]通过不同的触发器组完成N阶延时,产生与各个抽头对应的延时信号 (x[n],x[n-1],…,x[n- N +1])。

并/串转换模块——对经过数据延迟模块的各数据延时信号同时进行从并行到串行的处理,为后续电路做准备。该模块输出信号为各延时信号相对应位组成的N 位向量 (xb[n],xb[n-1],…,xb[n-N+1])。对于一些复杂的自适应均衡器系统,考虑FPGA内部逻辑有限,本文设计的整个电路以串行方式工作,然而输入数据是并行的,所以,必须将输入数据进行并/串转换处理。若数据延迟模块的并行输入数据为B位,则该模块要相继输出B组这样的向量后,数据延迟模块才能输入一个数据。

因此,数据延迟模块以信号速率采入B位数据(包括一个符号位),则并/串转换模块要以B×信号速率的时钟频率工作,这样就需要实现倍频。在处理高速信号时,该模块就需要更高频率的工作时钟。工作频率过高时,对于时序数字系统设计会出现不可预测的毛刺和干扰。因此在一些需要处理高速信号的场合,在FPGA资源足够的情况下,可以采用并行方式来实现,而不再需要并/串转换。

权系数组合模块——根据并/串转换模块输出的向量 (xb[n],xb[n-1],…,xb[n-N+1])完成相对应的权系数相加组合。权系数组合模块实际上是由多个用于存储权系数的双端口随机处理器(DPRAM)和控制各DPRAM正确工作的控制模块组成的,为了节省大量的逻辑资源,在设计中利用了Xilinx FPGA内部的块随机处理器(RAM)。

自适应均衡器系数更新模块输出的更新权系数后面加入了多个RAM来存储权系数。对于7阶FIR滤波器的7个24位权系数可有27种组合,这就需要24×27的RAM。为了减小RAM的存储规模,在每2个权系数后面加入1个24×8的DPRAM。同时将RAM分成A、B 2个区,前4个存储单元为A区,后4个存储单元为B区。其功能框图如图2所示,以w0和w1后面的RAM0为例来说明其工作过程。

图2 DPRAM功能框图

在RAM0中,A、B 2个区的第1个存储单元均存储24bit 0,第2个存储单元存w0,第3个存储单元存w1,第4个存储单元存入w0与w1的和值。另外通过一个state信号来决定A、B区的读和写操作。当state=0时,A区进行写操作,同时RAM的A端口写地址最高位为0;B区进行读操作,同时RAM的B端口读地址最高位为1。当state=1时,A区进行读操作,且B端口读地址最高位变为0;B区进行写操作,且A端口写地址的最高位变为1。通过state信号控制读写操作在A、B区交替进行,类似于乒乓操作。RAM0的3位读地址是由state信号和权系数组合模块输入信号 (xb[n],xb[n-1],…,xb[n- N +1])中 相 邻 的 2 位 (xb[n],xb[n-1])来 共 同 决 定 的。 其 中 (xb[n],xb[n -1])与w0和w1的4种组合值的对应关系及相对应的RAM读地址如表1所示。对于RAM0的写操作,只需要保证在8个时钟周期内(本中滤波器输入信号为8位)将同一时刻的w0,w1和w0+w1写入RAM0的对应存储单元即可。

表1 (xb[n],xb[n-1])与w0 和w1 的4种组合值及读地址的对应关系

所有DPRAM读出的数据再经过相加就得到与滤波器输入数据中的1位(xb[n])相对应的一种权系数的组合值。在经过B次循环后,就得到了与滤波器输入数据所有位 (xB-1[n],xB-2,…,x0[n])对应的权系数组合值。

移位相加模块——将系数组合模块输出的B个权系数组合值经过相应的二次幂加权后再相加得到最后的滤波器输出结果yn。在该模块中,要对权系数组合模块输出的值进行二次幂加权处理,其通过左移位运算完成。为了提高系统运行速度,B个数值的相加不采用传统的累加器,而采用加法树的形式实现。这样可以将移位运算分解成多层次的移位,进而可减小加法器的位数,起到节省FPGA资源的作用。对于B位的滤波器输入信号,当b<B-1做加法运算,当b=B-1时做减法运算。因此,经B-2次加法和1次减法,就完成了对yn的计算。

此外,为了提高整个自适应FIR滤波器模块的运行速度,在该模块中引入流水线技术。流水线技术为高速数字系统的实现提供了一种非常经济有效的方法。该技术将一个完整的操作分为若干子操作,这些子操作可以在时间上同时进行而互不干扰。流水线技术的引入可以在不增加或尽可能少增加硬件资源的条件下,实现高速信号处理。

3 自适应FIR滤波器FPGA仿真实现

为了验证本文方法的正确性,结合双模式(修正恒模算法(MCMA)+判别算法(DD))自适应盲均算法构造的自适应滤波器,设定输入自适应滤波器的信号为通过信道模型h=[0.763 1-j0.505 4,0.256 7+j0.271 4,-0.134 3-j0.016,0.059 2-j0.006,-0.026 7+j0.004 8,0.009 8+j0.001 5][7],并加入白噪声的16位正交调制(QAM)信号,滤波器的抽头数为7,FPGA的时钟周期为50MHz,分别应用Matlab和FPGA进行仿真。FPGA采用Xilinx公司的Virtex4中的Xc4vlx25芯片,在ISE9.1i的FPGA集成开发环境下使用硬件描述语言Verilog HDL进行设计,并且使用Modelsim SE 6.2b软件进行系统仿真,可以得到自适应均衡滤波器均衡后系统的均方误差效果图,如图3所示。

图3 双模式盲均衡器系统功能仿真图

由图3所示的仿真结果可以看出,图3(a)的Matlab仿真图和图3(b)的Modelsim仿真结果基本一致,因此,可以证明上面设计的自适应FIR滤波器的实现方法是可行的。整个程序是在ISE9.1i平台上实现的,设计中自适应FIR滤波器信号输入是8位,权系数为24位,输出也为8位,整个程序综合于Xilinx公司的virtex4系列Xc4vlx25芯片上,其中上述双模式均衡器中的FIR滤波器采用了并行结构,其使用资源为:3 195个Slices,占29%,3 248个4输入LUT,占15%,32个RAMB16s,占44%,其时钟频率可达到316.811MHz。若要考虑节省资源,可采用串行结构实现,其使用资源为:581个Slices,占5%,642个4输入LUT,占2%,1个RAMB16s,占1%,时钟频率可达到212.316MHz。

4 结束语

本文研究了一种自适应有限脉冲响应滤波器的FPGA实现方法。该方法将原来的乘累加运算转化为只有加法和移位运算,相应的FPGA实现也由传统的乘法器(DSP48)和加法器转变为加法器和DPRAM,可以节省FPGA中的硬核乘法器。该方法用FPGA内部的块RAM来存储权系数辅助完成乘累加运算,由于块RAM不占用内部逻辑资源,所以相对于查找表该方法可以节省大量的逻辑资源。另外,在移位相加时通过将移位分为多层移位减小了加法器的位数,同时结合使用流水线技术,保证了系统运行的速度,最后通过Modelsim仿真和Matlab仿真结果比较验证了该设计方法是可行的。

[1]Simon Haykin.自适应滤波器原理[M].郑宝玉译.北京:电子工业出版社,2010.

[2]杨恒.FPGA/CPLD最新实用技术指南[M].北京:清华大学出版社,2005.

[3]田耘,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008.

[4]潘立军,刘泽民.两种改进的盲均衡算法[J].电路与系统学报,2006,11(2):141-144.

[5]郭继昌,李香萍,滕建辅.基于位串行分布式算法和FPGA实现FIR电路的研究[J].电子测量与仪器学报,2001,15(2):15-21.

[6]Dawood A,Bergmann N,Asdani Z,et al.Adaptive FIR filter design and implementation empowered by reconfigurable FPGAs[J].Proceedings of SPIE-The International Society for Optical Engineering,2000,67(3):1601-1612.

[7]张晓娟,关明明,吴长奇.基于点判决域的多模盲均衡算法及其FPGA实现[J].电子技术应用,2011,37(2):49-51.