基于FPGA多通道高速数据采集存储器设计

2012-06-26刘文怡

郭 铮,刘文怡,冯 妮

(中北大学a.仪器科学与动态测试教育部重点实验室;b.电子测试技术重点实验室,山西 太原 030051)

在航空航天领域,遥测存储系统在飞行试验中起着极其重要的作用,而其各个子系统在记录飞行器飞行过程中各参数状态方面也扮演着重要角色。目前飞行器试验测试的完成大多是利用无线电遥测,但在某些特定的环境下会影响电波的发射使信号受到屏蔽,在这些情况下就需要采取某些辅助措施,而数据记录器恰好弥补了上述缺点[1]。数据存储器作为测试存储系统的核心部件具有体积功耗小、抗冲击能力强、测量精度高、抗干扰能力强等特点,特别适用于飞行器上记录各状态的动态参数,它能够完整地记录飞行器从起飞或发射到落地间的完整数据,待试验结束通过回收数据存储器,将数据读出,此测试方法记录完整,具有较高的可靠性[2]。

当今半导体技术迅速发展,使大容量高速存储技术得到长足进步,加之可编程逻辑器件的高度集成化以及较强的时序控制能力,使采集存储高速数据成为可能[3]。本文依靠现有技术,设计一种高速、大容量、高可靠性的数据存储器,该系统的优点是具有良好的逻辑控制能力。

1 系统总体设计

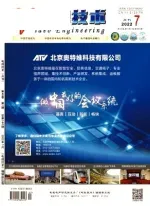

设计以FPGA作为主控单元,主要完成对1路PCM码流及2路音频信号、2路图像信号进行采集和存储。数据分别采用RS-422接口及异步串行接口传输,数据流消失,存储器停止记录,其工作状态是以数据形式记录。采集的数据分别存储于2片容量为1 Gbyte的K9K8G08U0A的固态Flash中。在设计中,以数据存储器为主体,配合地面测试台,以及上位机软件完成闭环自检试验。通过上位机发送不同的指令,分别完成实时监测、远程读数、数据存储及分析。总体框架如图1所示。

图1 系统总体框图

其中,数据存储命令采用开关方式的硬启动信号,在硬启动开关断开的情况下,采用在线软控制模式,通过测试台发送存储模块的实时监测以及远程读数的软启动命令。软启动命令由上位机软件控制,硬启动由地面测试台开关控制,且硬启动信号具有最高优先级,当硬启动命令发出时,存储器停止一切当前工作,转入执行数据存储工作模式。

2 硬件电路设计

2.1 PCM码调解电路设计

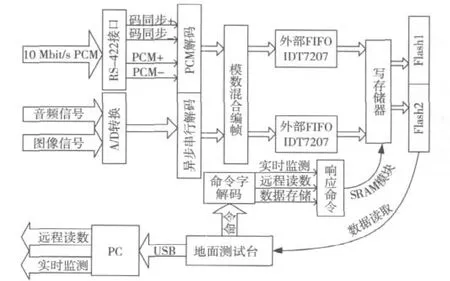

PCM码即脉冲编码调制是遥测系统将从传感器接收到的模拟信号经过编码、量化、抽样这3种方法转换为数字信号的过程。本设计收到系统发送的数据流是由码同步信号和PCM码组成,PCM码是每字节8位的串行数据。其具体的帧格式如图2所示。

图2 PCM帧格式图

PCM码调节电路的工作原理是:PCM码数据首先经过RS-422接口芯片DS26C32接收,接口匹配电阻选用100 Ω,进行电平转换。将RS-422电平转换为CMOS电平,经过电平转换后的PCM码再经过软件高频消抖[4]。最后,PCM数据在码同步信号的作用下,数据存储器采用下降沿接收数据,将串行数据转换为8位一组的并行数据进入FPGA,再在主控FPGA的控制下,与接收的其余4路模拟信号混合编帧,分别写入FIFO中。由于采集的数据码率比较大,而存储器选用的FPGA芯片XC2S100内部FIFO无法满足其容量要求,故选取32 kbyte×9的外部FIFO,IDT7207作为数据缓存区。FPGA再根据非空即读的原理,将写入FIFO中的数据读出,分别写入2片Flash芯片中。

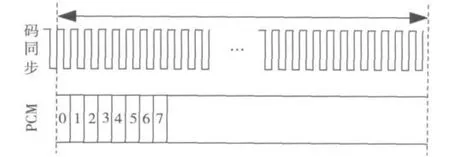

2.2 模拟信号采编单元电路设计

采编单元主要完成对2路音频信号、2路图像信号的采集编帧。4路模拟量在进入FPGA前,首先要进行信号调理,调理芯片采用AD824,该芯片的特点是响应快、带宽高,信号输入端需接入高阻值电阻,防止电流过大损坏运放[5]。经过调理的信号稳定后,启动A/D转换。A/D转换芯片是模拟量采编单元的核心部件,需要具有低功耗、高精度、工作温度范围广等特点。本设计根据实际任务采样频率的要求,采用AD8401芯片,采集电路如图3所示。其中,在硬件设计时芯片供电引脚加入了滤波电容,模拟量输入信号加入了高频去耦电容。

图3 模拟量采集电路设计

2.3 Flash存储单元设计

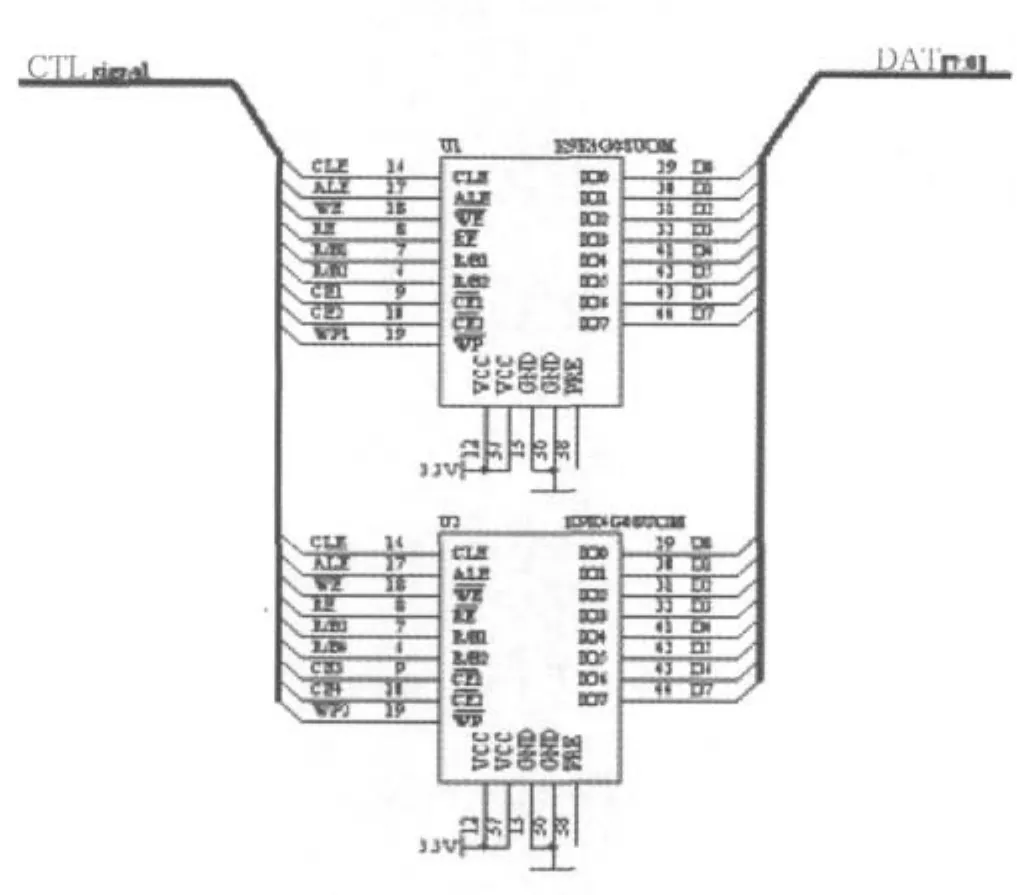

目前,非易失性存储介质有 RAM,EEPROM,Flash等。针对本设计的任务要求,选用三星公司的K9K8G08U0A芯片,并采用双Flash并行存储电路,即2块Flash芯片在主控FPGA的作用下,并行处理数据,分别写入Flash芯片中。这样可以保住存储数据完整地记录下来,具有双保险的意义。K9K8G08U0A芯片共有8448 Mbit,按块划分为8192 block,1块有64页,1页有(2 k+64)byte。典型的页编程时间为200 μs,典型块擦除时间为1.5 ms[6]。本设计Flash的读写操作按页进行,擦除操作按块进行。当Flash中数据存满后,会采取自断电保护,FPGA通过给CMOS器件IDF7404高低电平控制Flash的通断电,这样会保证记录的有效数据不会因误操作而使原有数据被覆盖。

另外,Flash的保护也是设计重点,本设计Flash采用单独电路板,其间用高温导线与数据采集板相连,这样做可以单独保护Flash电路。它的防护采用双层嵌套保护。首先将Flash板放于桶A中,桶内灌封聚氨酯保护,仅留出备用读数口(仅在回收读取数据使用),再将桶A置于桶B中,其间采用毛毡防护,这样可以使Flash板有较高的抗冲击抗过载能力,待试验结束,通过硬回收存储器,从备用读数口将采集的数据读出。Flash硬件电路设计如图4所示。

图4 Flash硬件电路设计

3 关键技术研究

在以往的设计中,大多采用模数独立编帧,分别存储于不同的Flash中,此种设计虽然方便简单,但切换Flash存储,串扰、丢数、误码情况严重。所以,在本设计中采用模数混合编帧的方法,即分别在模拟量、数字量数据中添加不同的帧头、帧尾及帧计数。数字量帧头帧尾分别为0xEB,0x90,模拟量帧头帧尾分别为0x14,0x6F。取251个字节,加入各自帧头帧尾及3个字节的帧计数,然后数据分别写入缓冲FIFO内。FPGA根据非空即读的原则,读取FIFO中数据,进行存储。由于设计中采用的是大容量FIFO,所以,不会出现丢数的情况。待数据存储完毕后,上位机根据不同的帧头、帧尾,将数据解包,分别处理、分析。帧结构如图5所示。

图5 帧结构分析

4 系统的闭环自检

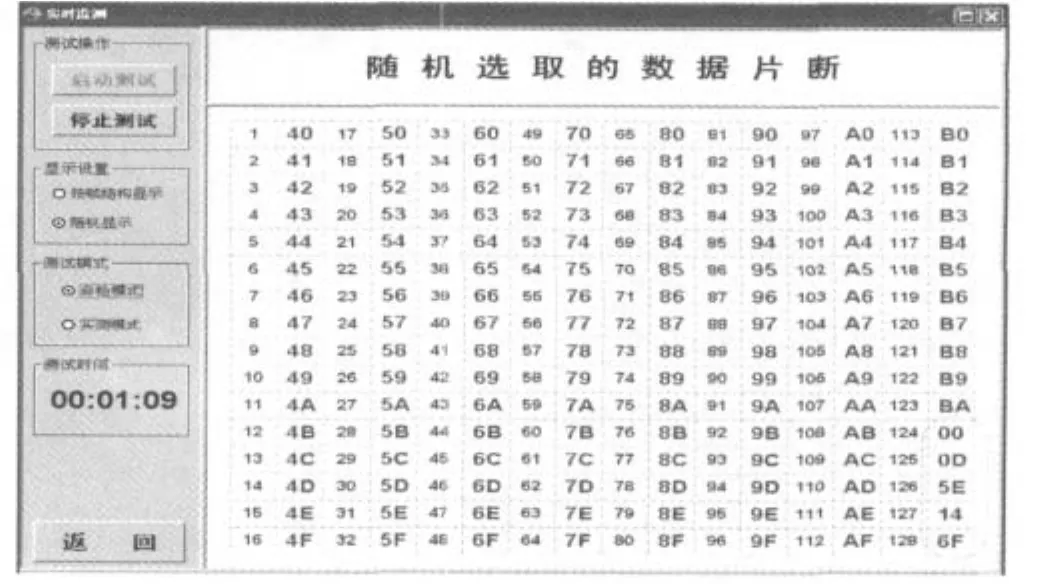

系统闭环自检,就是模拟实时的工作环境,数据存储器配合地面测试台和计算机对其完成系统的功能测试。地面测试台接收上位机命令模拟信号源发送数据给存储器,数据存储器再响应上位机命令,对测试台发送的数据进行解码、编帧,再将数据存储到双Flash中,同时通过实时监测SRAM将存储数据片段在计算机上显示。数据存储完毕,再通过远程读数将存储数据读出分析。这样的一系列操作就完成了对数据存储器的闭环自检。图6是根据试验的要求,由上位机发送命令,地面测试台发送自检数据,在计算机终端显示的实时监测结果。

图6 实时监测画面(截图)

5 结束语

本设计采用2片Flash存储芯片,对试验数据进行备份存储。相比于单机存储,可靠性更高,并结合相关的存储器防护设计,保证存储器数据在硬回收过程中被完整保护。本设计已在相关项目中得到应用,工作性能良好,具有一定的参考价值。

[1]刘攀,王红亮,孟令军.基于FPGA的数字图像采集存储系统的设计[J]. 电视技术,2010,34(6):33-34.

[2]朱维宝,孙波,李砥擎.航天器综合测试系统设计[J].计算机测量与控制,2009(8):1457-1459.

[3]郭虎峰,张会新,冯长磊.弹载数据记录器性能的优化设计与实现[J]. 计算机测量与控制,2011,19(1):108-110.

[4]张文栋.存储测试系统的设计理论及其应用[M].北京:高等教育出版社,2002.

[5]甄国涌,林华亮.串行PCM码流解码电路设计与应用[J].航空计算技术,2005,35(1):79-81.

[6]阎石.数字电子技术基础[M].北京:高等教育出版社,2006.