基于EDA技术的数字系统设计

2012-06-09赵辉

赵辉

(天津理工大学 中环信息学院,天津 300380)

随着电子技术的飞速发展,数字系统的设计正朝着高速度、大容量、小体积方向前进,传统的自底向上的设计方法已经难以适应电子系统的设计要求,因此,电子设计自动化(EDA)技术应运而生。EDA是以计算机为工作平台,以EDA软件为开发环境,以硬件描述语言(VHDL/Verilog HDL)为设计语言,以可编程逻辑器件(CPLD)为实验载体,以ASIC/SOC芯片为设计的目标器件,自动完成用软件的方式设计电子系统到硬件系统的一门新技术[1]。它是融合了电子技术、计算机技术、信息处理技术、智能化技术等最新成果而开发的高新技术,是一种高级、快速、有效的电子设计自动化工具。

1 EDA技术的发展

随着计算机技术、集成电路技术、电子系统设计技术的发展,EDA技术的发展经历了3个阶段[2-5]。

1)20世纪70年代的计算机辅助设计 (Computer Assist Design,CAD)阶段

随着MOS工艺以及中、小规模集成电路的出现和应用,传统的手工制图制版设计与电路集成的方法已经无法满足产品设计精度的要求。人们开始利用计算机辅助进行电路原理图编辑,PCB布局布线,使设计师从传统高度重复、繁杂的绘图劳动中解脱出来。这一时期最具代表性的产品就是美国ACCEL公司开发的Tango布线软件。

2)20世纪80年代的计算机辅助工程 (Computer Assist Engineering,CAE)阶段

随着计算机和集成电路技术的发展,相继出现了集成上万只晶体管的微处理器、集成几十万甚至上百万存储单元的随机存储器、只读存储器以及可编程逻辑器件 (PAL和GAL)。EDA技术进入了计算机辅助工程设计阶段。具有自动综合能力的CAE工具代替了设计工程师的部分设计工作,提高了产品设计的精度和效率。设计工程师可以通过软件工具来完成审批开发的设计、分析、生产、测试等各项工作,使设计阶段对产品性能的分析前进了一大步。

3)20世纪90年代的电子设计自动化 (Electronic Design Automation,EDA)阶段

设计工程师在产品设计过程中,从使用硬件转向设计硬件,从电路级电子产品开发转向系统级电子产品开发。硬件描述语言的标准化以及基于计算机技术的大规模ASIC设计技术的应用,使得EDA技术得到全新的发展。这一阶段的主要特征是以高级硬件描述语言 (VHDL、AHDL或Verilog-HDL)、系统级仿真和综合技术为特点,采 用“自顶向下”的设 计 理念,将设计前期的许多高层次设计由EDA工具来完成,实现了整个系统设计过程的自动化。

2 EDA技术的基本特征

EDA技术代表了当今电子设计技术的最新发展方向,它的基本特征是:采用自顶向下的设计方法,对整个系统进行方案设计和功能划分,然后采用硬件描述语言完成系统行为级的设计,最后通过综合器和适配器生成最终的目标器件[6]。下面介绍EDA基本特征有关的几个概念。

1)自顶向下的设计方法 EDA技术提供了一种自顶向下(Top Down)的设计方法。这种设计方法是从系统的总体要求出发,自顶向下地逐步将设计内容细化,最后完成系统硬件的整体设计。由于设计的主要仿真和调试过程是在高层次上完成的,这一方面有利于早期发现结构设计上的错误,避免设计工作的浪费,同时也减少了逻辑功能仿真的工作量,提高了设计的一次成功率。

2)VHDL语言 VHDL(Very-high-speed integrated circuit hardware description language)是一种全方位的硬件描述语言,1987年被IEEE和美国国防部确认为标准硬件描述语言[7]。它是一种用于设计硬件电子系统的计算机语言,它用软件编程的方式来描述硬件系统的逻辑功能、电路结构和连接形式,它包括系统行为级、寄存器传输级和逻辑门级多个设计层次,支持结构、数据流、行为3种描述形式的混合描述,几乎覆盖了以往各种硬件描述语言的功能,整个自顶向下或自底向上的电路设计过程都可以用VHDL来完成。在电子工程领域,它承担了几乎全部数字系统的设计任务 ,更适合大规模数字系统的设计。

3)CPLD 可编程逻辑器件 PLD (Programmable Logic Device)是一种由用户编程以实现某种逻辑功能的新型逻辑器件[8]。从20世纪70年代问世后,可编程逻辑器件经历了PAL、GAL、CPLD、FPGA几个发展阶段。其中CPLD/FPGA属于高密度可编程逻辑器件,目前集成度已高达200万门/片,它将专用集成电路(ASIC)集成度高的优点和可编程逻辑器件设计生产方便的特点结合在一起,以速度快、集成度高、可加密、重新定义编程、上万次的编程次数等优点得到广泛应用。CPLD/FPGA器件已成为现代高层次电子设计方法的实现载体。

3 使用EDA技术的数字系统设计

下面以Alter公司提供的Max+Plus II为平台,设计一个二十四进制计数器及其输出显示系统。该系统由计数器模块和显示模块两部分组成,电路的设计如下。

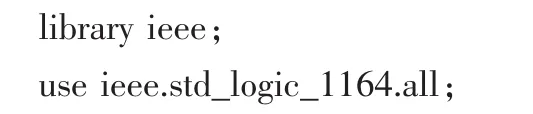

1)计数器模块的设计 二十四进制计数器的设计采用VHDL语言编程来实现。其VHDL程序如下:

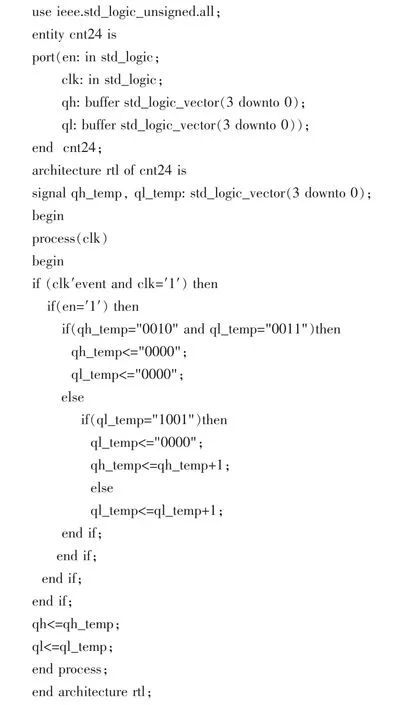

使用Max+Plus II的文本输入方式完成程序的输入,进行源程序的编译、仿真,得到图1所示的仿真结果。最后生成默认的计数器模块电路符号CNT24。

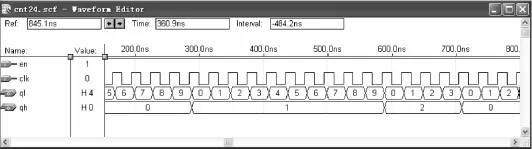

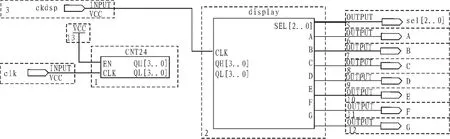

2)显示模块的设计 显示模块的顶层原理图如图2所示。它由3部分组成:八进制计数器CNT8、选择电路CHOOSE、七段显示译码电路DELED。

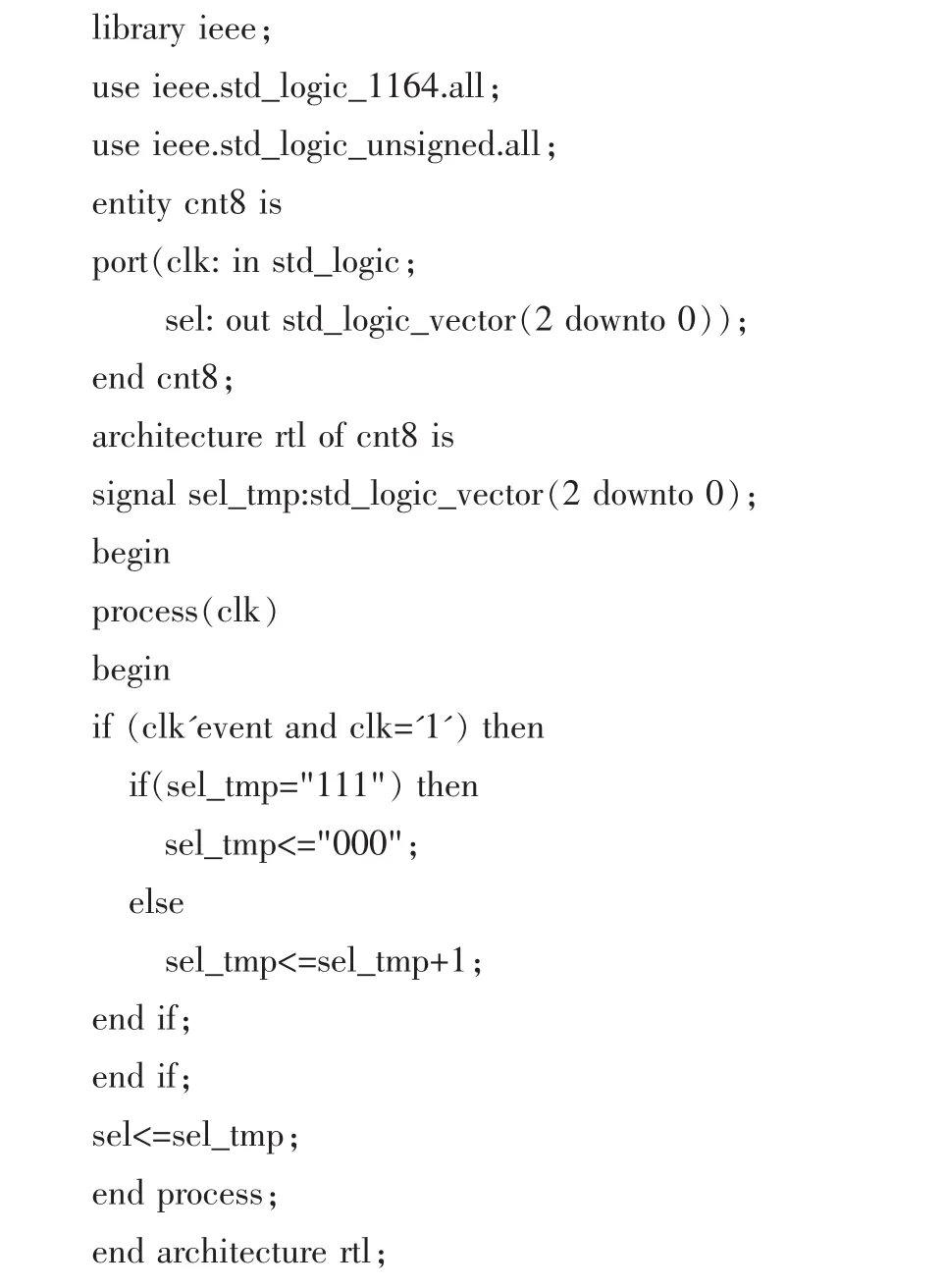

①八进制计数器的设计 八进制计数器的输入为时钟信号clk,输出为从000到111按顺序循环变化的3位二进制码,用来控制8位七段数码管的显示状态,其VHDL程序如下:

图1 计数器模块仿真结果Fig.1 Simulation of counter module

图2 显示模块的顶层原理图Fig.2 Top schematic of display module

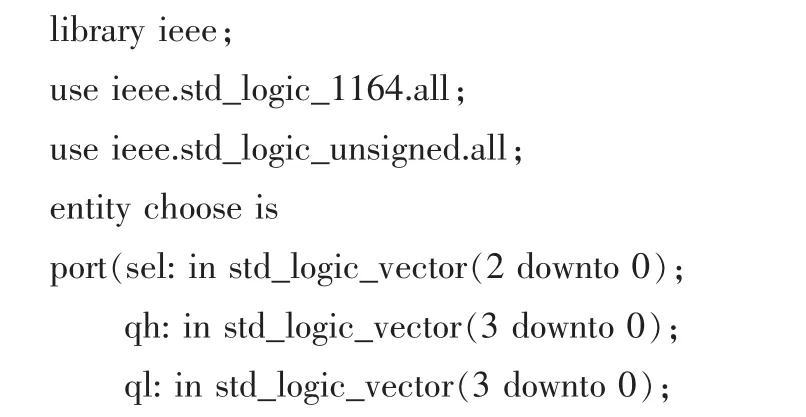

②选择电路的设计 选择电路以八进制计数器的输出sel作为选择输入信号,用来选择二十四进制计数器模块的输出qh和ql,并将其转换为4位矢量输出。其VHDL程序如下:

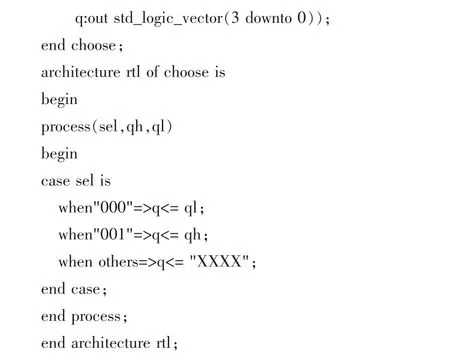

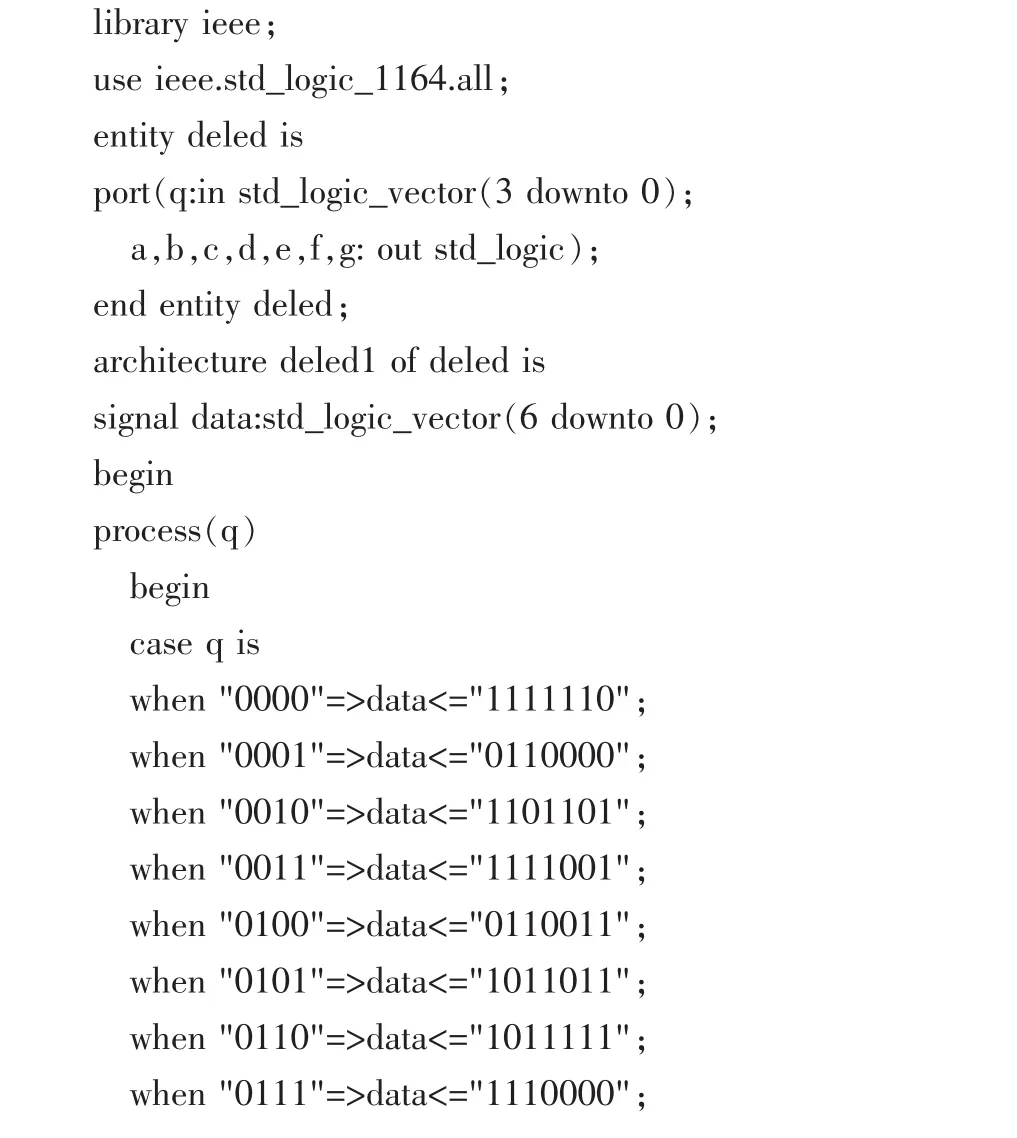

③七段显示译码电路的设计 七段显示译码电路将4位矢量转换为点亮LED 7段显示数码管a~g的信号。其VHDL程序如下:

使用Max+Plus II的文本输入方式分别完成八进制计数器、选择电路、七段显示译码电路各部分程序的输入,进行编译、仿真,最后生成各部分的默认电路符号。然后在原理图编辑器中调用各电路符号,按图2所示完成显示模块原理图的设计。对显示模块的原理图进行编译,并生成默认的显示模块电路符号display。

3)系统电路的设计

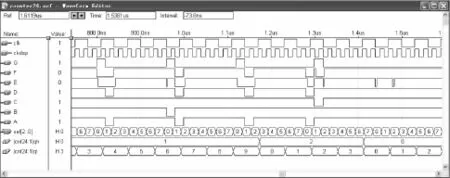

二十四进制计数器及显示系统采用原理图输入方式完成,在原理图编辑器中调用计数器模块CNT24和显示模块display电路符号,完成其顶层原理图的设计,如图3所示。对该电路进行编译、仿真,得到图4所示仿真结果。最后通过编程器或下载电缆将设计结果下载到目标芯片CPLD中 ,连接硬件电路验证设计结果符合功能要求。

图3 系统电路顶层原理图Fig.3 Top schematic of system circuit

图4 系统电路的仿真结果Fig.4 Simulation of system circuit

4 结束语

EDA技术彻底改变了数字系统的设计方法和实现手段,使电子系统的设计由硬件设计转变为以VHDL语言为核心的编程设计,借助于国际标准的VHDL语言和强大的EDA工具,使电子系统的设计变得思路简单,功能明了。使用CPLD可以反复进行硬件实验,降低了硬件电路的复杂程度,且设计电路的保密性强 。通过修改程序可方便地修改设计,提高了设计的灵活性,缩短了设计周期,提高设计的效率。

[1]WANG Li-qin,SHEN Lin.The application of EDA technology in education reform of system of hardware courses for electric information specialties[C]//Proceeding of 2010 International Conference on Future Information Technology and Management Engineering.Hubei:[s.n.],2010:268-271.

[2]谭会生,张昌凡.EDA技术及应用[M].2版.西安:西安电子科技大学出版社,2004.

[3]QI Hai-bing.Application of EDA Technology on Professional Teaching for Electronic Information Engineering[C]//Proceedings of 2010 International Conference on E-Health Networking,Digital Ecosystems and Technologies.Hubei:[s.n.],2010:203-206.

[4]Scheffer L, Lavagno L,Martin G.EDA for IC System Design,Verification,and Testing[M].U.S.A.Florida:CRC Press,2006.

[5]HU Hao-ran,WU Jia-ni,ZHANG Fei.Hardware design of independent experimental platform based on FPGA[C]//Proceeding of 2010 Second International Conference on Communication Systems,Networks and Applications.Hubei:[s.n.],2010:44-47.

[6]侯伯亨,刘凯,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].3版.西安:西安电子科技大学出版社,2009.

[7]刘爱荣,王振成,曹瑞,等.EDA技术与CPLD/FPGA开发应用简明教程[M].北京:清华大学出版社,2007.

[8]刘江海,涂传威,郭松梅,等.EDA技术[M].武汉:华中科技大学出版社,2009.