基于MPC8536的雷达嵌入式数据处理平台设计*

2012-06-08张利平

张利平

(中国西南电子技术研究所,成都 610036)

0 引言

近年来,随着大规模集成电路技术的成熟和发展,涌现出了许多功能强大的CPU处理器,POWERPC 即是其中的佼佼者,其产品线广、性价比高、温度范围广、集成度高以及功耗低等优点,正好满足现代高性能嵌入式设备的要求。POWERPC 搭载LINUX 内核,也可以满足绝大多数环境条件下的实时性要求。这里就以MPC8536为核心,构建了一个高性能的雷达通用数据处理平台,在不改变系统硬件的条件下,仅对软件进行更新,即可实现多功能性。基于通用处理平台的设计还可以扩展到后续任务如SAR 数据传输、雷达组网、雷达信号处理、大型数据链等多种用途,具有广阔的应用前景。

1 MPC8536 芯片介绍

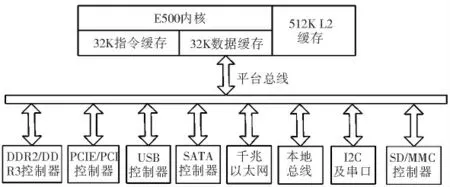

MPC8536 是Motorola 公司的高性能嵌入式微处理器芯片。该芯片内部集成了控制领域常用的外围组件,特别适合通信和网络设备的开发。MPC8536 采用E500 核结构,连同极高的网络、USB、PCIE和SATA 设备集成度,为用户提供了便捷的设计方案来建立高性能通用平台。其内部结构如图1所示。

由图1 可知,MPC8536 已经跨越了纯粹处理器的范畴,是一个高度集成的主控处理模块,并且还具有以下特点:

(1)具有高性能E500 内核,CPU 频率最高达1.5 GHz(2400MIPs);

(2)高度集成的内部控制器,如内存、PCIE、USB、SATA、以太网等,外围电路设计简单;

图1 MPC8536的内部结构

(3)低功耗,10W的典型功耗远优于X86 系列产品,且可以通过动态电源管理,控制静态和动态功率模式下的功耗;

(4)可运行嵌入式操作系统(LINUX、VXWORKS),便于多任务管理和调度,实时性强。

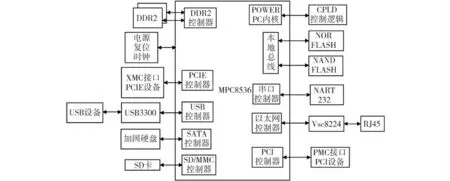

2 平台的硬件设计

系统的硬件部分主要包括MPC8536 微处理器模块、DDR2 控制模块、电源复位和时钟模块、存储器模块、千兆以太网模块、PCI/PCIE 控制模块、串行口控制模块、CPLD 控制逻辑、USB 控制模块、SATA 控制模块。系统硬件设计框图如图2所示。

2.1 电源、时钟和复位模块

考虑到功耗太大不利于散热进而影响系统稳定性,所以在芯片的选择上全部采用低功耗芯片。平台总共需要4 种电源,分别为1.1 V、1.2 V、2.5 V和3.3 V。其中MPC8536所需的电压由TI的开关电源TPS54910和LT1963AEST-2.5 提供,VSC8224所需的1.2 V 由TPS54312 提供。所选的芯片均能满足最大电流要求,且电源输出效率较高。在实际应用中,编程人员还可以利用软件启动MPC8536的各种节能模式,平均系统功耗测试值小于15W。

系统时钟电路分为3 部分,一是由33.33 MHz 晶振作为参考时钟,通过一个时钟分频芯片,分别送给CPU、CPLD和PCI 设备;另外选取一个14.31818 MHz的晶振,输入给ICS9FG108,分频输出PCIE 差分时钟;最后采用一个24 MHz的时钟,作为USB3300的输入,控制USB 设备。

系统复位模块采用的是MAXIM的电源监控芯片MAX16006。该芯片体积小、功耗低,可以通过配置同时监控8 种等级的电压,完全满足电压监控要求。

2.2 以太网和USB 模块

MPC8536 含有2个千兆以太网控制器,均可用作高速以太网接口。本系统采用VITESSE 公司的VSC8224芯片,加上脉冲变压器,就可以构造1000M/100M 自适应以太网。由于VSC8224 带一路光纤输出,所以本系统提供了两种网络模式选择。在某些对电磁干扰要求严格的环境条件下(如机载环境),采用光纤网络通信,可以减少电磁干扰,保证整机电磁兼容。

MPC8536 自带了2个USB 控制器,采用SMSC 公司的USB3300 加上LM3526M 电源管理芯片即可支持USB2.0 协议,实现外接鼠标、键盘、U 盘等接口。

图2 嵌入式通用处理平台系统框图

2.3 存储器模块

MPC8536 内部含有7个存储器控制单元,可以对各种存储外设进行管理。通过对每个存储器体的独立寄存器BRx和ORx 进行编程控制,可以实现对NORFLASH、NANDFLASH 等外设的读写操作。本系统的存储器模块划分为2个部分,即系统映像(NORFLASH)和应用程序(NANDFLASH)。由于嵌入式LINUX 操作系统一般体积较小,一片16M的NORFLASH 即可完成存储功能,故选用SPANSION的16 位总线存储芯片S29GL128N90TFIR1,用于完成U-BOOT和系统映像的存储。分配片选信号CS0,通过编程BR0和OR0 设置地址映射为0xAF000000~0xB0000000。

NANDFLASH 用于存放应用程序以及其他需要存储的大量数据。本系统采用三星的1G 容量芯片K9NBG08U5A,该芯片可以通过8 位的IO 口传输地址和数据,并且管脚兼容性好,可扩展存储容量。分配片选信号CS1,通过编程BR1和OR1 设置地址映射为0xBFFFFFFF~0xFFFFFFFF。另外,通过MPC8536 自带的MMC/SD 控制器和SATA 控制器,实现对SD 卡和SATA 接口的连接,作为大量实时数据的存储(如雷达SAR 图像)。

2.4 PCI/PCIE 模块

作为通用处理平台,必须要有高速总线和外部相连,MPC8536 自带的PCI/PCIE 控制器正好满足使用需求。方案设计时考虑将PCI 总线引到PMC 结构的接插件上,PCIE 总线引到XMC 结构的接插件上,方便进行功能扩展(如显卡、数据处理等)。

2.5 CPLD和串口模块

系统上电时,MPC8536 需要采样复位配置字,以决定其启动和工作方式。本系统通过CPLD 逻辑来完成上电复位配置字的采样,可以方便地对CPU 进行配置,如设置工作频率、配置总线和智能电源管理等。其自带的串口模块可以通过外接MAX3233E来实现RS232 接口,标准的I2C 总线也可以和低速外部设备互联。

3 软件设计

3.1 U-BOOT的移植

U-BOOT 是操作系统运行前执行的第一段程序,其作用是初始化硬件设备,建立内存空间映射表,为内核调用建立环境。系统采用最新的U-BOOT1.3.4,其中就包含了MPC8536的启动代码。根据硬件情况对源代码作如下修改:

(1)Include/configs/MPC8536DS.h

#define CONFIG_BOARD_SYS_CLK 33330000//设置系统输入时钟为33MHz;

#define CONFIG_SYS_FLASH_BASE 0xAF000000//设置FLASH 起始地址;

#define CONFIG_MAX_FLASH_BANKS 1//设置FLASH 只划分一个bank;

#undef CONFIG_EEPROM //无EEPROM 配置;

#define TSEC1_PHY_ADDR 1//分配第一个千兆网络地址;

#define TSEC2_PHY_ADDR 0//分配第二个千兆网络地址;

(2)Board/freescale/mpc8536ds/sdram.c

根据自身内存情况,在sdram_setup()函数中,添加对DDR2 控制寄存器时序的配置。

ddr->timing_cfg_3=0x00020000;

ddr->timing_cfg_1=0x4c47d432;

ddr->timing_cfg_2=0x331848ce;

将以上代码修改完毕后,编译生成U-BOOT.bin文件,通过BDI2000 写入NORFLASH,重新加电后串口即可输出启动信息。启动画面如图3所示。

3.2 操作系统的选择

操作系统选用LINUX 搭载最新2.6 内核,完全可以满足各种条件的应用要求。由于LINUX 系统具有安全性高、开放源代码、实时性高等优点,已经在军事和民用设备中得到广泛应用。使用标准C/C++编程语言就可以便捷的开发雷达信息处理应用软件,在ELDK4.2 环境下完成代码的编写、编译和调试。采用C/C++语言编写的代码具有易读、重用性高等优点,降低了开发难度,极大提升了开发效率。

3.3 操作系统的移植

2.6 内核已经支持MPC8536处理器和大部分外设,只需要根据平台实际情况,将LINUX 源代码中发布的MPC8536DS 开发板代码进行修改与裁剪即可。内核移植的步骤如下:

(1)修改顶层Makefile 增加编译选项

ARCH:=powerpc//选择POWERPC 架构;

(2)源代码的修改

由于系统硬件配置和FREESCALE的开发板有较大差异,所以需要对部分代码进行修改。如关键的网络地址的配置、时钟频率的配置等;

(3)内核的裁减

# make menuconfig //裁减掉内核中所有与本系统无关的模块;

图3 U-BOOT 启动画面

# make //编译完成后生成内核映像uImage;

(4)文件系统的实现

系统在调试阶段采用的是NFS 文件系统,通过tftp 进行网络加载,实现阶段是将RAMDISK 根文件系统写入NORFLASH 进行自动加载。NFS的实现较为简单,在ELDK4.2 交叉开发环境中,PPC_85XX 目录下即提供了一个NFS 根文件系统。只要主机提供了NFS服务,目标机即可通过tftp 进行引导。RAMDISK根文件系统的制作流程如下:

*创建根文件系统文件夹;

*创建各种必要的系统文件;

*创建设备节点;

*建立与启动相关的配置文件;

*安装库文件glibc;

*编译busybox,安装系统和应用软件。

4 结果与分析

在调试过程中,发现U-BOOT的移植过程非常关键,应该根据硬件配置对源代码进行修改。DDR2 寄存器需要根据实际PCB 布线来对时序进行微调,否则会导致系统不稳定或者根本无法启动。PCB 布板时要注意电源与信号的分层隔离。PCIE 高速差分信号线均需要进行等长设计,尽量从顶层或底层走线并保证地层的包裹。

在实际应用中,本平台主要完成的是雷达目标数据的解析工作。首先通过PCIE 总线接收多块雷达信号处理板送出的目标信息,然后通过优化算法对数据进行分类解析,最后将需要的目标信息通过光纤网络送到综显进行显示。在本系统中,要求数据处理平台能够以较短的时间响应多块信号处理板的中断请求,并从大量目标数据中提取需要的目标信息,实时地传送给综显进行显示。

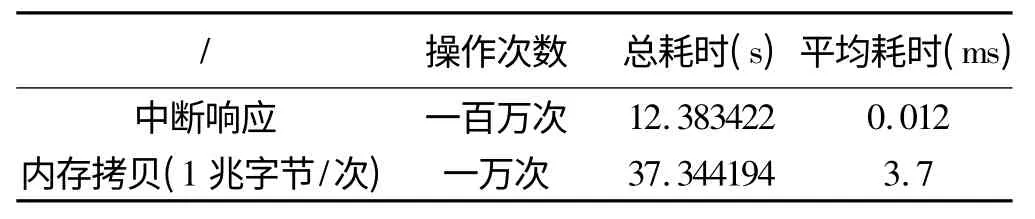

这里对系统中关键的中断响应和内存拷贝两项指标进行了测试,测试结果如表1。

表1 中断响应和内存拷贝耗时

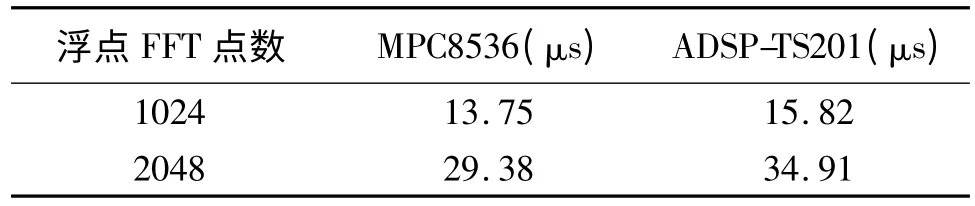

笔者将本平台和曾使用的ADSP-TS201信号处理芯片进行对比测试时发现,当采用雷达信号处理常用的浮点复数FFT 运算作为测试算法时,MPC8536的运算性能还优于ADSP-TS201。运算速度对比见表2。

表2 MPC8536与ADSP-TS201 性能对比

可见,虽然功耗略高于ADSP-TS201,但是MPC8536搭载LINUX 操作系统,已经可以胜任专业DSP的信号处理工作。LINUX 操作系统下的中断响应时间和内存读写速度也满足绝大多数环境条件的应用。雷达通用数据处理平台采用了LINUX 操作系统作任务管理的设计,应用灵活,开发调试方便,更能满足现代雷达对多任务、多功能的实际需求。

5 结束语

随着高性能通用处理器技术的飞速发展,基于POWERPC+LINUX 实时操作系统的雷达通用数据处理平台将成为发展趋势。本文介绍的即是其中一种应用于雷达设备中的通用数据处理平台的设计方法。该平台以Motorola 公司的高性能通信处理器MPC8536为核心,具有低成本、高性能、通用性好等优点。平台支持的多种通用数据接口加上LINUX 系统的稳定性,将可以适应不同的应用环境。在测试中发现,MPC8536 已具备较高的信号处理能力,可以在以后的应用中尝试进行简单信号处理算法设计,通过操作系统这种多任务的管理方式对信号处理流程进行优化,达到提升整体系统性能的目的。此通用数据处理平台已经成功应用于某型号雷达设备中。本平台的研制成功,也为下一代的雷达系统设计提供了借鉴,具有较大参考价值。

[1]MPC8536E PowerQUICC III.Integrated Processor Reference Manual Rev.0 10/2008.

[2]MPC8536E PowerQUICC.III Bring-Up Guide Rev.0,02/2009.

[3]韦东山.嵌入式Linux 应用开发完全手册[M].北京:人民邮电出版社,2009.

[4]Alessamdro Rubini.linux 设备驱动程序[M](第4 版).北京:中国电力出版社,2000.

[5]于明俭,陈向阳,方汉.Linux 程序设计权威指南[M].北京:机械工业出版社,2001.