软硬件联合仿真平台的设计

2012-06-02厦门大学信息科学与技术学院

厦门大学信息科学与技术学院 奎 伟

1.前言

在做FPGA设计时,软件仿真这个步骤是必不可少的。仿真工具如Modelsim在每一个仿真时钟片上会依次计算电路中每一个寄存器的值,完成之后再进入下一个仿真时钟片。由于CPU的运算是串行的,当仿真时间较长,或者电路结构很复杂时,软件仿真就会变成一件很耗时的事情。

假设仿真的最小时钟片是1ps,那仿真1s的时间长度需要进行1万亿次时间片的计算,每个时间片内的所需要的计算时间是由电路中寄存器的个数来决定的。如果目标电路是一个简单的加法器,这样的仿真过程仅需要不到1秒的时间;但是当目标电路换成一个1O万门以上的系统之后,所需要的仿真时间就会变得难以忍受。

软硬件联合仿真的概念早在HDL语言建立之初实际上就已经提出来。HDL的标准里有很大一部分描述了HDL语言与其他高级编程语言的接口规范,verilog对应的接口规范叫做PLI(Programmable Language Interface)[1],这个接口允许在仿真层次上verilog与C语言进行互动。有这个编程接口之后,HDL仿真就变得十分灵活,它可以借助于C语言实现的驱动程序与各种硬件设备进行交互,这就提供了一种可靠的软硬件联合仿真的技术基础。文献[2]给出了联合仿真的统一模型,文献[3-5]提出了不同的硬件加速设计方案。本文基于上述研究,提出一种使用USB2.O接口作为数据传输通道的软硬件联合仿真平台实现方式。

2.软硬件联合仿真平台设计

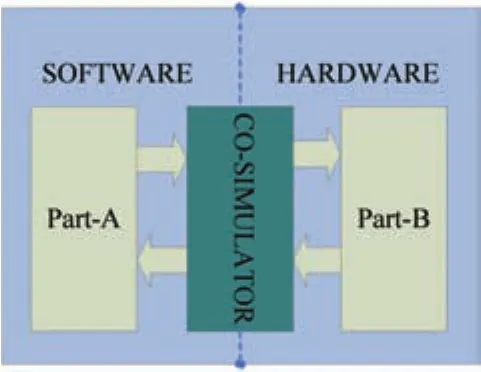

软硬件联合仿真的大体思路是:将一个系统拆分成为两部分,待验证模块和其他部分。将需要重点关注的待验证模块放在仿真工具上仿真,然后将其他部分直接烧入FPGA芯片里,通过外设接口(PCI-E、USB等)实现FPGA芯片和电脑的数据交互。为了保证仿真结果的可靠性,烧入FPGA芯片内的模块必须是验证后可靠的。

一个大系统的设计往往会经过从算法仿真到硬件描述语言仿真再到FPGA实现的过程,逐步的由软件框架变为硬件设计。借助于软硬件联合仿真的方法,就可以将一个系统分块由软件变为硬件,并且能够在设计过程中很方便的验证设计的正确性和可靠性,将出错的风险分散在整个设计流程内,降低最后除错的复杂性。

本设计实现了Modelsim与FPGA开发板的通信,传输接口采用USB2.O。USB2.O数据传输速率最高可以达到48OMbps,平均传输速率大概是3MB/s,可以满足仿真过程中大量测试数据的传输。

联合仿真需要解决的问题主要有,软硬件通信方式的设计以及软件时钟和硬件时钟的同步。本设计中采用软件生成时钟,驱动硬件产生时钟边沿脉冲信号,来控制硬件运行速度,保证软硬件运行速度的一致性。

2.1 系统框架

整个软硬件联合仿真平台的设计主要分为三个部分:Modelsim端的接口程序设计、USB驱动在PC上和FPGA上的实现、FPGA端接口控制电路的设计。

Modelsim端需要实现的功能有:时钟信号的生成,测试文件的实现以及实现USB通信的软件设计。这个部分是整个系统的驱动部分,所有对仿真过程的控制都在Modelsim上实现,同时也是系统人机交互的接口。这一部分需要实现对硬件的透明化设计,即用户只需要修改测试文件就能控制整个仿真的流程,与纯软件的仿真过程没有太大差异。

USB的驱动部分分为PC端和FPGA端。PC端的驱动采用windriver自动生成底层接口函数,然后再在这个基础上编写通信控制程序以及PLI的调用,实现Modelsim通过USB接口进行收发数据的功能。FPGA端采用了一块通用USB控制芯片cy7c68O13,直接连接到FPGA上。然后在对该芯片进行操作,实现FPGA通过USB接口进行收发数据。

FPGA端接口控制电路的设计所实现的功能包括:时钟信号的生成与驱动,仿真数据的收集功能,通信帧的组成与解帧。其中重点就是需要完成与软件时钟的同步以及数据搜集逻辑的实现。

2.2 系统性能分析

软硬件联合仿真平台的设计目标是为了加快仿真速度,缩短系统的设计周期和设计复杂度。我们会从时间性能上来分析使用软硬件联合仿真的方法带来的好处。

Modelsim的仿真过程是分仿真时间片进行的。每个仿真时间片内,Modelsim按照数据路径依次对系统中所有门电路和基本逻辑单元的输出进行计算。因此Modelsim每个时间片的仿真时间与系统综合后占用的门数成正相关。

设仿真时间TM与系统所占用的逻辑门数Ng之间的关系为:

若采用软硬件联合仿真的方式,将该系统的一部分放入FPGA内运行,则可以计算出联合仿真模式下所需要的仿真时间。

对待测系统进行分割之后,设需要放入FPGA的部分所占用的逻辑资源比例为p:

采用软硬件联合仿真后,所需要的仿真时间分为两个部分:运算和数据传输,计算公式如下所示:

上式中,TFPGA表示FPGA内部计算时间,包括成帧解帧逻辑和系统一个时钟周期的运行时间,而这个时间不会超过微秒数量级,所以通常情况下,

上式可以化简为:

由系统加速比的公式可以看出,软硬件联合仿真所带来的加速收益是与软硬件划分程度p和系统复杂度Ng成正比。而USB传输所需的时间又可分为设备初始化时间和传输时间,由于这是一个高速的串行接口,因此对于绝大多数待测系统来说,tUSB可以看作是一个固定不变的值(即不随系统的复杂度而改变)。因此,当系统越复杂时,采用软硬件联合仿真可以得到更好的仿真加速性能。

3.仿真平台的实现

3.1 PC端设计

PC端实现的功能是:1.产生测试用信号;2.实现USB接口驱动,完成与FPGA的通信;3.利用PLI的接口在Modelsim的波形窗口中显示需要关注的信号。

如图2所示,待测系统被分为软件和硬件两个部分。同样,我们所设计的接口也分为软件和硬件部分,PC端实现的就是仿真平台接口的软件部分。

PLI全称为Programmable Language Interface,是在1985年就公布的Verilog HDL语言与c语言的编程接口。通过PLI接口,Verilog HDL语言的仿真器变得更为灵活,可以完成几乎任何能够想到的任务,包括图形交互工具、文件读写、以及本设计中所用到的硬件驱动。

定义系统任务$getData,实现PC端对数据的读取操作。该系统在时钟信号发生变化时做出响应,首先会判断时钟上升沿和复位、使能信号是否有效。当条件都满足时,$getData读入标准化后的输出端口信号值,将其打包组成通信帧,之后再调用USB驱动程序将数据发送出去,并且读入来自FPGA的输入端口信号值,解帧后驱动到Verilog HDL的端口上,实现PC与FPGA的通信。

图1 系统设计框图

图2 系统软硬划分示意图

图3 通信帧结构

图4 FPGA端结构图

图5 待测模块的时钟生成逻辑

图6 加法器的软硬件联合仿真结果

图7 加法器的软硬件联合仿真波形图

3.2 通信帧设计

对于不同的待测系统,所需要传输的信号数量也各不相同。为了保持通用性,我们在软硬件仿真平台的USB通信部分设计了数据帧格式,使得程序可以自主的完成传输过程,而不需要对每一个待测系统再进行单独的配置。

通信帧的结构如图3所示。帧长度设计为32(N+1)bits,其中N代表每一帧包含的32位端口个数。一个完整的通信帧由1个记录传输信息的帧头和N个记录数据的帧体所组成。当N=7时,每个通信帧的传输容量为256位,其中可以传输224位信号线的数据。

帧头的32位数据定义如下:页数12位,表示当前通信过程总共需要的通信帧的个数,最多可以支持到4O95个帧,28665x32位的数据传输。页号12位,表示当前帧在整个通信过程中的序号,用来避免顺序出错以及做通信结束判断标志。特殊信号7位,每一位代表一种特殊信号,比如时钟、复位、使能信号等控制信号。传输方向标志(I/O)1位,表示当前通信帧是由FPGA传向PC还是反向。

作为数据空间,第一帧的第二个子帧(即数据域端口1)的32位被用来以无符号整数的形式传输port_in(或port_out)端口的个数,因此有效的总数据量会减少32位。

3.3 FPGA端设计

FPGA端完成的工作包括USB芯片的时序控制电路,以及联合仿真的时钟数据控制电路,共分为两个独立的模块实现,分别是USB_FPGA和enFrame。前者实现的是对USB接口进行32位数据的读写操作,后者实现将USB端口传入的数据正确的配置到待测模块Part-B上,并控制Part-B进行单时钟脉冲运行(单步运行),使得FPGA的运行速度与PC端Modelsim的仿真速度相匹配。

与软件端对应,enFrame也采用自动代码生成器生成与Part-B的连线逻辑,并且内部实现了将PC端传来的通信帧解帧,剥离出数据信号,配置到Part-B的输入端口;同时,enFrame也在每一个仿真时钟周期对Part-B的输出信号采样,成帧后由USB接口发送至仿真平台的软件端。

这个过程有一个难点在于,如何实现FPGA上系统的单步运行。我们采用的方法是,将Part-B的时钟信号单独剥离出来,由测试平台提供的单脉冲上升沿信号作为Part-B的时钟输入。如图5所示,利用使能信号ENB和晶振产生的方波信号,可以实现易于控制的单脉冲时钟信号。当enFrame将所有数据信号配置在Part-B的输入端之后,激活使能信号ENB,在一个时钟周期之后立刻禁用ENB,这样,图5所示电路的输出就只有单个上升沿/下降沿,达到预先的目的。

4.测试实例

通过USB接口,对FPGA发送测试数据。将FPGA数据处理后的结果采集并发送给Modelsim中的shift.v模块。如图6,DataIn是通过USB发送给FPGA上加法器的测试数据,DataOut是经FPGA加法后返回的数据,可见结果是正确的。如图7,是将DataOut发送给Modelsim,由shift.v模块中的din接收,dout为经过移位后的结果。如图6:DataIn[O]传入FPGA数据为97,经加法后为DataOut[O]=98,发送给shift.v的dinO为98,经右移后结果为doutO为49。结果完全正确。从而验证了硬件仿真加速的想法。同样,亦可在FPGA中运行更为复杂的系统,UUT模块选择为H.264,方法亦是相同的。

5.结论

本文实现了PC与FPGA的联合仿真平台设计,并从理论上证明了该仿真平台能够达到的加速性能。软硬件联合仿真平台共分为3个部分,分别是电脑上的用户软件接口,数据通信协议和FPGA内的控制模块,电脑与FPGA平台使用USB接口连接。本文使用加法器作为测试样例证明了该结构的可行性。与纯软件仿真的FPGA设计方法相比,在设计过程中使用联合仿真方案可以极大降低设计风险,缩短设计周期。

[1]“IEEE Standard Verilog Hardware Description Language”,New York,September 2001.

[2]Valderrama,C.,A.Changuel,et al.“A unified model for co-simulation and co-synthesis of mixed hardware/software systems”,Proceedings of European design and test conference,1995.

[3]Ruelland,R.,Gateau,G.,Meynard,T.A.,Hapiot,J.-C,“Design of FPGA-based emulator for series multicell converters using cosimulation tools”,IEEE Transactions on Power Electronics,January 2003.

[4]Jingzhao Ou,Prasanna,V.K.,“MATLAB/Simulink based hardware/software cosimulation for designing Using FPGA configured soft processors”,Proceeding of parallel and distributed processing symposium,2005.

[5]A.Hoffman,T.Kogel,H.Meyr,“A framework for fast hardware-software co-simulation”,Pro-ceeding of the conference on design,utomation and test in Europe,2001.