TD-LTE中基于码块分割的CRC模块研究与设计*

2012-05-12曹型兵杨高进余利成

曹型兵,杨高进,余利成

(1.重庆邮电大学通信应用研究所,重庆400065;2.重庆邮电大学重庆市移动通信技术重点实验室,重庆400065)

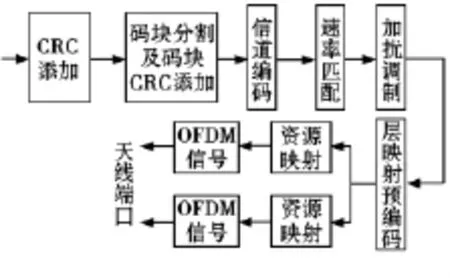

TD-LTE无线终端测试平台中基带板以DSP+ARM+FPGA为核心,DSP主要负责处理物理层软件中的部分内容,FPGA完成系统定时和物理层算法的部分内容。在下行物理信道一般处理流程中,从高层下来的数据需要经过如图1所示的几个阶段,包括CRC添加、码块分割以及码块CRC添加、信道编码、速率匹配、码块级联等一系列的处理流程[1]。最后实现基带信号的生成,通过天线端口将数据信号发送出去。

图1 下行物理信道一般处理流程

在测试仪表的基带板开发中,前期对于CRC的添加以及码块分割的过程采用了DSP进行其过程的实现。在采用DSP实现时,由于首先要对一组数据进行全数据的CRC添加,其次对于数据量超过一定位数时进行码块分割操作再做CRC添加。当高层发送下来的数据量过大时,采用DSP实现时需要内存空间进行清理,预留出一定的空间确保数据量能够完整地存储,以便进行后续的运算处理。并且采用DSP实现需要消耗大量的时钟周期进行运算处理。

本文根据实际情况需要,在DSP实现的基础上提出了采用FPGA来实现其相应的运算过程。FPGA通常用来实现较为固定的计算过程,在该设计方案中CRC校验码的添加,以及模块的分割均采用FPGA来实现,而DSP则用来进行数据以及控制信号的配置。从而可以更好地发挥FPGA与DSP的优点。

经过多次的仿真以及实际平台测试,实现了FPGA快速的生成CRC校验码,为后续的数据信号处理提供了可靠的保证,适用于TD-LTE无线综合测试仪中。

1 CRC校验的原理

在实际的传输信道中传输数字信号时,由于信道的传输特性不理想以及一些噪声带来的影响,从而导致接收端收到的信号不可避免地会发生错误,导致接收信号的失败。因此,为了保证传输的可靠性,就需要对传输过程进行差错控制,循环冗余校验CRC是一种高效率的差错控制方案。其具有编码及错误检测简单,容易实现且误判概率低、检错能力强等优点,在通信系统中得到了广泛的应用。

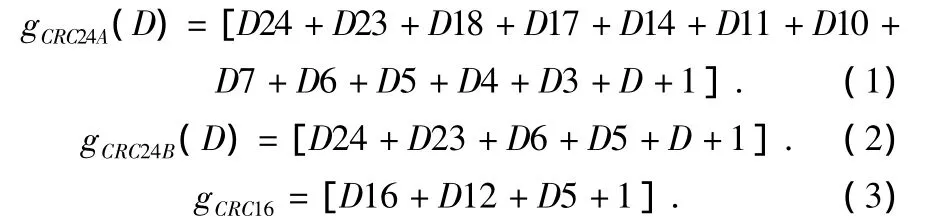

采用CRC校验时,发送方和接收方均采用同一个生成多项式g(D)(根据不同的需要选择不同的生成多项式),将最后的余数作为CRC校验码。根据3GPP[2]相关协议LTE中采用的校验比特由如下循环生成多项式之一产生。

对于物理下行共享信道采用gCRC24A(D)生成多项式,而对于下行广播信道则采用gCRC16(D)生成多项式。CRC校验码的编码原理是采用待发送的二进制数据a(x)除以生成多项式g(D),将其最终的余数作为CRC校验码。在FPGA中,实现CRC编码实际上是一个循环移位的模2运算。通过反复的移位和进行CRC的除法,最后得到的数据就是所需的余数。将所得到的余数放置在原始序列的尾部即实现了 CRC 的编码过程[3]。

对于CRC的解码过程,即采用与编码相同的生成多项式,同时也采用循环移位的模2运算,当计算出的结果为0时,译码正确,即完成了CRC解码过程,否则判为译码错误,则向发射端反馈NACK,请求数据重传。

2 LTE中CRC处理方式

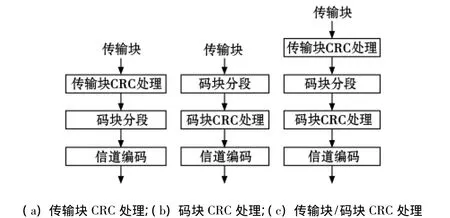

在LTE系统中,CRC的处理的具体长度由高层(MAC层)根据传输信道所承载的业务通过信令来通知传输信道,每个传输块的CRC校验的计算都要用到整个传输块(TB)的数据信息。当整个传输块的数据信息较长时,需要对TB进行分段处理。对于TB的分段,第一种可以选择先对整个TB进行CRC处理,然后进行分段处理,如图2(a)所示;第二种方法是先进行编码块(CB)分段处理,然后对每个CB分别添加CRC比特,如图2(b)所示;还有一种方法可以同时采用TB-CRC处理和CB-CRC处理,如图2(c)所示[4]。

经过研究发现,在原有的TB-CRC处理的基础上,在每个CB上分别添加CRC校验信息可以降低译码的复杂度,减小所需的译码延时及缓存器的大小,从而提高接收机连续传输处理能力,支持LTE系统的高速率传输,并且可以加快接收机的处理速度,实现快速的HARQ。因此,最后采用TBCRC和CB-CRC处理的方式[4]。

图2 3种CRC处理方式

CRC处理过程可以表述为:先在TB上添加24 bit CRC,然后如果进行码块分段(当传输块长于6144 bit时,此处选择6144 bit是因为在后续的),再在每个CB上添加24 bitCRC,如图3所示。

图3 CRC处理过程

采用这种双层CRC结构,接收端就可以在发现1个CB译码错误后停止译码,马上要求重传,而不需要等待整个TB译码完毕再反馈NACK,从而不仅避免了后续CB译码的无谓功率消耗,而且节省了处理时间,减小了HARQ重传时延,可以提高单位时间内的系统吞吐量。

而24bitTB-CRC则可以进一步减小CB CRC漏检的几率,防止1个CB上的漏检导致整个TB漏检,从而保证了整个TB上的漏检概率在6×10-8以下。

此方法还可以有效降低高速率传输时译码的平均迭代次数,减小接收机硬件的复杂度,降低对缓存空间的要求。另外,当进行多码字(Code Word,CW)MIMO信号的译码时,也可以利用CB-CRC实现CW之间的串行干扰消除(SIC)操作。

采用上述双层CRC结构需要考虑对TB-CRC和CBCRC是采用相同的CRC生成多项式,还是不同的生成多项式。经过仿真研究发现,使用不同多项式可以获得更低的漏检概率,因此确定采用不同的CRC生成多项式分别生成TB-CRC和CB-CRC。

2.1 CRC 计算

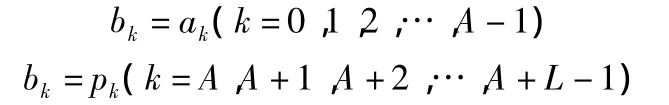

CRC 计算模块的输入比特为 a0,a1,a2,a3,…,aA-1,校验比特为 p0,p1,p2,p3,…,pL-1。A 是输入比特的长度,L 是校验比特的数目。将生成的校验比特添加至CRC的尾部。添加过的 CRC 之后的比特为:b0,b1,b2,b3,…,bB-1,添加后的比特数为B=A+L。ak和bk的关系为:

2.2 码块分段以及码块CRC添加

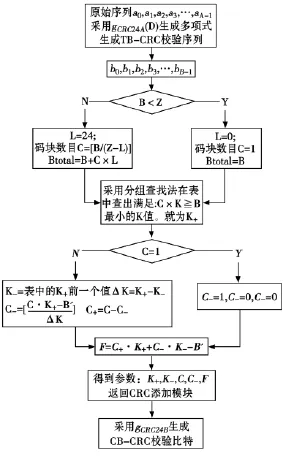

当输入的比特流比特数B大于最大码块大小Z(Z=6144)时,输入的比特流则需要分割,并且需要在每个CB上添加一个长度为24的CRC序列。具体的码块分割步骤可以采用如下图4所示的流程图进行实现。

图4 码块分割及码块CRC添加流程图

3 硬件实现过程

本设计中FPGA选择XILINX公司的VIRTEX-5(XC5VSX95T)芯片,软件环境为Xilinx10.1,仿真软件采用Modelsim SE 6.5。

3.1 编码器实现流程

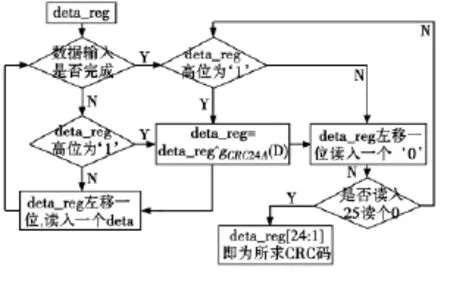

首先设置一个data_reg寄存器,当进行CRC-24校验时,先往寄存器中输入24bit数据,输入完成后首先判断data_reg最高位是否为1,如果为1,则data_reg=data_reg^gCRC24A(D);否则data_reg左移一位,读入一个新的数据,当原有数据输入完成后继续往其中输入1bit数据0,当输入的数据0达到25个时,此时data_reg的高24bit数据即为所求的CRC码块。具体的流程图如图5所示。

图5 CRC校验码计算流程图

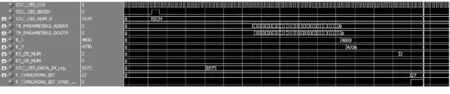

通过仿真可以得到如图6所示的计算结果图。此处采用CRC-24A校验,当数据接收完成后,开始进行计算过程data_reg=30’h65996659,当 crc_zero_cnt计数到 25 时即可输出结果,在光标处看到输出的crc_data=24’h0a633a,并将此结果附在原有数据尾部输出crc_out=54’h659966590a633a。其计算结果与MATLAB计算结果相同。由于输入的数据位数有不同的情况,可以采用双端口RAM进行数据的存储,通过从RAM中读数据,做运算,并将运算后的结果存入RAM中,从而降低FPGA内部LUT-FF资源使用率。

3.2 码块分割与码块CRC添加实现流程

码块的分割过程可以参照图4码块分割及码块CRC添加流程图进行其过程的实现。在实现的过程中,当采用分组查表法查出满足条件的K+时,我们需要将188种Turbo编码参数存储在一个ROM中;在查表时,若每次都从头开始查找则会大大降低查找速度。我们可以通过分组将其分为有相同的条件的几个小组,首先确定数据所在的地址范围,再通过对内部数据比较即可以找到所需的K+值,找到K+值后,即可以进一步计算出K-的值。通过F=C+·K++C-·K--B’计算出填充比特的数目,如图7所示。当进行的传输块比特长度为9500时,首先通过TB-CRC,码块长度变为9524,通过计算得到 K+值为4800,K-值为4736,但是此时长度为K+的码块数目为2,长度为K-的码块数目为0,通过计算得到填充比特长度为F_TIANCHONG_BIT=27,与实际计算结果相同。

对于填充比特则需要添加至传输块的头部,完成填充比特的添加后,根据不同的K-与K+值,取出相应的数据长度进行码块的CRC添加过程,此时采用的生成多项式为gCRC24B(D)计算过程采用图8 CRC校验码计算流程图所示过程进行计算。将计算出的数据添加至原始码块的尾部。从而完成了码块的分割以及分割后码块的CRC添加过程。

图6 CRC校验实现波形图

图7 码块分割实现波形图

图8 码块分割后CRC添加实现波形图

3.3 CRC校验实现流程

对于CRC的校验过程仍然可以采用CRC校验码生成过程的流程来实现,对于尾部添加了CRC校验码的比特流,与生成多项式进行除法运算,当计算出的结果为0时,即完成了正确的校验过程,否则认为接收到的数据出现错误,此时需要向高层发出请求重传标志信息。从图9中可以看出当crc_out_decode_buff=25’h1864cfb与crc_24相等时,计算的结果为0,此时crc_decode_right信号拉高,标志校验结束,crc_decode_wrong与data_repeat信号保持为低。

图9 CRC校验成功实现波形图

通过对程序进行综合、布局布线,将生成的BIT文件加载到硬件平台后能够正常运行,通过ChipScope软件,可以进一步从实际情况验证CRC模块以及码块分割模块的正确性和稳定性。使得该程序设计能够用在实际的开发应用中。

4 总结

本文在采用DSP实现码块分割与CRC添加的基础上,对其在实现的过程中对资源的利用以及处理时间的消耗基础上,提出了采用基于FPGA[9]的CRC校验与码块分割的相关研究,详细地介绍了CRC校验的原理,码块分割及码块CRC添加原理以及各个系统模块之间的通信。经过软件仿真和代码调试对于高层传输的数据信息,FPGA能够正确的进行处理。此设计处理模式已应用于测试仪表系统中,通过实验证明,其工作可靠,达到了设计要求。

[1]3GPP TS 36.212 V9.1.0:Downlink Transport Channels and Control Information(Release9)[S].2010(3):40 -43.

[2]3GPP TS 36.212 V9.1.0:CRC Calculate on(Release 9)[S].2010(3):8 -9.

[3]3GPP TS 36.212 V9.1.0:Code Block Segmentation and Code Block CRC Attachment(Release 9)[S].2010(3):9-10.

[4]沈嘉,索士强,全海洋,等.3GPP长期演进(LTE)技术原理与系统设计[M].北京:人民邮电大学出版社,2008:1-20.

[5]任君玉,黄良玉.TD-SCDMA中CRC算法的研究与设计[J].移动通信,2011(18):51 -53.

[6]金素梅,王家礼.基于 FPGA的 CRC编码器的实现[J].仪器与仪表,2005(24):18 -22.

[7]苏明,姚冬苹.专用异步串口通信电路的FPGA实现[J].物联网技术,2011,5(5):65 -67.

[8]田佳,王一平.基于FPGA的带CRC校验的异步串口通信[J].现代电子技术,2010,33(20):17 -19.

[9]夏宇闻.Verilog数字系统设计教程[M].第2版.北京:北京航空航天大学出版社,2008.

[10]吴厚航.深入浅出玩转FPGA[M].北京:北京航空航天大学出版社,2010:51-52.