说三道四

2012-04-29

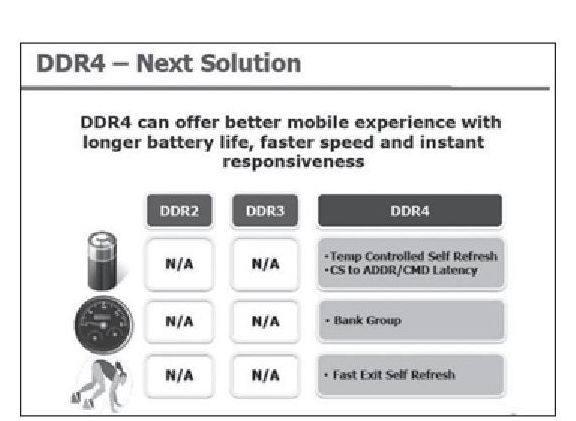

不知不觉,DDR3规格已经统治内存界六年时间了,相比CPU、主板甚至硬盘的升级速度,内存的确有点被遗忘的感觉。而DDR4内存技术标准的发布,在看似平静的内存领域溅起了不少水花……

速度加倍 能耗更低

微电子产业标准机构JEDEC固态技术协会终于发布了下一代同步DDR内存的技术标准:DDR4,它的数据传输速度将比DDR3快一倍,且功耗更低。DDR4的单个内存颗粒容量2Gb-16Gb,同时提供了三种数据宽度x4、x8、x16,最大数据传输速度为3.2Gb/s,不过JETEC说未来随着标准的发展速度还会继续增加。另外DDR4的功耗会更低,将使用1.2V电压而不是DDR3用的1.5V。值得一提的是当前很多移动智能终端都采用了1.2v的低功耗DDR(LPDDR)内存。而下一代产品LPDDR3,将能在现有基础上降低35%至40%的功耗,但它的成本会比DDR4高出40%(LPDDR产品生产成本更为昂贵)。

据目前透露的情况表明,DDR4内存将会拥有Single-endedSignaling信号( 传统SE信号)和DifferentialSignaling( 差分信号技术 )两种规格,对于用户来说,前者传输速率已经被确认为1.6~3.2Gbps,后者传输速率则将可以达到6.4Gbps。

下面,我们将DDR4内存将会采用的技术做了一个整理:

提供三种数据宽度:x4, x8和x16

新的JEDEC POD12接口标准(工作电压1.2V)

DifferentialSignaling( 差分信号技术)

新的终止调度:在DDR4中DQ bus可以转移终止到VDDQ,这样即使在VDD电压降低的情况下也能保证稳定

正常和动态的ODT:改进ODT协议,并且采用新的Park Mode模式可以允许正常终结和动态吸入终结,而不需要去驱动ODT Pin

突发长度和突发停止长度分别为8和4

数据遮掩

DBI:可以降低功耗并且提升数据信号完整性

新的数据总线CRC技术,可以侦测传输过程中的错误侦测,特别对非ECC内存进行写入操作时有帮助

针对命令和地址总线的新的CA奇偶校验

DLL关闭模式支持

服务器内存竞速仅是开始

其实在JEDEC正式公布DDR4技术标准以前,三星早在2011年初便推出了2GB DDR4内存模组,而Hynix海力士(现代旗下)也于同年4月推出了2400MT/s的2GB DDR4,不过这两款“抢跑”的产品均基于30nm和39nm制程工艺,工作电压同为1.2V。业内巨头Intel的再下代企业级服务器平台Haswell-EX才会第一个整合DDR4内存控制器,桌面级方面则要等待2015年左右的14nm工艺新架构“Skylake”了。

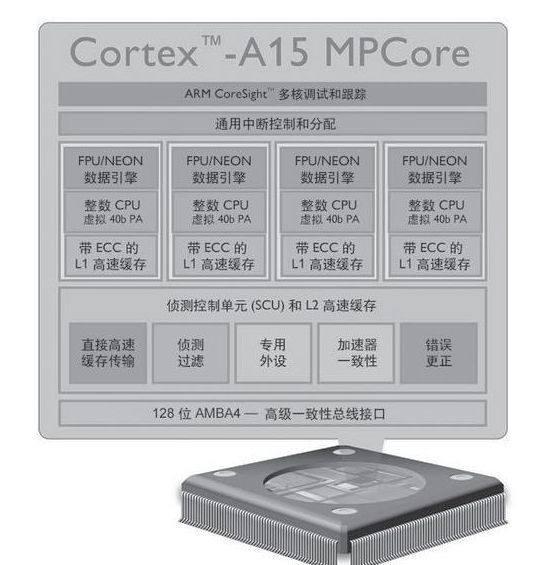

Intel在推进DDR4内存上的慢吞吞引来三星等内存厂商的催促,毕竟从2011年以来,主流PC内存售价一路狂跌,DDR4一定程度上已经成为了内存产业复兴的唯一希望。而在推进DDR4技术普及上,ARM则显得积极得多。作为服务器领域新手,ARM前不久推出了高达16核芯的处理器计划,以应对数据中心越来越高的低功耗以及网络连接需求。名为CCN-504的内核连接技术最多支持16核芯,并且ARM同时发布了内存控制技术DMC-520,可支持未来的DDR4,目前虽然都是28nm制程工艺,不过正努力向20nm工艺推进。

ARM在移动设备领域的强势已经让Intel倍感压力,而在服务器领域对DDR4规格内存的支持上它也领先了Intel一步,借助服务器领域的竞争,相信能有效推动DDR4规格内存普及,或许明年年底,桌面级DDR4内存就可以同大家见面了。