基于数据复制和数字上变频的高速信号的产生

2012-03-15刘章文卢朝政张生帅鲜海鹏

刘章文,卢朝政,张生帅,鲜海鹏

(中国工程物理研究院应用电子学研究所 高功率微波技术实验室,四川 绵阳 621900)

在信号产生技术中,数字信号由于其控制灵活,便于集成等优点已广泛用于现代通信设备、雷达信号产生和科研教学等仪器中。由于受频率精度、稳定度和动态范围的制约,提高数字信号中频率调制速度是难点,也是高速调制信号源的技术瓶颈。直接数字频率合成(DDS)技术具有频率切换快、分辨率高、频率和相位易于控制等特点,广泛用于信号产生技术中[1-2]。存储器数据的复制[3]和IQ数字上变频技术对于基带变到中频,具有非常灵活可调的优势[1-2,4]。本信号产生系统即是对DSP、FPGA、DDS、存储器的数字复制、数字上变频以及微波变频技术的综合集成。

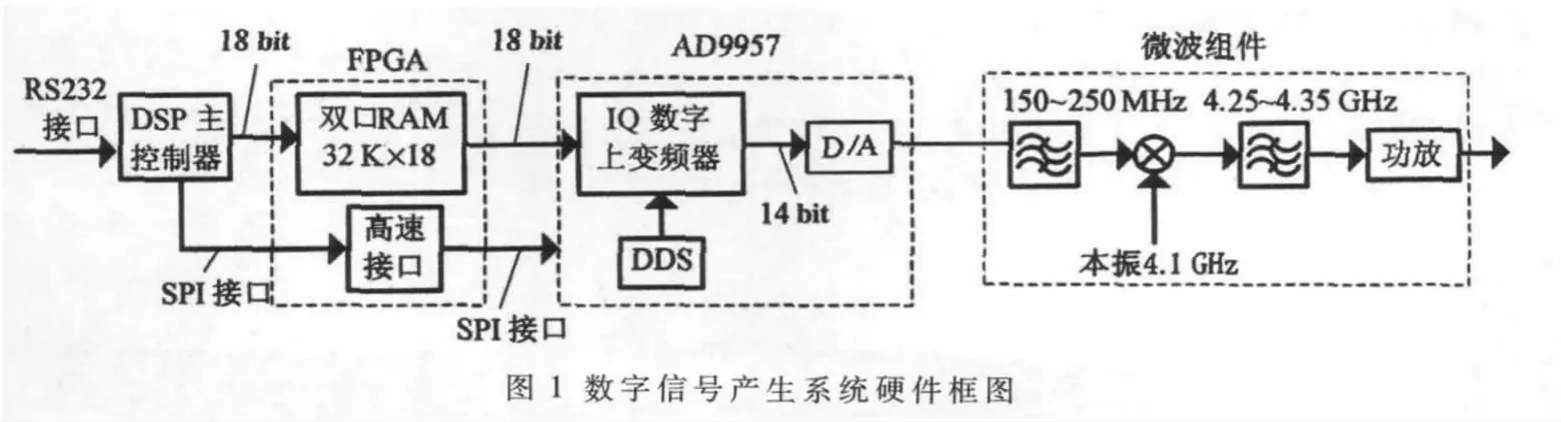

1 系统硬件方案

ADI公司的器件 AD9957内置了 DDS、IQ数字上变频器和刷新率高达1 GHz的14位高速DA,可直接产生最高400 MHz的输出信号,本系统用为上变频芯片。计算和控制采用高速DSP TMS320C6416T;高速接口采用了ALTERA公司的FPGA EP2S30F672I4N,内嵌较大容量的双口RAM,存储器的数据复制即在FPGA中进行。由于输出信号达到更高的微波频段,后端的微波变频组件是必须的。

图1为本系统硬件组成框图,主要由DSP控制器、FPGA高速接口、AD9957数字上变频和后端微波组件四部分组成。DSP控制器负责大量的信号产生所需的计算和对FPGA的数据传输,并对上位机通过RS232接口传来的命令进行解释和执行,通过SPI串口控制AD9957;FPGA高速接口完成高速数据的存储和复制,实现并口和SPI串口的时序管理;AD9957器件完成IQ数字上变频和D/A转换,D/A输出直接到中频,同时可选择地实现sinc滤波功能;后端的微波组件则完成输出信号的上变频和功率放大,以达到4.3 GHz的中心频率的微波频段。

2 系统工作原理

如图1所示,从PC机发向DSP的串口命令包括信号样式、频段码、带宽和频率码等,DSP控制器根据接收到的命令将频率和带宽解析成基带信号相关的参数,并计算出基带信号的18 bit并行数据流,传送给FPGA内部的双口RAM。同时DSP将频段信息通过SPI同步串口送到AD9957,以控制AD9957内的DDS。当DSP完成18 bit并行数据流传到双口RAM后,FPGA则将该RAM内的数据以一固定的高速时钟频率重复地复制输出到AD9957。AD9957将该18 bit数据流分成IQ两路,与内部的DDS一起完成数字上变频,后通过14 bit D/A将该数据流输出中频信号。后端再经过一个4.1 GHz的本振将该信号变到4.3 GHz的微波段。整个信号产生最关键的是基带信号的复制和IQ数字上变频两个过程,同时产生的数据必须作杂散抑制处理,才能获得高分辨的信号。

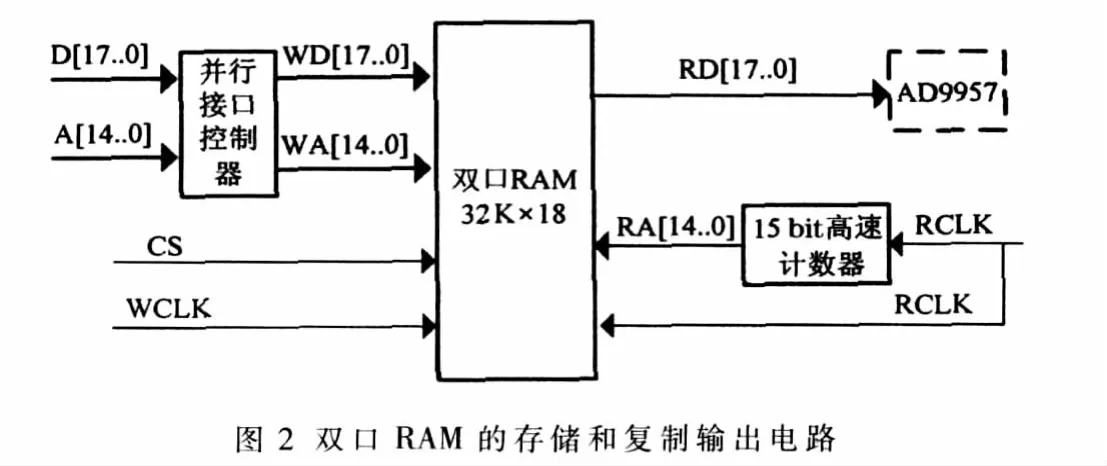

2.1 基带信号的存储与复制

高速18 bit并行数据的存储和复制均在FPGA内部进行,存储器采用FPGA上的同步双口RAM资源ALTSYNCRAM,数据存储和复制电路如图2所示。DSP的计算数据由地址A[14..0]和数据D[17..0]总线通过并行接口控制器、片选CS及写时钟WCLK写入到双口RAM中即完成数据的存储,并行接口控制器主要解决DSP的EMIF外设接口与同步双口RAM之间的时序匹配问题。

信号复制的关键在于读地址发生器,由于读出的数据流要直接形成输出信号,所以对时序要求非常苛刻,读时钟必须同后端的数字变频和D/A时钟严格同步,故图2中的读时钟RCLK来自器件AD9957。读地址由一个高速向上计数器产生,由读时钟RCLK来触发,计数器到顶自动溢出归零并重新向上计数,如此重复往返,即完成信号的复制输出。

由于使用了双口RAM,读写时钟完全独立,写时钟由DSP提供,需要刷新时才写入,所以实时性并不高,减轻了DSP的总线处理难度。而读数据必须实时进行,否则会影响信号产生质量。

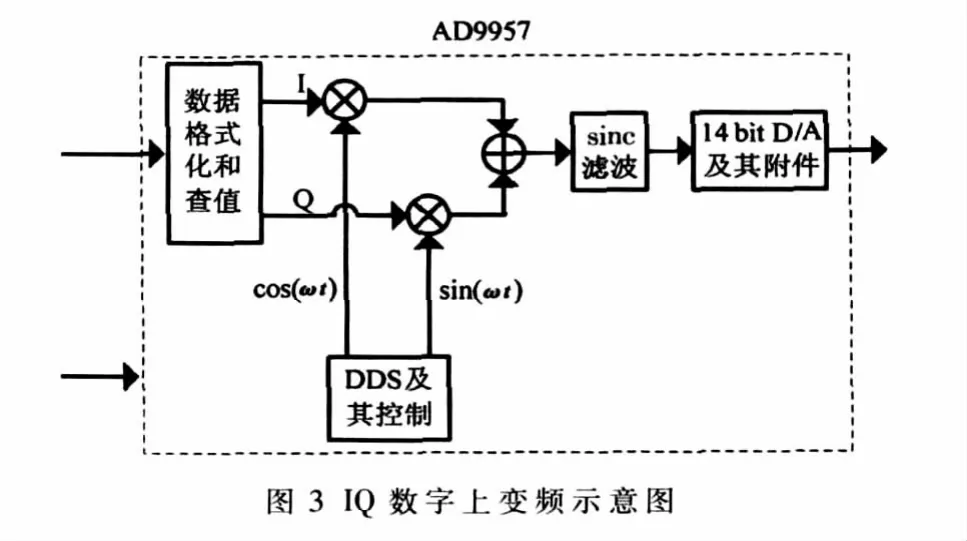

2.2 IQ数字上变频

数字上变频在AD9957中进行[4],同时进行查值、sinc滤波等功能,如图3所示。双口RAM中的数据按I和Q交替存放,AD9957内有一个格式转化器自动将IQ数据流转成独立的I路和Q路。如此,实际基带数据长度N是存储器长度的一半。

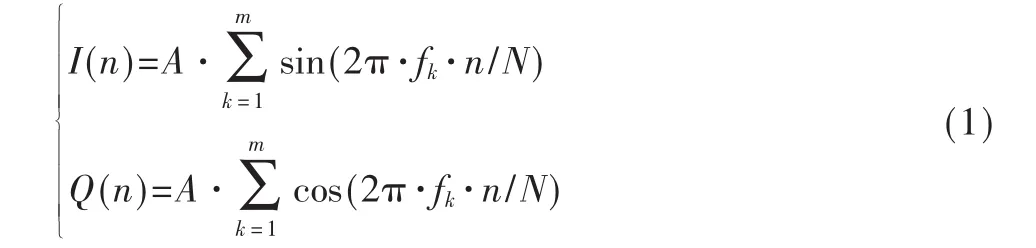

DSP计算出的基带数据表达式为多音信号为:

式中,m为信号载频数,fk为基带信号频率,A是为了把信号映射到18 bit符号数的范围内所加的变换系数。

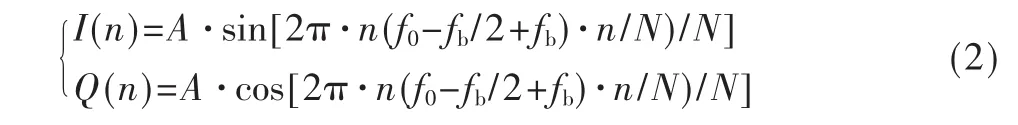

线性调频信号为:

其中,f0是中心频率,fb是带宽。

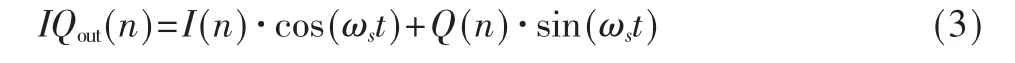

将式(1)、式(2)表示的基带信号与本振进行正交调制IQ变频后相加得

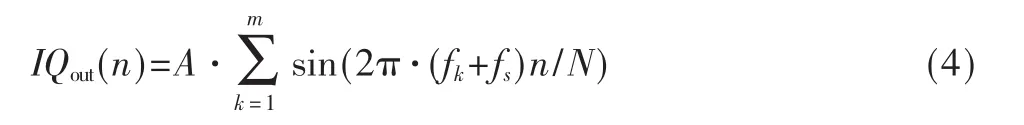

即多音输出为(fs为本振ωs的数字抽样频率,以下同):

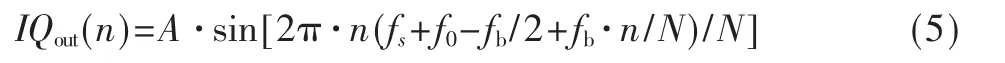

线性调频输出为:

从式(4)、式(5)的输出结果看,所得频率即为基带与本振的叠加,实现了边带数字上变频,而下边带由于IQ调制后相加被相互抵消了。值得一提的是,IQ变频因为在数字域进行,对本振的泄漏非常小,不必考虑IQ两路幅度的不平衡引起的泄漏。因此对DDS可以在其能力范围内任意设置,甚至可以将本振设置到带内,这样在输出频率一定的情况下,本振越高,基带的信号就要求越低,也就是前端并口数据流的速度要求更低一些,相应地减轻了DSP的总线处理难度。从式(4)、式(5)看,IQ调制不存在下边带,即下变频成分。但是实际由于IQ两路不完全对称,仍然存在不同程度的镜像对称频率,这需要设计和调试时充分考虑。

2.3 信号的杂散分析与抑制

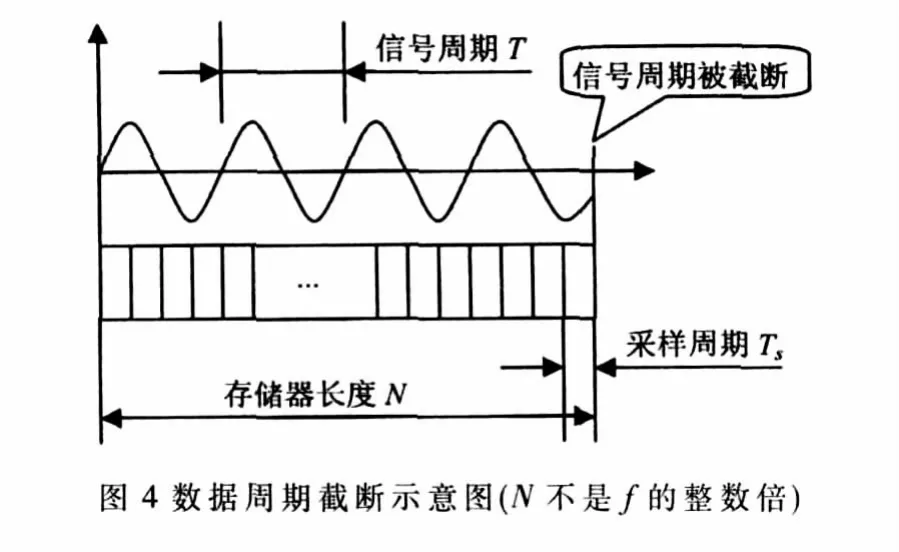

任何数字信号的产生都会存在不同程度的杂散,本系统主要的杂散来源于两个部分,一是数字变频的本振的DDS杂散,尽管DDS具有传统频率合成技术无法比拟的优点,但它的输出杂散较大的缺点严重限制了它的广泛使用[5],如何抑制DDS中输出频谱杂散是另一个研究热点。杂散的另一个来源是由所产生的数据在存储器中的周期截断所引起,由奈奎斯特抽样定理知,存储器长度 N与所产生的频率 f需满足 f<N/2,由于 f在[1,N/2]之间任意设置,大多情况下,N不是f的整数倍,反映在时域上,存储器的数据出现了信号的周期截断,如图4所示。这样出现了一个固有的低频窄带的杂散信号,该杂散信号的强弱和带宽随f的变化而变化,但其中心频率比较固定,并且是调制到有用信号 f上,离 f很近,因此不可能在后端加低通滤波的方法去掉。

为了说明周期截断引起的误差,将存储器分为f的整数段和f的余数段,即:

式中 r、h 均为整数,且 f<N/2,h<f和 M=r·f,于是参考式(1),单音信号I路(Q路类似)可表示为:

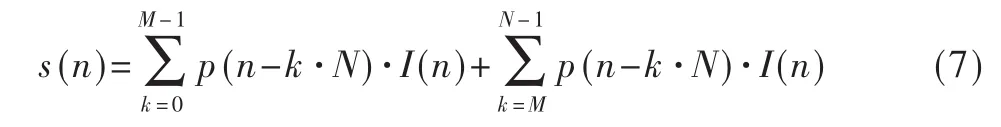

p(n-k·N)为长度为 N的窗函数,I(n)是 I路正弦函数。式(7)前面一项可看成是连续M个数据后补h个0的N个有限数据,后面一项看作是M个0后连续h个数据的N个有限数据,作DFT变换得(注意周期为N)

式(8)的第 1项只有前 M个数,是信号 f的整周期倍,后面h个为0,其积分只有k=nf处有频谱成分,而少了h个数后,只对其幅度有影响。第2项ε(f)完全由于周期截断引起,也是信号的一部分,但它会引起信号的杂散增加,当 N是 f的整数倍时,即 h=0,该项为 0,否则,不为 0,且设定 f时,ε(f±1)大都不为 0,说明周期截断误差是调制在f上且离f很近。

要获得高分辨率的信号,应尽量避免周期截断误差。可以利用数字上变频对本振的不敏感,在本振fs、信号f和存储器长度N之间来进行适当调整,即当输出中频设定,选取合适的 fs和 f,使得 N/2为 f的整数倍,或 N/2对f的余数最小。特别是多音时,不可能对每个f都是整数倍,应使N/2对每个f的所有余数尽量偏小。

3 测试及结论

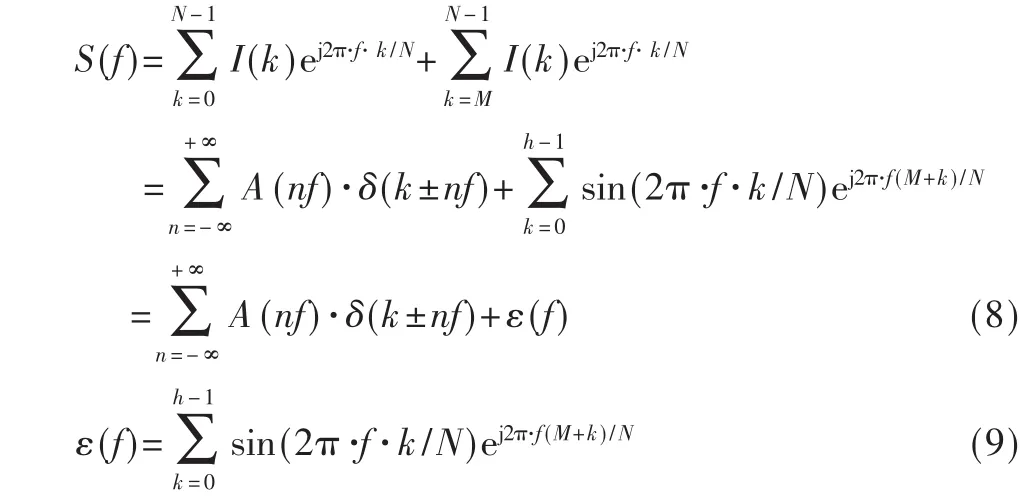

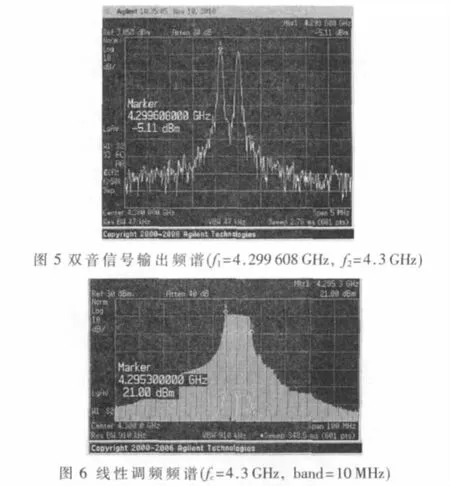

系统硬件按照图1所示的结构进行了制作。对产生的输出信号进行了频谱测量,双音和线性调频的一个例子分别如图5、图6所示。从大量测试的频谱图可以得出,双音信号分辨带宽达到100 kHz以下,信噪比优于40 dB,频率指标均能准确可调;线性调频信噪比优于30 dB,带宽和中心频率都灵活可调,满足使用要求。

本方法实际产生的基带信号带宽50 MHz,即图1中从FPGA到AD9957的并行数据刷新率只需大于100 MHz即可(本方法实际为 225 MHz),数字上变频将 50 MHz基带变到150 MHz~250 MHz的中频范围内。因此从基带到中频,都是数字过程,完全避免了直接用D/A到中频的超高速电路的难度,且变频不需要增加额外的硬件成本。所以存储器的数据复制配合数字上变频技术在高速信号产生中是一种性价比不错的选择。尽管如此,受数字速度的影响,数字变频仍然存在中频不够高的不足,但在实用带宽内,不影响它的选用。

[1]曹义,张春荣,李辉.基于AD9957的多波形雷达信号产生器[J].现代电子技术,2010(3):39-41.

[2]沈志,王宏远,陈少明,等.基于FPGA的 QAM的调制器系统实现[J].电子技术应用,2010,36(1):32-35.

[3]赵书志,潘明海.基于FPGA的数字射频存储器设计[J].电子测量技术,2007,30(2):118-120.

[4]王鹏,杨春,文招金.高速通用数字调制器的设计与实现[J].信息与电子工程,2010,8(3):247-260.

[5]王晓音,聂裕平,庞伟正.DDS输出频谱杂散的抑制[J].电子对抗技术,2003,18(6):25-28.