多标准视频解码器运动补偿存储架构设计

2012-03-15虞礼贞张延军李广桢

曹 超,虞礼贞,张延军,李广桢

(1.南昌大学信息工程学院电子系,江西南昌330031;2.北京理工大学信息与电子学院,北京100081;3.重庆四联微电子有限公司(北京研发部),北京100083)

当前,数字电视机顶盒设计中,主要参考的视频编解码标准包括MPEG-2、H.264以及中国自主研发的AVS;MPEG-2作为广播级的视音频标准已使用很多年;H.264相比其他标准能够在同等图像质量下有更高的压缩相率,因此,它广泛地应用于电视广播实时通信等领域;AVS与H.264相比虽然在性能上没有太大的提高,但是计算复杂度有了明显的下降[1]。国内有线广播主要是采用MPEG-2和H.264,地面广播采用AVS,目前,我国正大力发展农村直播卫星项目,它是利用卫星实现广播电视,多媒体数据直接向用户传送数据(直播卫星节目采用的编码标准是MPEG-2,数字地面广播采用AVS),同时,传统的有线、无线数据传输方式在很长一段时间内仍然是主流(高清节目主要是采用有线传输的MPEG-2和H.264编码标准)。为了满足不同客户对视频节目质量的不同需求,仅仅支持单一的视频编解码标准已难以满足要求,因此,兼容多标准的视频解码芯片将成为高清数字电视机顶盒芯片设计的必然趋势,这种视频解码芯片主要有以下3个特点:1)支持主流的视频编解码标准,包括MPEG-2,H.264,AVS(综合考虑成本与性能,在国内兼容这3种标准的机顶盒能够满足高清视频解码芯片设计要求,而不必兼容于更多的视频编解码标准,如:在国际上一些地区使用的用于广播的编解码标准VC-1);2)软硬件配合工作,固件Firmware可更新,以便于针对市场变化需求进行升级;3)支持通用的接口,易于系统集成化。本设计主要应用于中国直播星DTH项目以及高清卫星机顶盒应用。

在高清视频编解码设计中,基于硬件的实现技术已变的越来越重要,特别是在需要高效率执行、低功耗要求中。运动补偿(Motion Compensation)模块是视频解码器设计模块中访问存储器最频繁,且数据吞吐量最高的模块。为了解决存储器带宽的限制,文献[2]中提出了一种支持H.264的MC子系统,但是它不兼容于AVS;文献[3]中使用了Cache机制来降低访问外部存储器带宽,但当多种预测方式被请求时,就会减少Cache的命中效率。为解决这些问题,本设计中采用数据缓存机制用于减少对外部存储单元的频繁访问;另外,外部存储器单元SDRAM分配6帧高清帧存储空间,存储用于运动补偿计算的相关帧与重构帧,帧存储在SDRAM中采用顶底场数据分开方式,采用这种方式能够提高数据的存取效率。整个运动补偿计算模块采用并行多级流水线设计,减少了运动补偿的计算周期,提高了执行效率,使用90 nm COMS工艺库,在135 MHz的频率下综合,电路规模为45 kgate,处理一宏块数据大约需要520个时钟周期,文中设计能够应用于MPEG-2 MP@HL,H.264MP@L40 以及AVS Jizhun Profile。

1 运动补偿计算模块整体架构

在运动补偿计算过程中,首先,需要接收来自于VLD(Variable Length Decoding)模块解码的运动矢量;然后根据当前模块的数据分割以及运动矢量信息,从外部的存储器参考帧中读取相应的参考像素;再通过像素插补等一系列计算,最后得到重构的像素数据。对于MPEG-2,像素插补只是在半像素位置进行双线性差值;对于AVS,在半像素位置采用4抽头滤波器F1(-1,5,5,-1),在四分之一像素位置采用4抽头的滤波器F2(1,7,7,1);而H.264/AVC在半像素位置采用6抽头滤波器F3(1,-5,20,20,-5,1)。运动补偿模块整体结构如图1所示,包括用于得到重构数据的运动补偿像素插补模块单元,用于取相关数据的外部存储器接口单元以及一些控制计算单元(包括总线判决器和DMA控制器等)。外部存储器接口单元处于运动补偿像素插补模块与总线判决器模块之间,此模块接收来自于运动补偿像素插补单元的请求,用于控制运动补偿像素插补单元取相关数据;如果相关数据不存在于逻辑缓存器子模块中,那么外部存储器接口模块将发送请求给总线判决器用于从外部的SDRAM中读取相关数据,请求返回的数据将存储在逻辑缓存器单元中,同时相关数据将被传送给运动补偿像素插补单元;若运动补偿像素插补单元请求的相关数据存在于逻辑缓存器单元中,相关数据将从逻辑缓存器单元中直接传递给运动补偿像素插补单元而不访问外部的SDRAM。

图1 运动补偿计算模块整体结构

2 数据存储器优化

本文中提出了一种插补像素缓存机制,用于存储像素插补计算过程中的中间数据,对于那些反复被使用的参考像素存放在外部存储器接口单元中的缓存器Buffer中,完整的参考帧则存放在外部存储器SDRAM中,通过这种数据Buffer机制能够很好地提高运动补偿的性能,减少计算周期,运动补偿存储器架构如图2所示。

图2 运动补偿存储器架构

滤波中间值缓存器用于存放运动补偿计算过程中的中间值。由于这个滤波中间值缓存器只是用于存储像素插补流水的中间值,因此,它只是与像素插补计算单元有数据的交换。外部存储器接口单元内部结构框图见图3所示,主要是用于执行3部分请求响应:1)从运动补偿像素插补模块加载来自于相关Buffer的数据;2)发送请求信号给总线判决器;3)将返回的数据存储到逻辑缓存Buffer中。整个外部存储器接口单元包括以下几个子模块:亮度数据请求地址模块、色度数据请求地址模块、2k亮度数据Buffer、1k色度数据Buffer、亮度数据hit模块、色度数据hit模块,以及存储器请求发送FIFO、存储器访问FIFO。整个模块采用并行多级流水线方式,可以同时处理亮度和色度的取相关数据操作。

图3 外部存储器接口模块单元框图

通过这种存储器结构设计,能够减少对外部存储器频繁的访问。这样,虽然片内的存储器功耗略有增加,但是对于外部的存储器以及I/O接口的功耗能够大大地减少,表1是通过对20个QCIF视频序列功耗仿真测试的结果,结果表明存储器Buffer机制平均能够减少42%的系统功耗。

表1 存储器缓存机制优化

3 像素插补计算

3.1 亮度计算

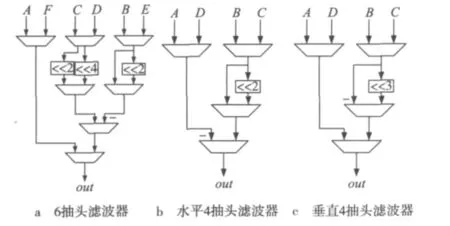

在亮度像素插补计算中,需要使用3种滤波器:2种4抽头滤波器 F1(-1,5,5,-1)和 F2(1,7,7,1),用于 AVS亮度像素插补计算;1个6抽头的滤波器F3(1,-5,20,20,-5,1),用于H.264/AVC的亮度像素插补计算。1个6阶的滤波器直接计算需要5个加法器和4个乘法器,但是通过简单的操作数组合能够将资源消耗减少到2个乘法器,即out=(A+F)-5×(B+E)+20×(C+D)。6抽头滤波器如图4a所示,设计中使用移位器和加法器组合来实现乘法器功能,因此1个6抽头滤波器需要使用7个加法器和3个移位器实现。对于2个4抽头滤波器,可采用类似6抽头的设计方式,水平滤波为out=-(A+D)+5×(B+C);垂直滤波为out=(A+D)+7×(B+C)。这样2个4抽头滤波器能够分别使用4个加法器和1个移位器实现,如图4b、图4c所示。

图4 3种滤波器设计实现

以文献[4]图8-4中j点像素插补为例,对一个4×4块进行像素插补计算。图5描述了H.264解码流水线过程。在流水线第1周期,使用4个水平和4个垂直滤波器分别对参考像素进行计算,输出结果存放在滤波中间值缓存器中;在第2周期,水平和垂直滤波窗口分别向右移动一格,对4×4块第2列数进行垂直插补,并且开始执行均值滤波,这样通过6个时钟周期,就能够得到计算j像素点的6个半像素参考点,所以,计算一个j参考像素需要9个时钟周期。表2总结了在H.264/AVC中插值计算一个4×4亮度像素块不同像素位置所需时钟周期(各像素点代表文献[4]中图8-4所示的位置)。

图5 亮度计算流水线设计

表2 4×4亮度块相应像素点计算周期

3.2 色度计算

对于色度计算来说,AVS与H.264/AVC可采用类似的计算方法,相比亮度计算,色度计算相对直接。插值按照以下公式完成

因此,色度滤波器可设计为如图6所示,与原始设计相比,该设计需要11个加法器、4个固定长移位器以及3个可配置移位器就能实现,减少了大量的乘法器消耗。

图6 色度滤波器

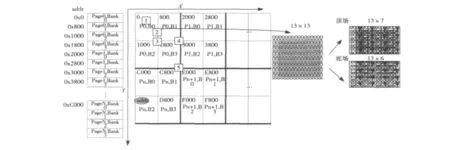

3.3 Page/Bank地址结构

外部SDRAM采用Page/Bank存储方式用于存储6帧高清图存储空间(满足IBBBBP编码方式),设计中采用顶底场分开的方式将数据存储在SDRAM中,如图7所示。对于亮度数据来说,每一页分为4个Bank的存储空间能够存储64宏块的亮度数据,这样,每个Bank能够存储4×4=16个宏块的数据,读/写访问每个时钟周期能够读取4 pixel×2的数据,采用此种数据分割模式,能够产生最优化的数据加载能力[5]。图7中1~5标示了取值模块在不同的Page/Bank中的位置,取值模块1所耗费的时钟周期最短,而由于取值模块5跨4个Bank取值,因此,所需的时钟周期最长。例如:当考虑到一个13×13像素的取数据操作时,读取方式如图7所示,其中阴影部分为所需要取得的数据,黑色箭头表示每个时钟周期所取像素。采用这种取相关数据方式,每个时钟周期能够取得8像素数据,这种架构能够有效地减少访问外部SDRAM的precharge/active的频率(每个precharge/active需要消耗2~5个时钟周期),从而能够提高运动补偿计算的性能。

图7 Page/Bank存储方式以及取亮度数据示意图

4 综合结果比较

采用文中所提出的设计方法,用Verilog语言进行RTL级描述,开发环境为QuartusII 10.2,使用Altera公司的Stratix II系列芯片EP2S90F1020C4,在时钟频率为135 MHz的情况下,使用资源为:4 590个ALUT;4 017个寄存器。建立的C模型是基于AVS验证模型RM09.10,H.264相关软件JM12.1以及MPEG-2相关的模型v1.2a。通过测试3种不同标准的码流,使用Synopsys Design Compiler综合结果显示,该Verilog代码能够满足MC功能。表3中描述采用文中Buffer缓存机制,AVS码流测试所节省的带宽,结果表明采用文中设计Buffer能够平均节省37.47%的带宽消耗。

表3 AVS测试Buffer性能

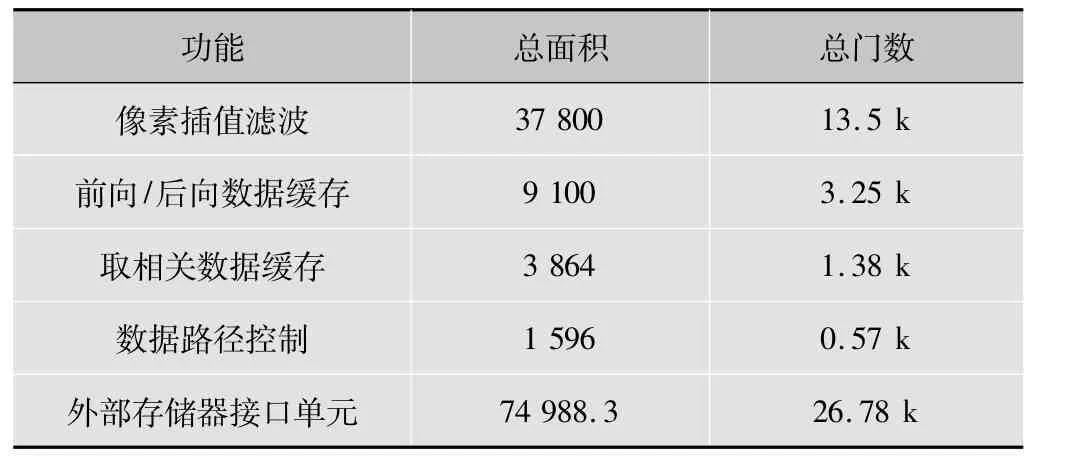

Synopsys Design Compiler下,使用0.09 μm CMOS 工艺库综合,在工作频率为135 MHz下,除去外部的存储单元SDRAM运动补偿计算模块总共消耗45.48 kgate(运动补偿像素插补计算单元与外部存储器接口单元总和),执行1 Mbyte的MC计算(运动补偿像素插补计算,不包括从外部SDRAM中取相关数据),需要消耗大约520个时钟周期,相比文献[6]减少了大约15%的时钟周期,MC计算单元资源消耗情况及与文献[6-7]比较见表4、表5所示,结果表明,该设计满足实时高清解码要求(30 f/s)。

表4 文中设计所耗资源

表5 MC计算单元资源与文献[6-7]性能比较

5 小结

本文提出了一种满足多标准视频解码的运动补偿存储架构,外部存储器SDRAM存储6帧HD图,每一帧图采用顶底场数据分开的方式存储在SDRAM中,整个MC单元采用并行多级流水线处理,实现了对外部帧存储单元的高效存取访问以及运动补偿的高效计算,处理1 Mbyte的MC操作需要大约520个时钟周期,相比文献[6]节省了15%。综合结果表明,本设计满足高清视频解码的要求。

[1]Document JVT-C167.Draft ITU-T recommendation H.264(a.k.a"H.26L")[S].2002.

[2]WANG S Z,LIN T A,LIU T M,et al.A new motion compensation design for H.264/AVC decoder[C]//Proc.IEEE International Symposium on Circuits and Systems,2005.[S.l.]:IEEE Press,2005:4558-4561.

[3]KIM J H,HYUN G H,LEE H J.Cache organizations for H.264/AVC motion compensation[C]//Proc.13th IEEE International Conference on RTCSA,2007.[S.l.]:IEEE Press,2007:534-541.

[4]ITU-T H.264建议书[S].2005.

[5]LIN C F,CHUNG C C,TSAI Y C,et al.Bandwidth-efficient architecture design for motion compensation in H.264/AVC decoder[C]//Proc.10th IEEE International Conference on Solid-State and Integrated Circuit Technology,2010.[S.l.]:IEEE Press,2010:445-447.

[6]ZHENG Junhao,GAO Wen,WU D,et al.A novel VLSI architecture of motion compensation for multiple standards[J].IEEE Trans.Consumer Electronics,2008,54(2):687-694.

[7]TSAI C Y,CHEN T C,CHEN T W,et al.Bandwidth optimized motion compensation hardware design for H.264 HDTV decoder[C]//Proc.48th Midwest Symposium on Circuits and Systems,2005.[S.l.]:IEEE Press,2005,2:1199-1202.