IEC61850-9-2标准下合并单元的研制

2012-03-07田丽平

田丽平

(华东交通大学电气与电子工程学院,江西南昌 330013)

IEC61850-9-2标准下合并单元的研制

田丽平

(华东交通大学电气与电子工程学院,江西南昌 330013)

针对当前合并单元的研究现状,分析了合并单元的采样值映射模型IEC61850-9-2及其实现方法,在此基础上设计了一种基于现场可编程门阵列(FPGA)的合并单元装置。该装置通过在FPGA芯片上配置NiosII软核处理器和相关接口,完成合并单元同步、多路数据接收和处理以及以太网通信等功能,能满足电子式互感器数字接口的要求。

IEC61850-9-2;合并单元;FPGA

数字化变电站建设是当前电力建设的一个热点。但在进行传统变电站数字化改造的过程中,亦或是新建的数字化变电站中,在过程层网络采用的是IEC61850-9-1标准或是IEC60044-8协议,并未真正意义上实现数字化。随着以太网技术的发展,变电站过程层、间隔层以及站控层将逐渐实现总线化,合并单元作为过程层的核心设备,采用IEC61850-9-2标准,实现互感器或合并单元与间隔层设备的数字化连接,将势在必行。

1 合并单元的研究现状

合并单元主要实现变电站电流、电压等模拟量数据的同步采集,经合并处理后,按IEC 61850标准规定的通信规约进行应用数据单元(APDU)组帧并通过以太网实时发出,供给间隔层设备使用。

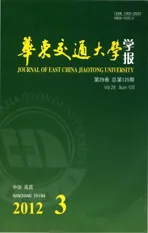

合并单元的定义(merging unit,MU)首次在IEC60044-8标准中提出,如图1所示,标准中对数字输出规定的典型做法是将7个电流和5个电压的二次变换器组成一个合并单元,然后组成以太网信息帧发送给二次保护、测控设备。

随后颁布的IEC61850-9-1/2标准[1-2]对合并单元的通信方式做了进一步定义,通过串行单向多路点对点和基于过程总线的特殊通信服务映射(SCSM)实现采样值的传输,增强了采样值传输模型映射的完备性。

图1 合并单元模型Fig.1 Model of merging unit

当前国内研究的合并单元大多是基于IEC61850-9-1标准或是IEC60044-8协议,采用专用数据集,帧格式固定,输入通道为12路,不允许改变。表1分析比较了3种标准的合并单元,从表1可以看出,IEC61850-9-1部分遵循了IEC60044-7/8标准对合并单元的设定,只支持采样值报文传输(SendMSVMessage)服务,不支持采样值控制块读/采样值控制块写(GetMSVCBValues/SetMSVCBValues)等控制服务,映射方法相对固定、简单,比较容易实现。目前,IEC TC57 WG10正在制定IEC 61850系列标准第2版,撤消了FT3帧格式及IEC 61850-9-1,推荐使用IEC 61850-9-2[3]。

表1 合并单元比较Tab.1 Comparison of merging unit

IEC61850-9-2由于具有众多优势而被国外厂家大力推广,国内也正在紧锣密鼓的对基于IEC61850-9-2的合并单元进行研究。但由于IEC61850-9-2涉及比较复杂的制造报文规范(MMS)协议,同时对通信网络性能有很高的要求,目前有一定的实现难度。为此,IEC委员会专门出版了针对9-2的LightEdition,专门针对9-2的应用提供了指导,并对一些参数进行了固化[4-5]。随着数字化变电站建设的进程,IEC61850-9-2标准下合并单元的研究迫在眉睫。

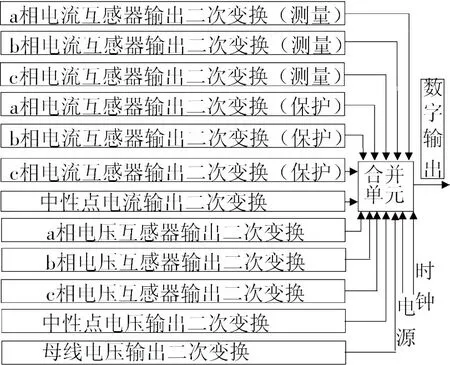

基于以上情况,利用FPGA丰富的I/O口和快速计算能力等优势[6]实现合并单元的所有功能,功能结构如图2所示,其中,FT3为帧格式;1PPS为秒脉冲;GOOSE为面向通用对象的变电站事件。

2 合并单元映射实现

图2 合并单元功能结构框图Fig.2 Frame figure of merging unit

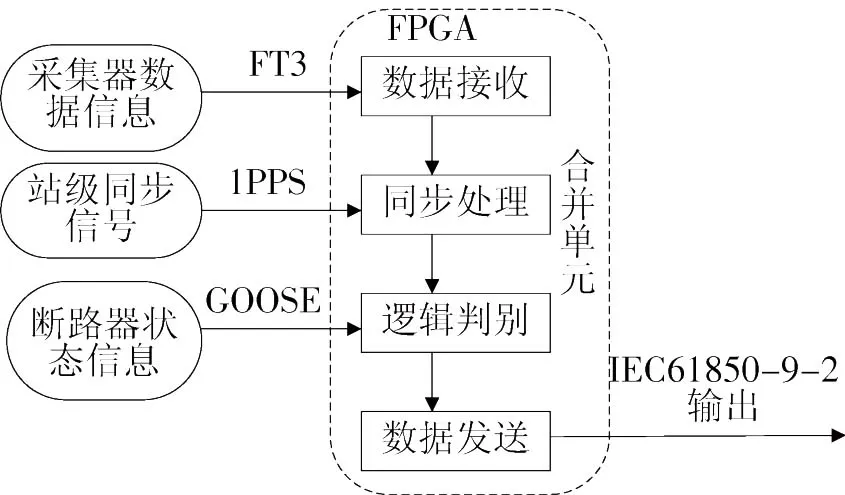

IEC61850-9-2规定了间隔层和过程层之间通信的特定通信服务映射SCSM,除了支持映射到数据链路层,还支持制造报文协议MMS的映射。从图3可以看出,采样值传输作为一种快速报文传输服务,直接由SendMSVMessage服务被映射到了以太网链路层,保证了数据传输的实时性快速性的要求。虽然IEC61850-9-2支持向MMS映射,但由于MMS的复杂性,一般在合并单元暂不进行实现,目前暂时考虑实现“SendMSVMessage”服务。其中SMV为采样值。

IEC61850-9-2采样值应用协议数据单元(AP⁃DU)采用与基本编码规则(BER)相关的ASN.1语法对通过ISO/IEC8802-3传输的采样值信息进行编码。

图3 采样值模型特定通信服务映射Fig.3 Specific communication service mapping of the sample value model

3 合并单元功能分析及系统总体方案

合并单元是电子式互感器接口的重要组成部分,主要功能是同步采集多路电子式电压互感器(ECT),电子式电流互感器(EVT)输出的数字信号后按照标准规定的格式发送给保护、测控设备。

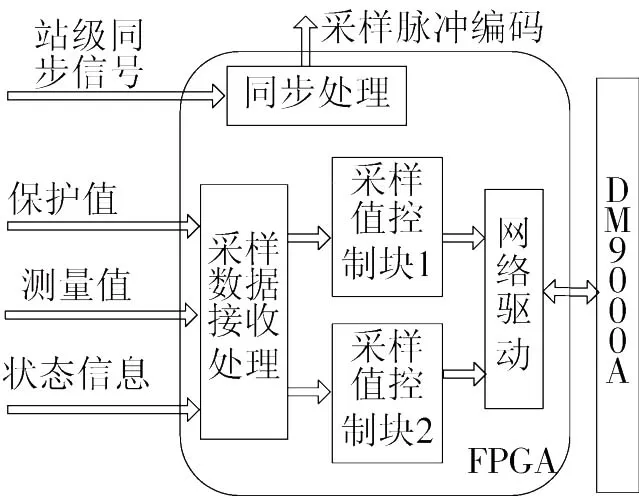

根据系统需要,由于合并单元同时处理的数据量非常大,这就要求硬件系统必须具备快速处理信号的能力,而且还要有大规模的存储设备来存储这些数据,更需要完善的通信网络来实现信息的交互。大规模集成电路FPGA具有集成度高,开发灵活,功能强大等优点,利用FPGA硬件优势,选用Altera公司32位Nios II CPU软核的FPGA作为核心模块,实现合并单元的所用功能,其硬件系统结构如图4所示。IEC60044规定互感器的测量值和保护值精度要求不同,因此,在设计时使用两个采样值控制块及相应的通信服务分别控制测量值和保护值传输,如图4所示。通信系统由以太网控制器DM9000A完成。

4 合并单元功能的实现

图4 合并单元硬件结构Fig.4 Hardware structure of merging unit

设计中,分以下4个模块实现合并单元的功能。

4.1 同步模块

时钟同步系统是数字化变电站建设中的关键环节。合并单元同步功能的实质是实现电流、电压的采样同步,它包括:①接收校验同步信号;②向采样设备发送同步信号;③同步信号异常处理[7-8]。

IEC61850标准定义了3个等级的采样值同步准确度:T3,T4和T5。T3等级要求为25 μs,用于配电线路保护;T4等级要求为4 μs,用于输电线路保护;T5等级要求为1 μs,用于计量[2]。过程层采样值要求最高,同步精度达到亚微秒级。目前的同步方案一般采用站内统一的GPS时钟信号,通过脉冲对时网和通信网络,给需要时间标签的合并单元、互感器等设备对时,此方案满足不了T5等级的要求,所以需要对其进行分频。利用FPGA内嵌的锁相环(PLL)技术对时钟信号进行分频[9]。

设计中,FPGA的全局时钟管脚作为GPS接收信号输入端,对GPS信号进行可靠识别,确认正确后,准备发送采样信号给各路A/D;如果GPS信号异常,FPGA需要一边发出告警信号,启用备用同步信号,一边实时跟踪GPS信号何时恢复正常,若恢复正常后,能够马上启用GPS信号。

4.2 数据接收模块

数据接收模块的任务之一是对各通道数据的接收和校验,任务之二是对各通道数据排序。下面主要对数据通道排序模块进行介绍。虽然采用了同步信号进行数据采集,但是数据在传递过程中的具体情况不同,以致到达合并单元的顺序不同,因此需要利用FPGA的先入先出队列(FIFO)来完成此功能。FIFO存储器是按先入先出的秩序对数据进行存储和读取,即在写入第k-1路数据后再写入第k路数据。实现过程:数据校验无误后,由write_data模块将数据写入FIFO,当写满一个采集包时,通知read_data模块读取数据。另外,为保证系统正常运行,需要设置一计数器time_over,当某路数据故障无法到达时,time_over模块设置一最大等待时间[10],如果超时,该路数据输入为0,等待接收下一路数据。

4.3 逻辑判别模块

合并单元对断路器、刀闸状态的GOOSE信息,进行逻辑判别,从而选择合适电子式电压互感器的电压送至间隔层的保护、测控和计量等智能电子设备,并在故障时发送告警信息。

4.4 数据发送模块

各路数据接收完成后,将它们按IEC61850-9-2标准规定进行信息封装组帧通过以太网实时发出。采样值包括保护值和测量值,IEC61850规定两者的采样频率不同,在发送时两者是互斥的访问以太网控制器,如果两种数据同时发送时,为保证保护值的时延最小,算法需优先发送保护值。DM9000A内部有16 KB的SRAM用来作为收发数据的缓冲区,可以同时保存2个完整的以太网帧,设计时将发送缓冲区看作2个独立发送缓存区,可分别标记为index I和index II。采样值发送过程如下:

FPGA首先将要发送的一帧数据写入index I中,启动发送该帧数据,DM9000A对数据组帧后,开始发送。在发送数据的同时,下一帧数据将写入index II中,当index I中的数据发送完成后,启动网络控制器发送index II中的数据,同时将要发送的下一帧数据写入index I。在程序中可以通过检测网络状态寄存器NSR判断哪个缓存区中的数据发送完毕。通过对这两个发送缓存区进行如此轮流操作,从而有效的避免了处理器的等待时间,提高数据发送的效率和速度。实际中为了提高效率,也可以采用中断方式发送数据。

5 结束语

合并单元作为数字化变电站过程怪的核心装置,针对合并单元的研究现状,遵循IEC 61850-9-2标准,采用单机片FPGA实现合并单元的所有功能。该方案硬件电路简单,选择性灵活,保证数字化变电站过程层和间隔层信息交换的可靠性和实时性,同时也为实现变电站数字化提供了支持。

[1]李永宙,李风.IEC 61850第2版简介及其在智能电网中的应用展望[J].电网技术,2010,34(4):11-16.

[2] IEC 61850 Communication Networks and Systems in Substations[EB/OL].(2005-10-23)[2012-01-16].http://scl-validator.erlm.siemens.de/validator/upload.html.

[3]胡国,唐成虹,徐子安,等.数字化变电站新型合并单元的研制[J].电力系统自动化,2010,34(24):51-54.

[4]何卫,王永福,缪文贵.IEC 61850深层次互操作试验方案[J].电力系统自动化,2007,31(6):103-107.

[5]樊陈,吕晓荣,高春雷.基于IEC 61850过程层总线合并单元的研究[J].江苏电机工程,2010,29(2):25-29.

[6]陈小毛,陈尚松.32位软核处理器NIOS II的以太网接口设计与实现[J].电子测量技术,2007,30(1):150-151.

[7]刘琨,周有庆,张午阳,等.电子式互感器合并单元时间同步问题的解决方法[J].电力系统通讯,2006,27(161):71-75.

[8]殷志良,刘万顺,杨奇逊,等.一种遵循IEC61850标准的合并单元同步的实现新方法[J].电力系统自动化,2004,28(11):57-61.

[9]李红斌,余春雨.电子式互感器数字输出的研究[J].高电压技术,2004,30(2):10-11.

[10]姚静,郑建勇,梅军,等.基于FPGA的合并单元数据接收及处理模块的实现[J].电工电气,2009(7):14-18.

AResearch on Merging Unit Based on IEC61850-9-2

Tian Liping

(School of Electrical and Electronic Engineering,East China Jiaotong University,Nanchang 330013,China)

Aiming at the current research situation of the merging unit,the value of the merging sampling unit mapping model IEC61850-9-2 and its implementation are analyzed.A merging unit based on FPGA is designed.This device realizes the functions of merging unit synchronization,multi-channels acquisition,and Ethernet communication by configuring NiosII soft core CPU and some modules on a PFGA.This method can fulfill the requirements of reliability for electronic transducer.

IEC61850-9-2;merging unit;FPGA

TM45

A

1005-0523(2012)03-0036-04

2012-02-13

华东交通大学科研项目(10DQ03)

田丽平(1981-),女,硕士,研究方向为变电站综合自动化。