基于IEEE 1588的智能变电站时钟同步技术研究

2012-02-21王水鱼魏传均

王水鱼,魏传均

(西安理工大学 自动化与信息工程学院,陕西 西安 710048)

近年来,智能电网成为世界范围内电力系统的发展方向,智能变电站得到广泛的应用和推广,采用智能设备实现了全站信息数字化、通信平台网络化、信息共享标准化。同步对时系统是智能变电站中的重要环节,数字化变电站间隔层的保护装置、测控装置,尤其是过程层的合并单元均离不开同步对时信息,保证数字化变电站各设备的精确同步是数字化变电站稳定运行的重要基础。IEC 61850标准对智能电子设备 (IED)的时钟精度按功能要求划分为5个等级(T1~T5),其中用于计量的 T5 等 级精度达到 1 μs[1]。IEEE 1588全称为网络测量与控制系统的精密时间同步协议,简称为精密时间同步协议PTP(Precision Time Protocol),具有容易配置、快速收敛以及对网络带宽和资源消耗少等优点。经过完善的IEEE 1588标准(第2版)在 2008年已发布。在硬件辅助条件下,其时间同步精度可达到亚微秒量级,可满足T5等级同步精度 1 μs的要求,IEEE 1588是智能变电站对时系统的必然趋势[1-2]。

1 IEEE 1588对时原理及时钟结构

1.1 IEEE 1588对时原理

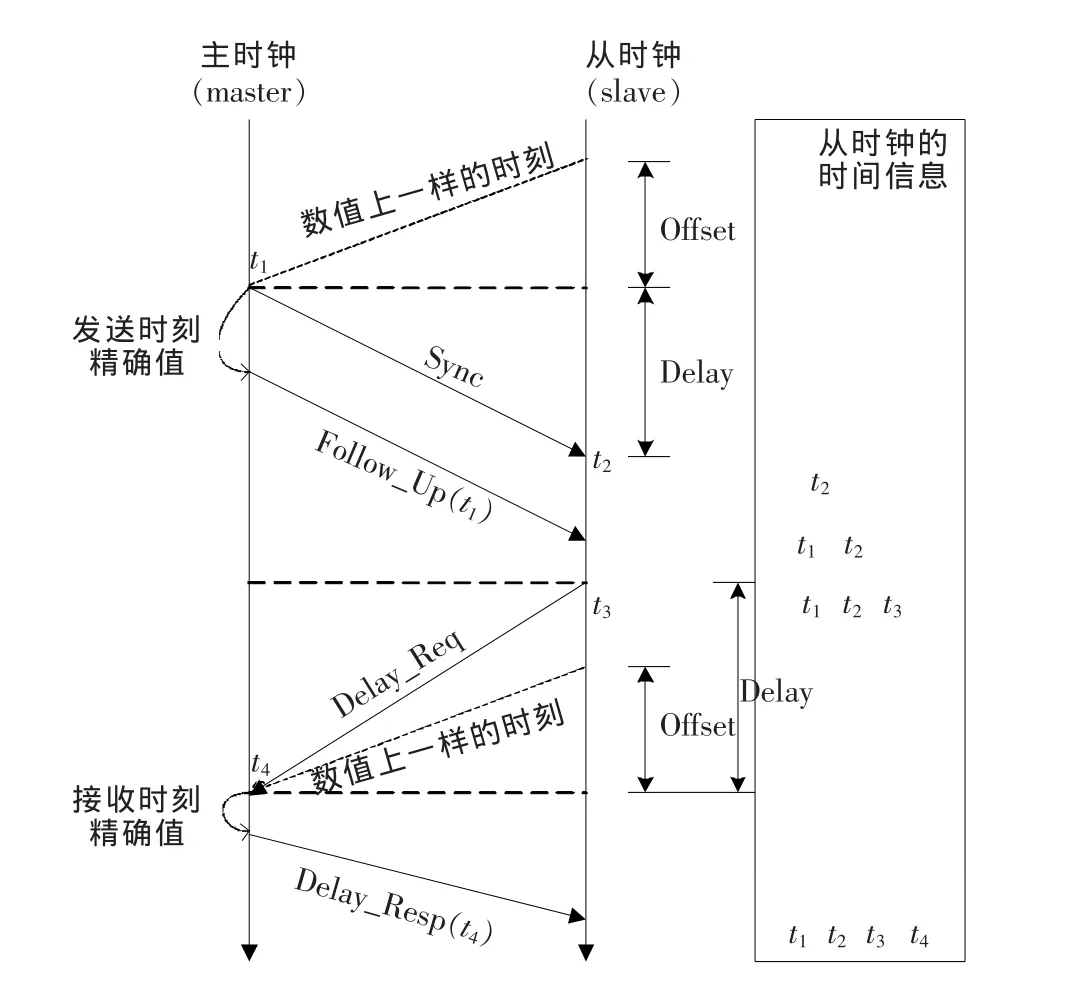

IEEE 1588协议采用分层主从 (Master-Slave)模式进行时钟同步,从时钟通过必要的时间信息实现与主时钟的同步。IEEE 1588协议主要定义了4种多点传送的时钟报文类型:同步报文(Sync)、跟随报文(Follow_Up)、时 延 请 求 报 文 (Delay_Req)、 时 延 请 求 响 应 报 文(Delay_Resp)。通过测量主从时钟之间的时间偏差和网络时延来实现同步功能。IEEE 1588主从时钟同步机制如图 1所示[1-2]。

IEEE 1588从时钟与主时钟同步的过程如下:

(1)首先主时钟以多播形式周期性(一般间隔 2 s)地向所有相连的从时钟发送Sync报文,并在介质独立接口 MII(Media Independent Interface)处加盖 Sync报文发送的硬件时间戳。

(2)从时钟接收Sync报文。并在以太网MII处产生一个基于从时钟的本地时间戳t2,即收到Sync报文的精确时间。

图1 IEEE 1588同步原理

(3)主时钟通过读取 Sync的硬件时间戳信息,得到Sync报文基于主时钟的精确发送时刻t1,将其插入Follow_up报文中发送给从时钟,从时钟便能获取Sync报文的精确发送时间t1。

(4)随后从时钟向主时钟发送Delay_Req报文(一般4~60 s发送一次),并记录Delay_Req报文基于从时钟的精确发送时刻t3。

(5)主时钟接收 Delay_Req报文,并记录 Delay_Req报文基于主时钟的精确接收时刻t4。

(6)主时钟把Delay_Req报文的精确接收时刻t4插入Delay_Resp报文中,并发送给从时钟[1-2]。

通过这种“乒乓”方式,由此可计算出主从时钟之间的时间偏差Offset和网络延时Delay。假设通信路径网络时延是对称的,则Follow_Up报文的精确接收时间t2和Delay_Req报文的精确接收时间t4分别为:

由式(1)、式(2)得:

Offset=[(t2-t1)-(t4-t3)]/2 Delay=[(t2-t1)+(t4-t3)]/2

因此,从终端可以通过计算得到主从时钟之间的Offset和Delay,并据此调整本地时钟,完成一次时间同步。

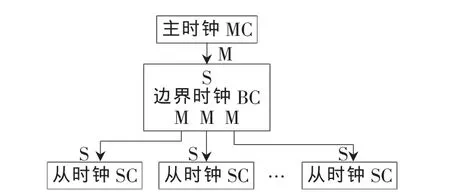

1.2 PTP系统时钟结构

PTP系统中的时钟在结构上分为普通时钟OC(Ordinary Clock)、边界时钟 BC(Boundary Clock)和透明时钟TC(Transparent Clock)。主时钟与从时钟只有一个时钟端口为普通时钟OC,而边界时钟包含一个从时钟端口和多个主时钟端口。交换机时钟模型为TC,合并单元、保护测控等装置的时钟模型为OC,运行在从时钟状态,边界时钟将同步过程分段进行,体现了逐级同步的思想[4]。PTP时钟组织拓扑结构如图2所示。

图2 PTP时钟组织拓扑结构

数字化变电站PTP同步对时系统结构如图3所示。其特点如下:主时钟a和主时钟b互为备用;正常状态下只有一台活动主时钟,另一台处于静默状态,此机制通过最佳主时钟BMC(Best Master Clock)算法实现;PTP交换机TC需根据BMC算法选择主时钟同步频率;IED(OC)跟随当前活动主时钟。在主时钟发生切换时,守时等待切换完成,并根据BMC算法选择主时钟。

图3 数字化变电站PTP同步对时系统

2 IEEE 1588对时系统分析及实现

2.1 PTP的最佳主时钟(BMC)算法

一套IEEE 1588系统由许多设备(节点)组成,每个设备都有自己的时钟系统,理论上任何时钟都能实现主时钟和从时钟的功能,但一个PTP子网内只能有一个主时钟,主时钟担当时间发布者的角色,从时钟担当接收者的角色。整个系统中的最优时钟为最高级时钟GMC(Grand Master Clock),有着最好的稳定性、精确性等。根据各节点的时钟精度、级别以及UTC(通用协调时间)的可追溯性等,由最佳主时钟算法来自动选择系统内的主时钟。

BMC算法由两部分组成:(1)数据集比较算法(data set comparison algorithm),比较两组数据的优劣,选出质量较优的数据集;(2)状态决策算法 (state decision algorithm),根据数据集比较算法的结果,计算本地时钟每个端口当前应该所处的状态,并作相应的端口状态转换。

BMC算法的软件实现:BMC算法在时钟的每个端口上运行,它规定了数据比较的顺序和判据,时钟端口在设备上电时进行缺省初始化配置,为各数据集分配缓冲区等操作,然后系统开始侦听网络上的时钟报文,如果端口收到相应的PTP报文,就调用BMC算法;或者当时钟处于未校准状态时,端口收到其他同步时钟的PTP报文后,也调用BMC算法。实现时钟端口的BMC算法的软件流程如图4所示。

BMC算法的实现步骤如下:

(1)对于具有N个端口的时钟C0的其中一个端口r,通过数据集比较算法比较从这个端口接收到的其他时钟端口的有效同步报文的数据集,计算出最优的Erbest。

图4 BMC算法的软件流程

(2)对 C0的所有端口比较 Erbest,计算出 N个端口中最优的 Ebest。

(3)对 C0的每个端口,根据 Erbest和 Ebest以及缺省数据集,通过状态决策算法决策出端口应该所处的状态,并更新所有端口的数据集。

(4)把决策出的端口状态反馈到PTP引擎状态机,由状态机控制和实现端口状态的转化[3]。

对于系统的每个时钟,每个端口都运行BMC算法,这个运算是连续不断的,因此能适应时钟和端口的变化。通过仿真测试,BMC算法能实现对主时钟的最优选择。

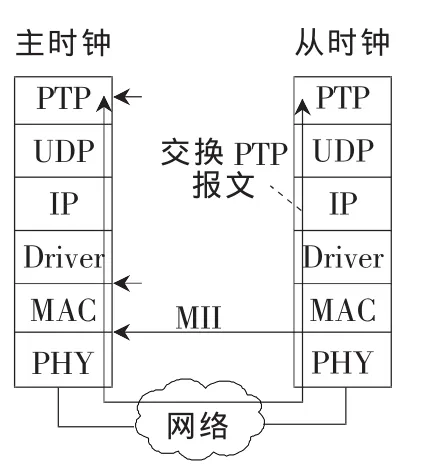

2.2 硬件时间戳的实现

时间戳标记精度直接影响IEEE 1588协议的时钟同步精度,给报文加时间戳有以下两种方法:(1)报文由软件处理时出现软件时间戳;(2)报文实际到达或离开设备时出现硬件时间戳。以往使用软件方式获取的时间戳受操作系统和协议栈的延迟不确定性以及网络传输延迟的不确定性的影响,导致时钟同步精度较低。为了提高时间戳获取精度,就必须尽量将时间戳标记位置向网络底层移。PTP协议将时间戳下移到介质访问控制(MAC)层 和 网 络 物 理 (PHY)层之间的MII层,有效地提高了精度,如图5所示。

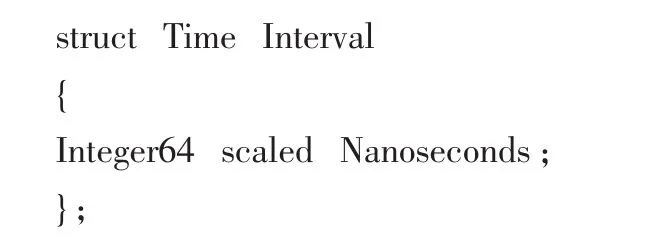

IEEE1588V2.0中时间戳的表示为:

图5 硬件时间戳标记位置示意图

Seconds Field表示时间戳的整秒部分,nanoseconds Field表示纳秒部分,纳秒的表示范围为0≤|nanoseconds Field|≤109,并且,加入了一个新的数据类型——时间间隔数据类型。

时间间隔是一个64位有符号整型数,可以使时间分辨率达到纳秒的1/216,提高了同步精度[2]。目前,IEEE 1588硬件时间戳的实现方案主要有:(1)通过FPGA实现支持IEEE1588的MAC;(2)采用美国国家半导体公司推出的具有IEEE 1588硬件支持功能的高精度以太网收发器;(3)选用支持IEEE 1588硬件时间戳功能的微处理器[4-6]。

2.3 本地时钟同步(LCS)算法

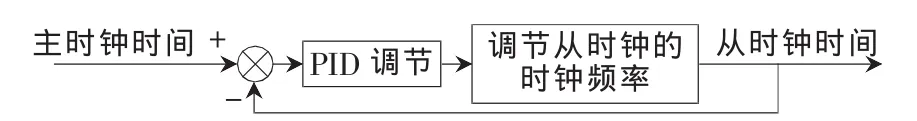

LCS(Local Clock Synchronization)算法主要完成从时钟的校准。LCS算法包括两个方面:(1)从时钟设备需要加上时间偏差以调整绝对时间,使从时钟在此时刻与主时钟的系统时间完全一致;(2)从时钟设备调整自身的时钟频率。与主时钟的时钟频率保持一致。不能单靠调整绝对时间,因为时间偏差只在一定时期内应用,主从时钟频率的不一致会使调整后的从时钟的时间向前或向后跳跃。因此,时钟同步过程分两步执行:①如果时钟偏差过大则应调整系统绝对时间;②如果时钟偏差较小则相应的调整从时钟的时钟频率。在调整系统时钟频率的过程中系统会变成控制环路,IEEE 1588从时钟同步模型如图6所示。

图6 IEEE 1588从时钟调节模型

主时钟时间是参考输入,而从时钟时间是跟踪主时钟时间的输出,时钟偏差驱动从时钟调节自身时钟频率。在控制策略上,选用改进的PID控制器——变参数PID控制器,根据时钟频率调节次数的增加,通过非线性函数在线改变P、I、D控制参数的大小,以获取满意的控制性能。

3 影响同步性能的因素

(1)网络时延的对称性。IEEE 1588的路径时延测量假设通信路径时延是对称的,可以通过增加网络时延测量频率,降低其影响。(2)时钟的漂移和抖动特性。主时钟的任何时变行为都会扰动该控制系统,导致稳态和瞬态两种误差。因此,时钟的漂移和抖动越低,则同步精度越高。(3)控制法则。控制法则参数包括调节时间、超调量和稳态误差等,都将直接影响时钟同步性能。(4)Sync报文的发送周期。发送周期越长,下一个Sync所观察到的时间误差越大。一般发送周期选为2 s,可以选择减小周期来提高精度。(5)时钟分辨率。本地时钟的分辨率由时钟频率决定,最小的时间增量为时钟信号的一个周期。可以考虑选用支持高时钟频率的CPU作为IEEE 1588时钟同步的硬件。

4 时钟同步精度测试

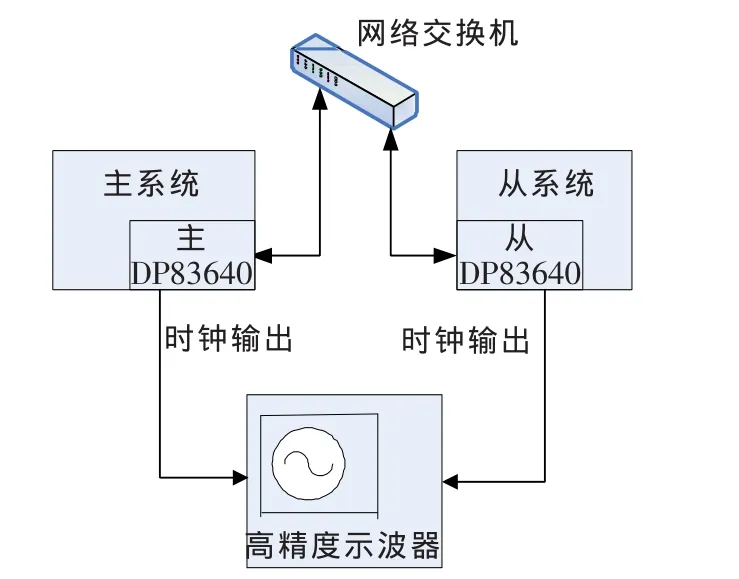

通过观测输出时钟来测量时钟同步,设定主时钟和从时钟在同一个频率点上产生时钟输出信号,并在示波器上比较这两个时钟信号[4]。IEEE 1588同步性能测试硬件平台如图7所示。

图7 同步性能测试装置

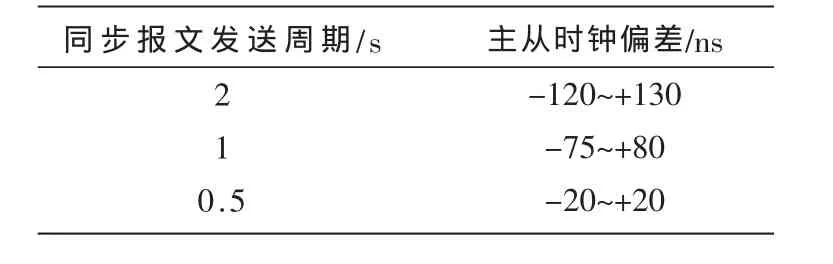

本设计主处理器采用TI推出的内置MAC功能的TMS320DM642芯片,PHY芯片选用美国国家半导体推出的以太网收发芯片DP83640,DP83640芯片内置高精度IEEE 1588同步时钟,可以在最靠近网线的位置获取时间标记,通过硬件执行时间标记,本系统同步报文发送周期可以设定。测试结果表明,在同步报文发送周期为2 s时,主、从设备之间的时钟同步精度在200 ns以内,而且缩小同步报文发送周期可以提高精度。系统达到了微妙级同步精度,可满足智能变电站任何等级的时间精度要求,测试结果如表1所示。

IEEE 1588作为一种亚微秒级精度的分布式网络时钟同步方案,对智能变电站的建设具有重要意义。本文研究了IEEE 1588的原理及实现过程,对同步精度进行了测量,实验结果表明,该方案可满足IEC 61850所有等级的对时精度要求。下一步将讨论在利用IEEE 1588对时系统时,过程层网络的组网方案。

表1 测试结果

[1]樊陈,倪益民,沈健,等.IEEE 1588在基于IEC 61850-9-2标准的合并单元中的应用 [J].电力系统自动化,2011,35(6):55-58.

[2] IEEE Std 1588-2008 Precision clock synchronization protocol for network measurement and control system[S].2008.

[3]杨佳顺,李国华,钱幸存.精确时钟协议的最优主时钟算法[J].计算机测量与控制,2011,19(9):2269-2271.

[4]王康,胡永辉,马红皎.基于IEEE 1588的智能变电站同步技术[J].电力科学与技术学报,2011,26(3):9-14.

[5]关世友,李智,胡聪.IEEE 1588协议硬件时间戳标记电路设计 [J].计算机测量与控制,2011,19 (10):2532-2535.

[6]杨传顺,吕文发,袁健.以太网精确时钟协议的研究与实现[J].计算机测量与控制,2011,19(12):3047-3049.