基于FPGA的低功耗高精度DPWM设计

2012-01-31李荣毅

唐 宁,李荣毅,罗 磊

(桂林电子科技大学 信息与通信学院,广西 桂林541004)

开关电源被广泛应用于以电子、计算机为主导的各种终端设备、通信设备等电子设备中,是当今电子信息产业飞速发展不可缺少的一种电源方式。数字控制电路具有性能稳定、无零漂、抗干扰能力强,因此得到了广泛地应用和发展。但有限的数字脉宽调制(DPWM)分辨力及ADC(数模转换)分辨力是目前数字控制的缺点之一,ADC分辨力的有效解决使得提高DPWM的分辨力成为目前研究的主要对象。理论上,提高系统时钟的频率就能增加DPWM的分辨力,因此系统时钟频率与DPWM分辨力之间的矛盾更为凸显。为了解决这一矛盾,有关学者提出了计数比较法,延时线法,Delta-Sigma法。其中,计数比较法结构简单,容易实现。但是其需要的系统时钟频率为2nfs,其中fs为开关频率,n为DPWM的分辨力。分辨力越高将需要越高的时钟频率,硬件系统不易满足而且会产生很大的功耗。延时线法是由大量的延时单元构成,这种结构的时钟频率与开关频率相同。当需要n位精度的分辨力时,需要的延时单元数目为2n-1个,而且延时单元的大小由供电压、制造工艺、工作温度决定,不易于移植与集成化。Delta-Sigma法仅限于低分辨力的DPWM中,如果应用于高分辨力中将会产出收敛速度慢,极限环等问题[1]。

1 实用新型高精度DPWM的设计

1.1 数字时钟管理(DCM)逻辑模块

数字时钟管理能够实现输入倍频、分频和4种不同的相位时钟输出(0°,90°,180°,270°),提供零传播延迟、低时钟相位差和高级时钟区域控制等。在本设计中主要运用了DCM的倍频与移相功能。正如前文所述,数字控制系统的缺点之一是其DPWM有限的分辨力。由图1可知,在一个开关周期(Tsw)内,分辨力Δf的大小可以由两个连续占空比(din1,din2)的最小增量(Δt)决定,其关系见式(1)

图1 DPWM分辨力的图解

因此为了得到更高的分辨力有必要对DCM移相得到的CLK0,CLK90,CLK180,CLK270这4种相位进行一些逻辑处理。将它们与CLK2X或CLK2X180相与后可以得到占空比为25%的占空比,同理与CLK4X或CLK4X180相与可以占空比为12.5%的占空比。将占空比为12.5%的占空比与CLK2X0,CLK2X90,CLK2X180,CLK2X270,CLK8X,CLK8X180进行相应的与后可得6.25%的占空比。

1.2 数字抖动模块

1.2.1 数字抖动的基本原理

数字抖动是基于输出电压平均值的原理。通过改变相邻几个周期内占空比的最低有效位(LSB),从而平均几个周期的占空比,最后由LC滤波器输出实现[2]。3位抖动经过8个开关周期后LC的输出如图2所示。

图2 3位抖动方案的实现

可以看出经过2Ndith个开关周期,DPWM的有效分辨力提高了Ndith位,其关系如式(2)

式中:NDPWM_EFF是DPWM有效分辨力;NDPWM是硬件实现的位数;Ndith是抖动实现的位数。

1.2.2 抖动位数的选择

由式(2)可知,DPWM抖动的位数越多,分辨力就越高。但是数字抖动方式会产生低频纹波且LC滤波器在低频下滤波效果下降。当位数增多时输出抖动纹波会越大,甚至会引起极限环现象,所以抖动的最大位数是有限的。数字抖动纹波的峰峰值vp-p-dith决定着抖动的最大位数,通过一些数学方法能推出抖动方式产生最大峰峰值vp-p-dith与抖动位数位数Ndith的关系[2]。本设计数字控制器的对象为BUCK型DC-DC电路,电路各器件的参数为L=4.7μH,C=10μF,RESR=15 mΩ,Vin=5 V,Vout=1.9 V,fs=1 MHz,NADC=10,NDPWM=11,ΔN=NDPWMNADC=1,Ncore=8。可以计算出fc=1/(2π)=0.0232×106Hz,fz=1/(2πRESRC)=1.06×106Hz。最大低频器件的抖动纹波是频率为fdith占空比为50%的方波。

根据公式(3),可知

Ndith的范围值可由式(5)和式(6)确定,即

当fc<fdith<fz时,

当fc<fz<fdith时,

将相应的数据代入式(3),当fc<fdith<fz时,0<Ndith<5.43;当fc<fz<fdith时,Ndith<0。

由Ndith≥1,故选择fc<fdith<fz。根据式(5)可得Ndith≤3.3,在本设计中选择Ndith=3。

1.2.3 抖动方式的设计方案

目前,数字抖动方式的实现主要通过查找表方式。其设计方案如图3所示。由比例—积分—微分(PID)算法控制器生成的11位DPWM,在每个开关周期的起始阶段根据它的低3位选择查找表相应的序列,然后在接下来的8个周期分别与高8位相加从而生成了新的8位DPWM1[7:0]。查找表中存放着不同的抖动序列。由于抖动方式使LC滤波器输出产生纹波,这样会致使输出电压控制效率降低,产生极限环。因此有必要选择生成纹波最小的抖动序列以降低其产生的抖动幅值[2]。其序列如表1所示。

图3 数字抖动设计方案

表1 最小的抖动序列表

1.3 低功耗高精度DPWM的设计方案

该设计的主要目标是在取得高分辨力DPWM的同时,降低其所需的系统时钟频率以及减少系统的功耗,设计方案框图如图4所示。为了在固定的系统时钟频率下获得高分辨力的DPWM,采用了同步计数及异步计数的方法[3]。系统的时钟频率fclk与开关频率fs有如下关系

式中:Ncount为计数器的位数,在本设计中的Ncount=4。新型混合DPWM设计中[5]Ncount=7,因此大大降低系统频率从而降低系统的功耗[4]。当fs=2 MHz时,本设计的fclk应为32 MHz而在新型混合DPWM设计中[5]要求为256 MHz,因此在需要更高的开关频率fs的设计中,该设计方法的优势更为突出。由于计数器在每个开关周期中都从0~15的计数,将一个开关周期分为16等份。在该设计中当计数器的值等于DPWM1[7:4]时,使能DCM模块工作生成两类(占空比为12.5%与6.25%)4种不用相位。将抖动模块生成的8位DPWM1[7:0]的[3:2]位用于选择占空比为12.5%的4路输出,[1:0]位选择占空比为6.25%的4路输出。在每个系统时钟周期内根据低4位的不同选择可以生产16中不同相位的信号,从而将DPWM的分辨力提高了16倍,分辨力增加了4位。而且该方法可以使得DCM模块只在开关周期的1/16工作,之前的DPWM的电路结构几乎都是让DCM模块工作在整个开关周期,因此该设计方案能进一步降低了系统的功耗。从前面讨论可以得出11位DPWM中,DPWM的[2:0]位是由抖动方式获得,[6:3]位是由DCM模块产生,[10:7]是由计数比较方式生成。

图4 低功耗高精度DPWM设计框架图

2 FPGA的实现与仿真验证

本设计基于ISE11.1进行仿真验证,并采用Virtex4系列的芯片。其功能仿真结果如下。

2.1 占空比6.25%的仿真图

CLKIN为开关频率,大小为1 MHz,在一个周期内产生了16种相位不同、占空比为6.25%的信号,仿真图如图5所示。

2.2 抖动方式的仿真

图5 占空比6.25%的仿真图(截图)

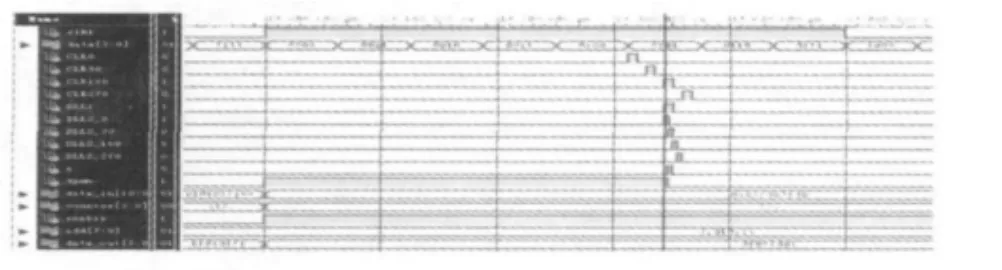

Clk为开关频率,大小为1 MHz;data_in[10:0]为PID控制算法的输出;reset为复位信号,低电平有效;counter[2:0]为计数器输出;add[7:0]为选择的抖动序列;enable为使能查找抖动序列的信号;data_out[7:0]为输出新的占空比。当新的开关周期开始时counter开始计数,enable有效。当data_in=10011010010,data_in后3位选择抖动序列,故抖动序列应为00010001,接下来的8个周期中data_out应为原来的基础上分别加0,0,0,1,0,0,0,1。通过图6可知波形图与抖动方案的设计要求吻合。

图6 抖动方式的仿真图(截图)

2.3 低功耗高精度的DPWM的仿真验证

Clk1为开关频率,大小为1 MHz;data_in[10:0]为PID控制算法的输出;data_out[7:0]为抖动后生产的新占空比;DLL1为选择后得到的12.5%占空比的信号;e为选择后得到的6.25%占空比信号,通过e信号复位dpmw信号;dpwm为总体设计的输出;当data_out[7:0]为01011001时,DCM模块应在计数值为data out[7:4]时使能;通过data out[3:2]选择DLL1信号,通过data_out[1:0]选择e信号。通过图7得知波形图符合整体方案的设计要求。

图7 低功耗高精度的DPWM的仿真图(截图)

3 总结

本文介绍了一种低功耗高分辨力的DPWM的设计方法。由PID算法控制器输出的11位DPWM,通过3位抖动电路后可以产生新的8位DPWM。新DPWM的高4位由计数比较器实现,低4位由DCM模块实现。该设计通过降低系统时钟频率和控制DCM模块只在1/16开关周期内工作实现降低系统的功耗。在开关频率为1 MHz,系统频率为16 MHz的条件下,该设计通过了FPGA开发系统的仿真,验证了该设计方案的可行性。

[1]QIU Y,LI J,XU M,et al.Proposed DPWM scheme with improved resolution for switching power converters[C]//Proc.Applied Power Electronics Conference.Anaheim:IEEE Press,2007:1588-1593.

[2]PETERCHEV A V,SANDERS S R.Quantization resolution and limit cycling in digitally controlled pwm converters[J].IEEE Trans.Power Electronics,2003(18):301-308.

[3]SYED A,AHMEN E,ALARCON E,et al.Digital pulse-width modulator architectures[C]//Proc.35th Annual IEEE Power Electronics Specialirls Conference.Aachen:IEEE Press,2004:4689-4695.

[4]WANG X.High slew rate high-efficiency DC-DC converter[M].Florida:University of Central Florida Press,2006.

[5]高艳霞,徐妍萍,郭水保.新型混合DPWM方法及其实现[J].电力电子技术,2009(6):84-86.