E1/LAN反向复用技术的FPGA实现

2012-01-14宣二勇常立新王俊芳

宣二勇,常立新,王俊芳

(1.中国电子科技集团公司第五十四研究所,河北石家庄050081;2.总参信息化部驻石家庄地区军代室,河北石家庄050081)

0 引言

当前以太网和SDH系统分别是IP业务和时分复用(TDM)业务的主要承载网络,如何实现SDH上的IP业务传输一直是业界研究的热点之一。EOS[1](Ethernet over SDH)是当前一种较现实和较高效的解决方案,然而用SDH传送以太网业务存在的一个主要问题是SDH的虚容器速率与以太网速率不匹配造成的带宽浪费,为此ITU提出的虚级联技术[2]很好地解决了这一问题,即把一路高速数据适配到N路互相独立的低速信道中传输,提供相当于多路低速信道容量之和的传输带宽。当低速传输信道为E1时,便为E1虚级联,也称作E1反向复用技术。

E1/LAN反向复用技术是将一路高速以太网数据流捆绑到多路低速E1链路上进行传输工程应用技术,该技术在现有SDH传输设备的基础上,充分利用E1链路资源,为多个局域网通过SDH网络实现互联提供了一种简单经济的解决方案。

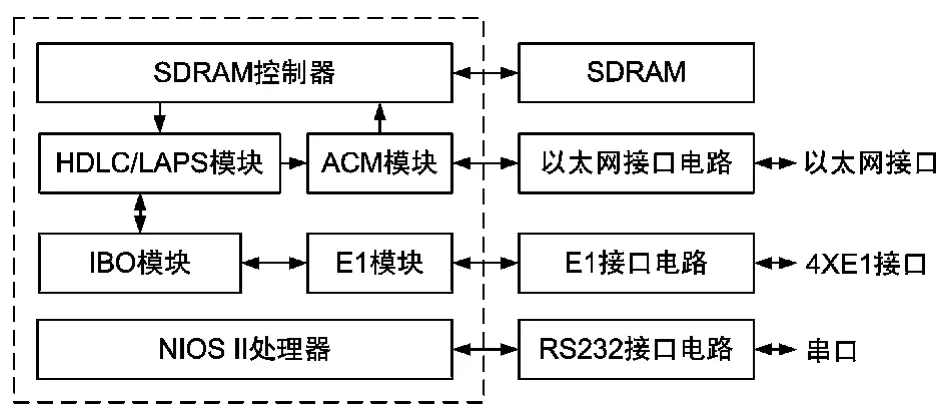

1 总体设计

E1/LAN反向复用技术的系统设计框图如图1所示。虚线框表示FPGA芯片,主要由媒体访问控制(MAC)模块、高级数据链路控制(HDLC)/链路访问规程(LAPS)[3]模块、交错间插总线操作(IBO)模块、E1模块、SDRAM 控制器和 NiosⅡ处理器[4]构成,主要完成介质独立接口(MII)与4路E1接口之间的数据转换。由于以太网接口速率为10/100 Mbps,而 4路 E1链路的总带宽仅为8.192 Mbps,为避免以太网数据分组突发时造成的数据丢失,采用外接SDRAM存储器缓存突发的数据分组。NiosⅡ处理器是片上可编程系统(SOPC)的核心,通过Avalon总线与各模块相连,结合片内定制的通用异步收发(UART)模块可以实现对整个系统的控制与维护。

图1 系统总体设计

1.1 MAC模块

MAC模块完成以太网侧MAC帧的收发,支持10/100 Mbps全双工操作。在接收方向,从MII接口接收MAC帧,进行前导码和帧起始定界符检测和循环冗余校验(CRC),若校验结果正确,将数据分组通过SDRAM控制器写入SDRAM,否则丢弃该MAC帧;在发送方向,从HDLC/LAPS模块接收数据分组,添加CRC字段和前导码,封装成MAC帧后通过MII接口送往接口电路。NiosⅡ处理器通过写控制寄存器的相应比特位,可以设置MAC模块的端口速率、允许接收的最大帧长度、是否去除CRC字段和接口环回等;通过读取状态寄存器的相应比特位可以获得该模块的当前状态。

1.2 HDLC/LAPS模块

HDLC/LAPS模块将MAC帧封装为HDLC帧或LAPS帧,采用字节操作模式,主要完成HDLC成帧/解帧、标志生成/检测、语义转换操作、帧校验(FCS)和异常帧检测等操作。在发送方向,从SDARAM中读取数据分组,首先进行语义转换操作,然后封装为HDLC帧或LAPS帧送往IBO模块;在接收方向,从IBO模块接收到的数据流中检测HDLC/LAPS帧起始标志,一旦检测到帧起始标志后,进行帧校验,去除帧头、帧尾字段和异常帧检测等操作,最后完成语义转换后将恢复的数据分组送往MAC模块。NiosⅡ处理器通过写控制寄存器的相应比特位,可以设置帧类型(HDLC帧或LAPS帧)、HDLC帧格式(标准HDLC帧或简易HDLC帧)、循环冗余校验模式(CRC-32、CRC-16或no-CRC)、比特收发顺序(大端模式或小端模式)、扰码与解扰、最大帧长度和接口环回等参数。

1.3 IBO模块

IBO模块主要完成链路层协议握手、复分接、链路差分时延补偿和序号产生/检测等操作,是整个实现的重点和难点。

系统上电初始化完成后进入握手阶段,两端节点间进行链路层协议的握手,握手操作在每路E1链路上单独进行,握手流程如图2所示。

图2 握手操作流程

A端首先发送握手起始命令,接着发送3个连续序号的序号命令,然后发送空操作命令;B端接收到握手起始命令后,立即发送握手起始命令,接着发送3个连续序号的序号命令和空操作命令。对于A端或B端来说,若接收到对端发送过来的握手起始命令和3个序号连续的序号命令,则认为本地同步,并向对端发送本地同步命令。当接收端接收到对端发送的同步命令后,则认为对端同步;当本地和对端均同步后,握手成功,进入数据收发阶段。各命令格式如表1所示。

表1 握手命令

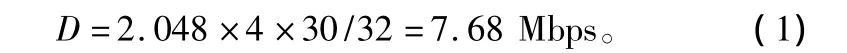

进入数据收发阶段后,在发送方向,将HDLC/LAPS帧以字节交错间插的方式分接到握手成功的链路上传输,握手未成功的链路发送固定字节FFh。各链路带宽为2.048 Mbps,数据帧格式为每帧32个时隙,其中第1时隙固定为FFh,第2时隙在握手阶段传输握手命令,数据阶段传输帧序号,其余时隙传输数据字节。系统总的有效带宽D为:

在接收方向,首先进行E1帧对齐,序号检测和纠错,然后将相同序号的四路2.048 Mbps TDM数据流以字节交错间插的方式复接成一路8.192 Mbps数据流,送往HDLC/LAPS模块。

1.4 E1模块

E1模块主要完成广域网侧4路E1数据流的收发,由E1成/解帧模块、帧同步检测模块、时钟提取模块和HDB3编解码模块构成。在发送方向,将IBO模块送来的2.048 Mbps数据流,封装为E1帧后经HDB3编码后送往E1接口电路;在接收方向,首先从接收的HDB3码中提取出2.048 MHz时钟信号,然后进行HDB3解码和E1解帧后,送往IBO模块。

1.5 NiosⅡ处理器

NiosⅡ是Altera公司针对SOPC解决方案在其FPGA中集成的软核处理器。为了降低设计成本和设备体积,在FPGA内构建了简单的SOPC系统代替外部处理器,实现对设备的控制与维护。

NiosⅡ处理器通过Avalon总线与各模块相连,完成的工作包括:①上电时对系统各模块进行初始化操作;② 利用片内定制的UART模块,完成对各模块的参数设置与状态查询。

2 关键技术

2.1 差分时延补偿

E1/LAN反向复用技术将一路以太网数据反向复用到多路E1链路上进行传输。由于各E1数据流经过的路径不同,同一数据分组的各个分片到达接收端的时间也不同,因此接收端在将各E1链路接收的数据流恢复为HDLC/LAPS帧之前,必须对各分片进行时延补偿。具体实现原理如下:

①将各链路接收到的E1数据帧写入到先入先出队列(FIFO)中,然后采用同一时钟将数据读出,实现各链路E1帧头对齐。

②当某一链路接收到握手起始命令后,启动本链路定时器和全局定时器。每接收到一个E1数据帧,定时器加1,同时将后续接收到的E1数据帧写入本链路的片内缓冲区中进行缓存。

③握手成功后,首先复位各缓冲区的读写指针,然后利用各链路定时器的当前值和全局定时器的当前值调整各缓冲区的读指针。

通过上述指针调整后,同一时间从各链路缓冲区中读取的E1数据帧将保持序号相同,由此实现了各链路的差分时延补偿。容许的差分时延大小由片内缓冲区的容量决定,缓存区容量R(kbit)与容许的差分时延T(ms)之间的关系为:

在本设计中使用了256 kbit的片内缓存区容量,因此容许的各链路的最大差分时延为16 ms。

2.2 链路动态调整

在数据传输阶段,当某些链路发生故障或从故障中恢复时,系统应能够自动将数据切换到有效链路上传输,保证链路带宽的最佳利用,这称为链路动态调整特性。链路动态调整的原理为:由于传输链路状态发生变化,将导致E1模块中的E1帧同步状态发生变化,因此当可用的E1链路数与当前正在使用的链路数不同时,重新发起链路握手操作,由此实现链路的动态调整。

链路动态调整带来的一个问题是当传输链路频繁在故障和正常之间切换时,将导致握手操作的频繁进行,从而影响数据的正常传输。为降低握手操作对链路状态变化的敏感度,在具体实现时通过增加一个计时器来控制有限状态机的状态切换,即当E1帧同步状态发生变化时,启动计时器进行计时,若计时器满时E1帧同步状态未发生变化,则控制状态机进入握手状态,若在计时器未计满前E1帧同步状态再次发生变化,则重新启动计时器,不进行握手操作。

3 解决的问题

针对工程需求,在CycloneⅡ FPGA上完成了E1/LAN反向复用技术的硬件实现。相对于采用专用集成电路和微处理器实现的设计[5,6],该实现方法解决了如下问题:

①由于该设计中的所有功能模块均在FPGA中利用逻辑资源实现,因此大大减小了设备体积,降低了设备功耗,提高了设备可靠性;

②通过改变相应模块的逻辑,可以实现将一路以太网数据反向复用到更多的E1链路上,灵活性好,可扩展性强;

③利用差分时延补偿技术,各链路容许的差分时延达16 ms,通过增加片内缓冲区的大小,可以进一步提高该指标。

④利用链路动态调整技术,实现E1链路的动态增加和删除。另外可以根据应用需求进行灵活配置,强制使用部分E1链路作为传输链路,合理利用E1链路资源。

4 测试及结果分析

4.1 链路动态调整测试

对实现的设备进行了互通测试,2台设备之间通过4路E1互连,设备的以太网口连接至计算机,2台计算机进行连续ping数据包操作,利用SignalTap逻辑分析仪对IBO模块中的数据进行采集。

当断开任意E1链路时,2台计算机之间ping操作在出现部分数据包丢失后,能够重新ping通,同时出现时延变大;当恢复断开的E1链路后,2台计算机之间仍能够ping通,时延变小。

分别断开和恢复第4路 E1链路,通过SignalTap逻辑分析仪观察IBO模块中的数据收发情况。可以发现,断开第4路E1链路前,第4路发送的帧间填充符为7Eh,断开第4路E1链路后,第4路发送的字节为全FFh,在接收端可以看到有效数据被调整到前3路E1链路上传输。

通过以上测试可以发现当业务两端之间的E1链路状态出现变化时,设备能够自动将业务承载到有效链路上传输,保证了两端之间的业务互通,由此验证了该设计具有链路动态调整的特征。

4.2 差分时延补偿测试

通过在第1路E1模块中增加缓冲模块模拟该链路传输过程中产生的延时,测试对不同链路差分时延的支持。缓冲模块中缓冲区大小设置为32 kbit,因此第1路E1链路相对于其他链路延时16 ms。2台计算机之间进行连续ping数据包操作,ping数据包长度为32 byte。增加缓冲模块前,ping数据包时延小于1 ms;当增加缓冲模块后,ping数据包时延变为16 ms。由此可以说明当各链路的数据到达接收端的时延不同时,设备能够自动对各链路时延差进行补偿,即设备具有差分时延补偿特征。

5 结束语

根据工程需求,使用VHDL语言完成了多路E1/LAN反向复用技术的FPGA实现,利用此技术设计完成的E1/LAN反向复用设备具有体积小、功耗低、可靠性高、灵活性好和可扩展性强等特点。灵活链路动态调整和时延补偿技术,不仅满足当前工程的需求,在未来的其他应用领域也可以根据传输链路的变化进行灵活配置,具有较广的应用前景。

[1]肖萍萍,吴建学.SDH原理与技术[M].北京:北京邮电大学出版社,2002.

[2]李 玲.EOS中虚级联及 LCAS功能的芯片设计与FPGA实现[D].济南:山东大学,2009:12-18.

[3] ITU-T Recommendation X.86/Y.1323.Ethernet over LAPS[S],2001.

[4]李兰英.NiosⅡ嵌入式软核SOPC设计原理及应用[M].北京:北京航空航天大学出版社,2006.

[5]刘 羿.以太网10BASE-T到E1接口的硬件设计及实现[D].成都:电子科技大学,2003:14-37.

[6]魏海功,杨勇涛.基于DS33Z41的协议转换器[J].电子技术,2006(12):64-66.