射频电路中的CMOS LNA设计方法与性能提高方法研究

2012-01-13

1.引言

LNA是接受路径中的第一个增益级,所以它对于噪声、线性度、阻抗匹配、带宽等参数有着更加严格的要求,例如,在外差结构中,LNA的典型参数值为:2dB NF、-10dBm IIP3、50ohm输入输出阻抗、15dB增益、-15dB输入输出返回损耗、稳定性因子>1、20dB逆向隔离[1]。MOSFET器件在亚微米技术中,通过对器件和偏置电流的合理组合,可使噪声降到一个令人满意的大小,所以,随着MOSFET器件性能的提升,LNA器件也获益良多,取得了长足的发展。因此,对CMOS器件构成LNA的方法研究是非常必要的。

本文即是通过对各种具体方法的介绍,使我们对整体的LNA设计方法有一个明确的认识,并对以后各种问题的解决提供更多的方法。

2.CMOS LNA RF的整体设计方法

前文已经介绍了LNA的典型参数值:

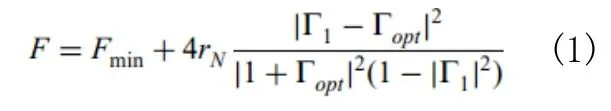

噪声系数:

输入发射系数:

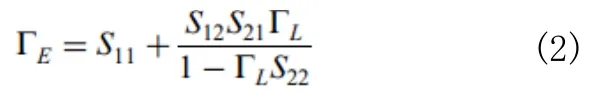

式中,rN为噪声等效电阻,Sij为双端口网络的散射系数,Γopt源反射系数的值,Γ1即对应着噪声系数最小值Fmin。

所以,为了减小噪声系数,首先要获得小的Fmin和低的rN,其次要减小Γopt,最后可以通过π型阻抗匹配网络实现源的阻抗匹配,从而可以使用片上电感。

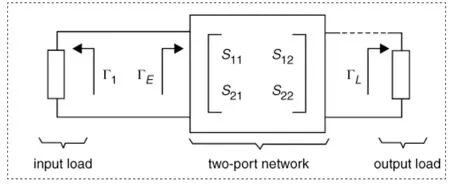

图1是一个具体的设计实例(仅考虑NMOS的情况)。节点1为输入,节点2为输出,节点3处通过电感接地。输出接理想1H电感。可以通过调整M1、M2的宽长比来实现Fmin与rN的最小化。

反馈补偿电感L2的作用是修正网络的输入阻抗,使ΓE的共轭更加接近Γopt。

图2中沟道最佳宽度在40-160µm之间,考虑到rN可以降低源阻抗的敏感度,所以,可以最佳沟道宽度为120µm[2]。

图1 输入输出网络参数图

图2 实际电路及各部分尺寸(Vdd=2.5V)

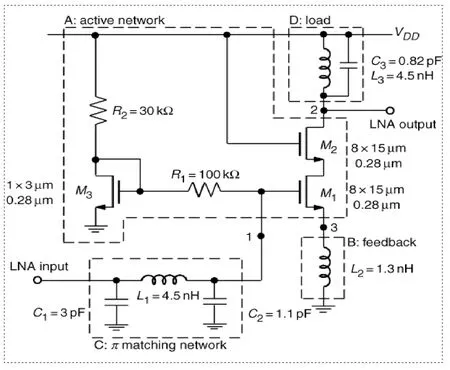

图3 前置放大部分的示意图

图5 LC谐振隔离的静电保护设计电路

3.性能提高方案

3.1 采用两级放大来提高性能

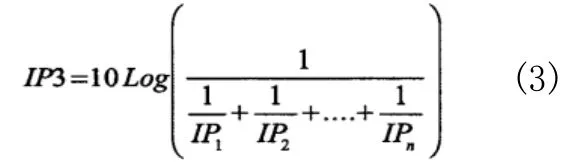

这是一个比较老但却实用的办法,第一级放大通过控制偏置条件和器件尺寸来减小噪声,这是因为第一级放大的噪声在全部噪声中影响最大,后一级主要用于调整线性度[3]。关于减小噪声,上文已有比较详细的描述,此处不再重复。线性度,主要通过三阶交调点IIP3来表示。由式(3)可以看出,三阶交调点主要是受最后一级的影响。

通过这种方式,我们就可以把噪声和线性度分开调整,减小彼此之间的冲突,更好的提高性能指标。

3.2 片上系统

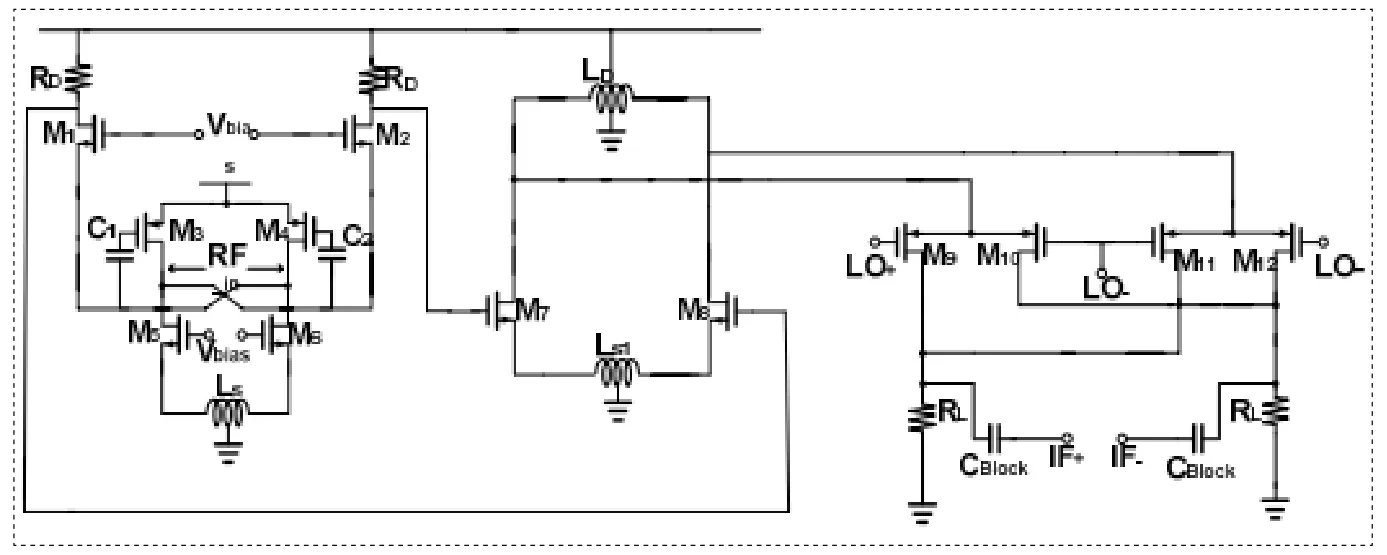

把NMOS开关、前置放大、混频器等各个模块都集中到一个芯片上面,不仅仅是对LNA性能的大幅提升,甚至对于整个RF芯片来说,在集成度、带宽等各种性能上都有非常大飞跃,SOC将是比较主流的发展方向之一。

目前,已有很多系统采用SOC的方式来实现射频电路的设计,以一个5GHz的雷达系统为例,把NMOS开关、前置放大、上混频器、电压控制振荡器等模块全部集中在了基于0.13µm工艺的CMOS芯片上,带宽达到20Ghz,在线性度、输入反射系数、噪声、稳定性因子等各个性能指标均达到较好水平[4]。

图3是一个典型的片上系统的LNA部分示意图,M1-M4主要是实现阻抗匹配,M5、M6作为电流源提供恒定电流,通过NMOS M1、M2和PMOS M3、M4和负载可以减小噪声,后面部分作为负载,实现阻抗匹配,把电阻调整至50ohm。

3.3 静电保护阻抗隔离设计

静电保护电路会使射频LNA电路的增益下降、噪声增加,所以,在这里介绍一种阻抗隔离技术,可以减少保护电路的有害影响。

电路的增益下降、噪声增加主要是由于ESD部分对输入端口网络的寄生电阻和寄生电容引起的,所以用LC谐振回路将ESD部分和电路隔开,可以有效的缓解寄生效应,从而提高电路的性能,如图4中的L1、C1和L2、C2网络,通过Dp1(Dn1)进行正向导通放电,以及MNESD部分的保护作用,可以对静电保护电路进行有效的保护,防止电压击穿等损害的发生[5]。

4.结束语

本文着眼于用CMOS来实现射频电路中的LNA部分的设计。一开始先综述答题的设计方法,并对LNA电路的性能指标进行介绍。然后,又介绍三种实用的设计方法,对LNA电路进行改进。当然,在设计中,我们要清楚设计电路的最主要的性能参数是什么,并努力的去实现完成。采用上述的设计方法,可以尽可能的提高电路的效率和性能。

[1]Behzad Razavi著,余志平,周润德,译.射频微电子[M].清华大学出版社,2006:131-142.

[2]M.Egels,J.Gaubert,P.Pannier and S.Bourdel.Design method for fully integrated CMOS RF LNA[J].Electronics Letters ,2004,40(24):1513-1514.

[3]Piljae Park,Cheon Soo Kim,Member,IEEE,and Hyun Kyu Yq Member,BEE.Linearity,Noise Optimization for Two Stage RF CMOS LNA[J].Electrical and Electronic Technology,2001:756-758.

[4]Yuan Liang.RF NMOS Switch,Front End,Up Converted Mixer,LC-VCO Co-Design in a SoC-based Sensor Chip in 0.13µm CMOS.System Science and Engin eering(ICSSE),International Conference,2012:389-394.

[5]Ming-Dou Ker and Chien-Ming Lee.ESD Protection Design for Giga-Hz RF CMOS LNA with Novel Impedance-Isolation Technique.Electrical Overstress/Electrostatic Discharge Symposium,2003:1-10.