基于CPLD的BPSK编码的调制与解调

2012-01-05谭来军韩壮科梁羽佳

谭来军 韩壮科 宋 涛 梁羽佳

(中国石油测井有限公司技术中心 陕西 西安)

基于CPLD的BPSK编码的调制与解调

谭来军 韩壮科 宋 涛 梁羽佳

(中国石油测井有限公司技术中心 陕西 西安)

文章对CPLD可编程器件在综合化测井系统中BPSK编码的调制解调原理进行了阐述,给出了BPSK调制解调系统各个模块的算法和结构,通过对ALTERA公司生产的EPM7064芯片和可编程软件环境的仿真,得出了各个系统中的时域和频域的波形图,并设计实现已在测井系统中得到应用。该系统运行稳定可靠,对全数字调制解调的硬件实现具有实际的指导意义。

CPLD;BPSK编码;调制解调

0引言

随着可编程器件的普及和高性能的可编程逻辑芯片的使用,缩短了设计的周期的同时也大大提高了系统的稳定性。而CPLD普遍被认为是建构原型和设计开发的最快途径,其芯片能够进行在线编程、排错、再编程和重复操作等优点,利用CPLD这些优点能够快速可靠的对BPSK编码进行调制解调,使得数控测井系统向高集成度、小型化便携化迈进了一步1、2。

1 BPSK编码原理与特点

BPSK(双相移键控)调制方式是受键控的载波相位按基带脉冲而改变的一种数字调制方式。是用二进制基带信号0、1对载波进行二相调制,载波的相位随调制信号的0或1改变。通常用相位00和相位1800来分别表示0或1。

图1 双相移键控 (BPSK)调制码波形图

经BPSK编码调制后的波形如图所示。“0”只在位边界处有电平跳变,而“1”在位边界和位中央都有电平跳变。这是一种“自时钟码”,它无需单独的时钟道和精确的时间传输。时钟瞬时频率即使有较大的变化(20%~ 30%),也不会影响所传输的数据码值。BPSK波形中没有直流成分,易于传输和处理。因为BPSK调制只有0°和180°两种相移,相应电路比较简单,可靠性高。BPSK编码调制能有效利用电缆的频带宽度,其位速率与最大传输率之比为1。

2 CPLD对BPSK编码调制解调的实现原理

2.1 CPLD对BPSK编码调制的实现原理

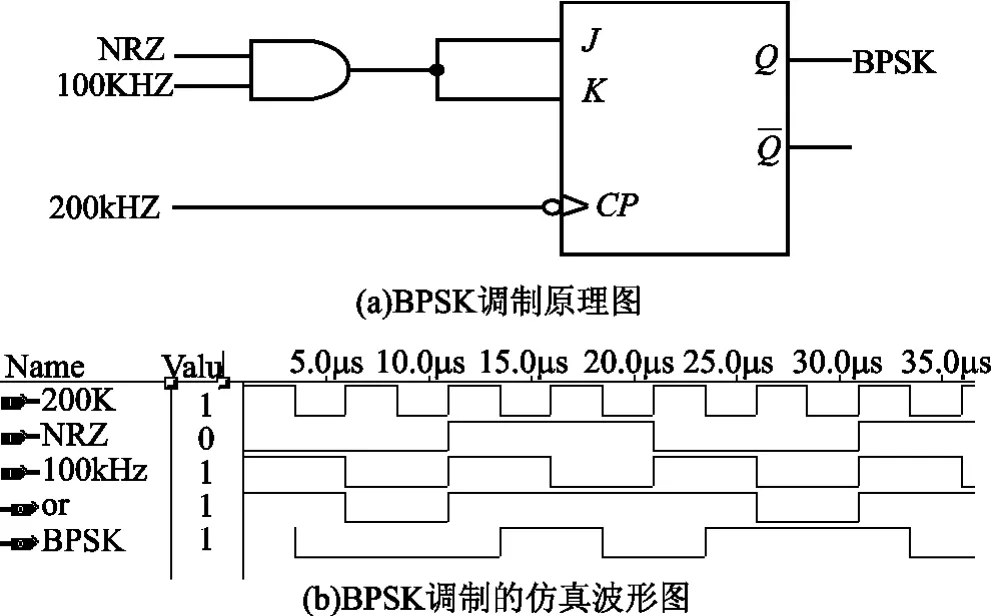

JK触发器具有输入端J、K同时为高时跳变,同时为低时保持的功能,为了实现BPSK调制功能,把要调制的数据同时输入到JK触发器的J和K端,在合适的时钟作用下,就可以实现输出调制的波形,电路的原理如图2(a)所示。

图2 BPSK调制原理及仿真波形图

进行仿真的波形如图2(b)所示。图中NRZ为码元信号,传输的数据为010。传输速率为100kHz,即每个码元的传输时间为10s,故使用的调制时钟分别是100kHz和200kHz。200kHz的时钟信号作为JK触发器的触发脉冲。100kHz信号与码元信号相或,作为JK触发器的输入。如果码元为1,那么它和100 kHz的信号相或的结果为高电平,即在每个码元开始的整个10s,or都为高电平。如果码元为0,则在每个码元开始的半个周期内为高电平,即在100kHz信号为高电平的5s,or为高电平。而在接下来的5s为低电平。当触发时刻到达,如果码元为1,那么信号电平除了在码元开始的时刻跳变以外,在码元中间也会跳变一次。若码元为0,则只在码元开始的时刻跳变3、4。由于JK触发器为下降沿触发,因此BPSK的调制信号在NRZ信号基础上延迟了2.5s。

2.2 BPSK信号解调的原理和实现方法

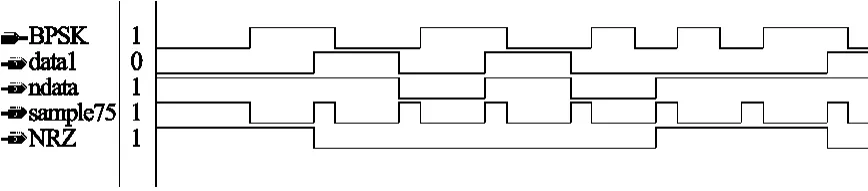

解调原理:从一个码元开始的75%处取值,把此值和向前一个周期的取值进行比较,如果这两个值相同,则说明在这一个周期内信号电平经历了两次跳变,那么这个码元的值就应该被解调为1。如果不同,那么说明在这一个周期内信号电平只经历了一次变化,那么就应该被解调为0。实现信号解调的电路如图3所示。

图3 BPSK解调电路图

1)sample75信号的产生:

sample75信号是用来在每个码元开始的75%时刻触发取值。要产生 sample75信号,必须先得到周期为10s的edge-jump信号。产生sample75信号的电路如图4所示。

图4 sample75信号产生电路

2)解调出NRZ信号:

由电路仿真可得到解调后的 NRZ波形,如图5所示。

图5 解调出的NRZ信号波形

BPSK码信号经过D触发器产生edge-jump的信号,并把它作为时钟,在分频器作用之下产生sample75的信号,sample75的信号作为作用D触发器的输入,输出信号比BPSK信号延时了一个800kHz信号周期,即可实现解调过程。

3CPLD对BPSK编码解调的设计实现

3.1 CPLD的选型和功能

经过计算机仿真,ALTRA公司生产的EPM7064的容量即可满足功能要求,经过市场调研,比较货源、价格等因素,最终选用工业级EPM7064SLCC。EPM7064SLCC内部具有64个宏单元,可用门数为1250门,采用44脚 PLCC封装,工作电压5 V。外部工作时钟采用与DSP同步的4 MHz外部时钟,由一片模块晶振提供,CPLD内部的时钟/分频电路产生BPSK调制解调需要的800kHz、200kHz和100kHz。50Hz时钟提取电路从220V交流市电供电提取50Hz工频信号,通过CPLD内部的帧启动脉冲形成电路产生周期为80 ms的帧启动脉冲。

BPSK调制模块将DSP通过串行口SPORT0发送的NRZ编码格式的数据变换为双相码。

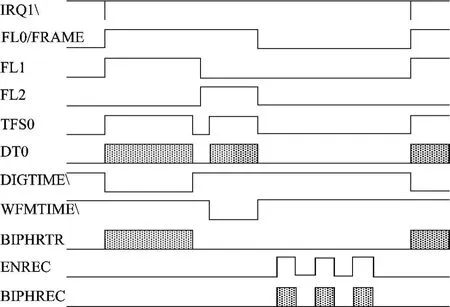

图6 CPLD外部接口工作时序波形

BPSK解调模块将经电缆传送来的双相码转换为NRZ编码,交由DSP处理。时序电路由DSP的FL0,FL1,FL2和TFS0控制,产生电缆驱动电路帧同步信号 FRAME,数据发送门控信号 DIGTIME和声波发送门控信号WFMTIME。

3.2 CPLD外部接口工作时序

CPLD外部接口工作时序以80ms为一个工作周期,由帧启动脉冲形成电路产生的80ms帧启动脉冲同步,各外部接口工作时序波形如图6所示。

4 结论

采用上述设计思想及实现方式,在综合化测井地面系统中成功实现了基于CPLD的测井信号解码,系统已在EILOG系统地面模拟器中得到实验,取得了良好的效果,达到了系统设计的要求。

[1]Jeffrey S.Beasley,Gary M.Miller.ModernElectronicCommunication(Eighth Edition)[M].北京:清华大学出版社,2006

[2]测井学编写组.测井学 [M].北京:石油工业出版社,2004

[3]BernandSklar.DigitalCommunications Fundamentals andApplication(Second Edition)[M].北京:电子工业出版社,2002.

[4]Tommy Öberg.Modulation,Detection and Coding[M]. 北京:电子工业出版社,2004

P631.8+3

B

1004-9134(2012)03-0081-02

谭来军,男,1978年生,工程师,2002年毕业于江汉石油学院计算数学与软件开发专业,现中国石油测井有限公司技术中心从事地面仪器的生产调校、遥测仪器的生产调校工作。邮编:710077

2012-06-06

刘雅铭)

经验交流