基于FPGA与USB2.0的实时数据采集与处理系统

2011-11-27赵乐森王旭柱

赵乐森,王旭柱

(中国海洋大学 信息科学与工程学院 电子系,山东 青岛 266100)

数据采集系统正越来越多地应用于控制和测试领域,在某些特定的领域,数据采集系统所起的作用也越来越大[1]。传统的数据采集方法通常采用DSP作为核心芯片,DSP虽然运行速度快,但是不能完成外围的硬件逻辑控制。FPGA时钟频率相对较高且延时小,FPGA采用IP内核技术,可以集成外围控制和接口电路[2]。本文根据项目需要,设计了一种基于FPGA的双通道、最大采样率为5 Mb/s的通用数据采集与实时处理系统。

1 系统方案设计

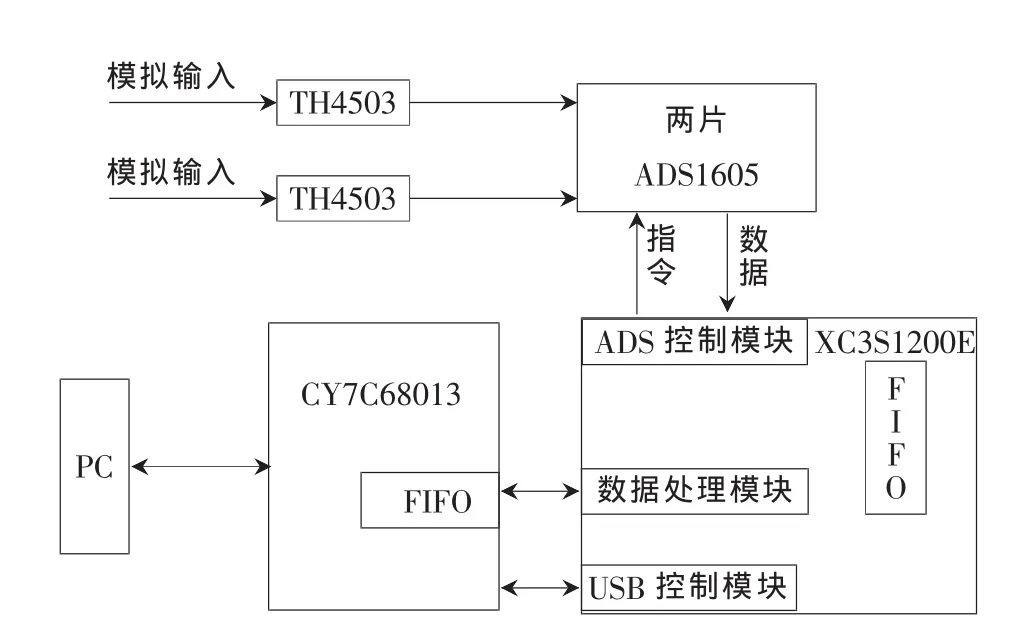

数据采集和处理系统主要由信号调理电路、A/D转换器、FPGA和USB四部分组成,如图1所示。

信号调理电路的作用是对所采集的模拟信号进行放大、滤波,将单路信号转变为差分信号,驱动A/D转换器的正常工作。本文选用TI公司的全差动运算放大器THS4503,它是模数转换器ADS1605的数据手册中推荐的运算放大器[3]。

A/D转换器在FPGA内的控制模块控制下,将所采集的模拟信号转换为16 bit的数字信号,传入FPGA中进行处理。本系统所采用的模数转换器为TI公司的ADS1605。

图1 实时数据采集与处理系统框图

FPGA芯片采用的是Xilinx公司的Spartan 3E系列中的XC3S1200E。FPGA为本系统的核心部分,控制A/D转换器的数据转换,并将A/D转换来的数据进行FFT处理。同时,FPGA的USB接口控制逻辑查询CY7C68013是否空闲,控制USB将处理完的数据传递给主机,并在PC机中显示出来,实现数据的可视化显示和人机接口的互动。

CY7C68013是Cypress公司推出的EZ-USB FX2系列的USB接口芯片,其作用是在FPGA的接口控制逻辑下,把处理完的数据传递给主机。

本系统的工作原理为:该系统可以完成两路中频信号的采样处理,单路信号经过THS4503后转变为差分信号,输入到模数转换器中,FPGA中的A/D控制模块向ADS1605发送采样控制指令,A/D转换器在控制模块控制下进行数据采集,将模拟信号转换成16 bit的数据信号,并依次选通两片A/D通道,实现由A/D转换器到FPGA的双通道数据传输。当采集的数据达到处理条件后,相应的数据在FPGA中进行FFT计算。计算完成后,将处理过的数据在FPGA的USB接口控制逻辑下,经过USB接口传递给主机,当数据传递完成后,再进行下一次的数据采集和处理。

2 系统硬件设计

2.1 信号调理电路

A/D转换器的前端需要运放来驱动,本设计中的信号调理电路采用TI公司的全差动运算放大器THS4503。经过信号调理电路后,单路信号转变为差分信号,输入到A/D转换器中。

全差动放大器的特点为:具有高分辨率、高精度以及出色的动态范围。THS4503就是一种高精度的全差动运放,选择它作为ADC的缓冲器可以简化方案的设计[4]。

2.2 A/D转换电路

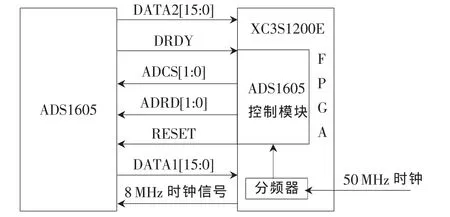

A/D转换电路是系统的重要组成部分,其与FPGA的连接如图2所示。

图2 ADS1605与FPGA的接口框图

ADS1605是TI生产的一款高采样率、高精度、易使用的16 bit ΔΣ模数转换器,ADS1605的工作电源为+5 V的模拟电源和+3 V的数字电源,独立的数字I/O电源设计使芯片可灵活与其他逻辑芯片接口[3]。ADS1605需要外接时钟源进行工作。本系统外接频率为50 MHz的晶振时钟源,经过FPGA分频后,为ADS1605提供正常工作所需的频率。

ADS1605在FPGA的控制模块下正常工作。ADS1605的控制模块对ADS1605的控制进程为:

(1)状 态 0:CS、RD 置 1,RESET 置 0, 初 始 化ADS1605,进入状态 1。

(2)状态 1:CS 置 0,RD 置 1,RESET 置 1,开始数 据转换,进入状态2。

(3)状 态 2:CS 置 0,RD 置 1,RESET 置 1, 检 测DRDY的状态,若下降沿来临,进入状态3;否则,继续等待DRDY下降沿的到来。

(4)状态 3:CS 置 0,RD[0]置 0,RESET 置 1,输出一通道转换好的数据,进入状态4。

(5)状态 4:CS 置 0,RD[1]置 0,RESET 置 1,输出两通道转换好的数据,进入初始状态。

2.3 FPGA的设计

本系统采用的是Xilinx公司的Spartan 3E系列的XC3S1200E芯片,它更好地利用了90 nm工艺,拥有的系统门数达到120万,28个乘法器,504 KB的块 RAM,136 KB的分布式RAM,8个数字时钟管理模块,最大可用管脚可达304个,它性价比也较高[2]。

XC3S1200E是基于SRAM工艺的查找表结构,它不具备非易失特性,因此断电后将丢失内部逻辑配置。在每次上电后,都需要从外部非易失存储器 (如PROM、Flash存储器等)中导入配置比特流。本系统选用的是XC F04S芯片,这是FPGA数据手册上提供的配置芯片[5]。

FPGA是本系统的核心部分,构成了数据采集系统和数据传输系统的“桥梁”,完成了对 ADS的控制,并对采集到的数据进行存储和处理,同时也完成了对CY7C68013的控制。使用FPGA使电路得到了简化,不需要额外的分立器件来存储数据。在FPGA内部构成了以下几个模块。

FIFO数据存储模块主要用来存储A/D转换的数据。由于需要同时采集两路信号(一路荧光信号,一路多普勒信号),因此需要两个FIFO模块,这样易于对数据的存储和控制。

(2)数据处理模块

本系统需要把采集到的数据进行处理,所以数据处理模块是很重要的组成部分。

在数据处理模块中,首先将一路通道采集到的荧光信号数据进行32个数据的求平均操作,以预触发两个通道的信号,然后再对一路通道的数据进行最大值和最小值计算,通过这两个数据求出荧光信号的宽度。对另一通道中的多普勒信号进行FFT计算。通过两通道得到的数据计算出所求粒子的直径。

(3)控制模块

控制模块主要完成对ADS1605、FIFO存储模块和CY7C68013的控制,这是整个系统的关键。控制模块将产生控制信号,实现系统的数据采集、处理和传输功能。

(4)分频倍频模块

系统提供的FPGA外部时钟频率为50 MHz,经过分频倍频模块将外部时钟转换成各个芯片工作所需的频率。

京津冀协同发展战略是河北省实现跨越式发展的历史机遇。河北省只有立足现实、抓住机遇,才能构建起有效的人才支撑体系,为河北省经济社会发展服务。

2.4 USB的设计

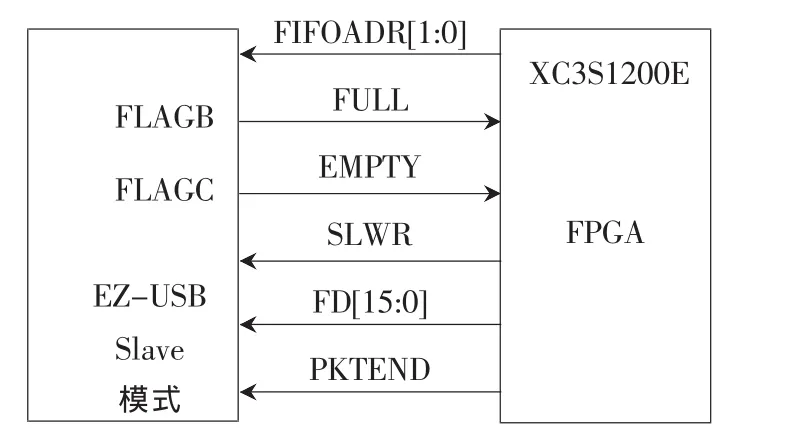

2.4.1 USB与FPGA的接口设计

在USB设计中,为了保持较高的传输速度,使用不经过CPU的SLAVEFIFO控制模式。

接口方式如图3所示:

图3 USB与FPGA的接口框图

本系统选用的芯片是Cypress公司的CY7C68013芯片。该模块的工作过程为:当采集的数据在FPGA中处理完后,FPGA根据SLAVEFIFO的控制时序产生相应的控制信号,将在FPGA中的数据传输给EZ-IJSB FX2的内部端点FIFO,而当内部端点存储满后,FX2自动将数据传输到PC机上[6]。外部控制器FPGA对FX2的控制进程如下:

(1)IDLE:空闲状态,此时如果写事件发生,将转向状态 1。

(2)状态 1:指向 IN FIFO,触发 FIFOADR[1:0],转向状态 2。

(3)状态2:如果 FIFO满标志为假,则转向状态 3;否则,保持在状态2。

(4)状态3:驱动数据到总线上,通过触发 SLWR来写数据到FIFO,并增加FIFO指针,然后转向状态4。

(5)状态 4:如果还有数据写,转向状态 2,否则,转向IDLE。

2.4.2 USB接口芯片固件程序

固件程序是指运行设备CPU中的程序,只有在运行该程序的时候,外设才能称为具有给定功能的外围设备。在该系统中,CY7C68013芯片的固件程序的主要功能就是辅助硬件系统工作,完成对设备的初始化,处理应用程序和驱动程序发送的各种命令和数据交换。

Cypress公司为使用FX2芯片的用户提供了一个完整的固件开发框架,用户只需要在框架的基础上提供一个USB描述符表,添加其他端点接收和发送数据的通信代码以及控制外围电路的程序代码,即可完成固件的开发。该固件所使用的编程工具是Keil公司的C51编译器[6]。

本文主要介绍了基于Xilinx公司XC3S1200E FPGA的数据采集与实时处理系统,采用计算机的USB接口作为数据传输接口。本系统利用FPGA内部模块来实现数据处理,采用Verilog生成的状态机来控制各个模块的连接,实现数据的采集、转换、处理和传输。本文的创新点在于:利用FPGA生成了各个接口的控制模块,并利用FPGA内部的IP核完成了对数据的FFT计算,简化了硬件的设计,使系统变的简洁。在应用中可以根据任务的不同改换内部的数据处理模块,使系统可以灵活地处理各种数据采集处理任务。

[1]沈兰荪.数据采集技术[M].北京:中国科学技术大学出版社,1990.

[2]田耘,徐文波,胡彬.Xilinx ISE design suite 10.x FPGA开发指南[M].北京:人民邮电出版社,2008.

[3]Texas Instruments.ADS1605 data book.2007.5.

[4]Texas Instruments.THS4503 data book.2004.

[5]Xilinx.Xilinx Spartan-3E FPGA family data sheet,2009.8.

[6]薛园园.USB应用开发技术大全[M].北京:人民邮电出版社,2007.