计算机仿真软件Multisim 10在电子系统设计中的应用

——基于FPGA的直接数字频率合成系统的仿真设计

2011-11-15马彦庆梁虎聂典解放军理工大学通信工程学院210007

马彦庆 梁虎 聂典 解放军理工大学通信工程学院 210007

计算机仿真软件Multisim 10在电子系统设计中的应用

——基于FPGA的直接数字频率合成系统的仿真设计

马彦庆 梁虎 聂典 解放军理工大学通信工程学院 210007

Multisim 10是一个完整的电子设计工具系统,工程师利用该软件可有效地完成电子工程项目的概念建模到最终成品的全过程。本文用Multisim 10设计基于FPGA的直接数字频率合成实验系统,介绍基于计算机仿真设计与虚拟实验来实现电子系统设计的全新理念和手段。

计算机仿真;Multisim;单片机 DDS频率合成器;VHDL

引言

EDA(Electronic Design Automation)技术已经在电子设计领域得到广泛应用,它借助计算机存储量大、运行速度快的特点,可对设计方案进行人工难以完成的模拟评估、设计检验、设计优化和数据处理等工作。一台电子产品的设计过程,从概念的确立,到包括电路原理、PCB版图、单片机程序、机内结构、FPGA的构建及仿真、外观界面、热稳定分析、电磁兼容分析在内的物理级设计,再到PCB钻孔图、自动贴片、焊膏漏印、元器件清单、总装配图等生产所需资料等等全部在计算机上完成。本文将用计算机仿真软件Multisim 10设计一基于FPGA的直接数字频率合成系统,介绍电子系统设计的主要过程。

一.Multisim 10和DDS原理简介

1. Multisim 10简介

Multisim10是一个完整的系统设计工具系统,提供了庞大的元件数据库,并提供原理图输入接口,全部的数模spice仿真功能,VHDL/Verilog设计接口与仿真功能,FPGA/CPLD综合,RF射频设计能力和后处理功能,还可以进行从原理图到PCB布线工具包的无缝隙数据传输。Multisim10提供全部先进的设计功能,满足从参数到产品的设计要求。

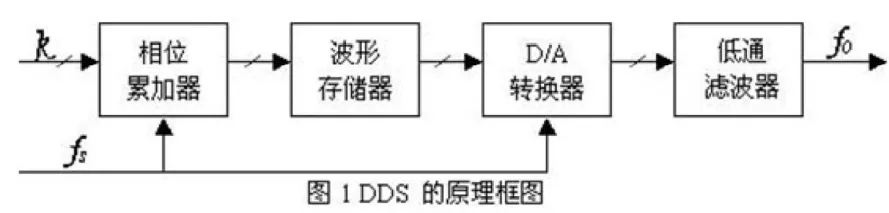

2. 直接数字频率合成(DDS)简介

直接数字频率合成(DDS)技术是60年代末出现的第三代频率合成技术,以Nyquist时域采样定理为基础,在时域中进行频率合成。DDS具有相对带宽很宽,频率转换时间极短(可小于20ns),频率分辨率可以做到很高(典型值为0.001Hz)等优点;另外,全数字化结构便于集成,输出相位连续,频率、相位、幅度都可以实现程控,通过更换波形数据可以轻易实现任意波形功能。

(1) DDS基本原理及性能特点:

相位累加器由N位加法器与N位累加寄存器级联构成。相位累加器在每一个时钟脉冲fs输入时,把频率控制字k累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

(2) DDS的输出频率计算

DDS的输出频率为:Fout=M*Fclk/(2^N),这里M为频率控制字,N为相位累加器的位数,fclk为基准时钟。由于基准时钟fclk一般是固定的,因此相位累加器的位数就决定了频率分辨率。在这里我们取N=16,即相位累加器为16位,那么频率分辨率就可以认为是16位。位数越多,分频率越高。

二.系统设计全流程

设计任务:用Multisim10设计一个基于FPGA的直接数字频率合成实验系统。本系统基于直接数字频率合成技术,以8051单片机为控制核心,通过8051单片机控制频率控制字实现频率合成;经低通滤波器滤除噪声和杂散信号就可得到比较纯正的正弦信号。设计目标为:可以实现稳定的正弦波输出,输出频率范围是100Hz~25.5KHz,且频率可调(步进100Hz),频率控制字由单片机产生。

1.DDS芯片设计流程:

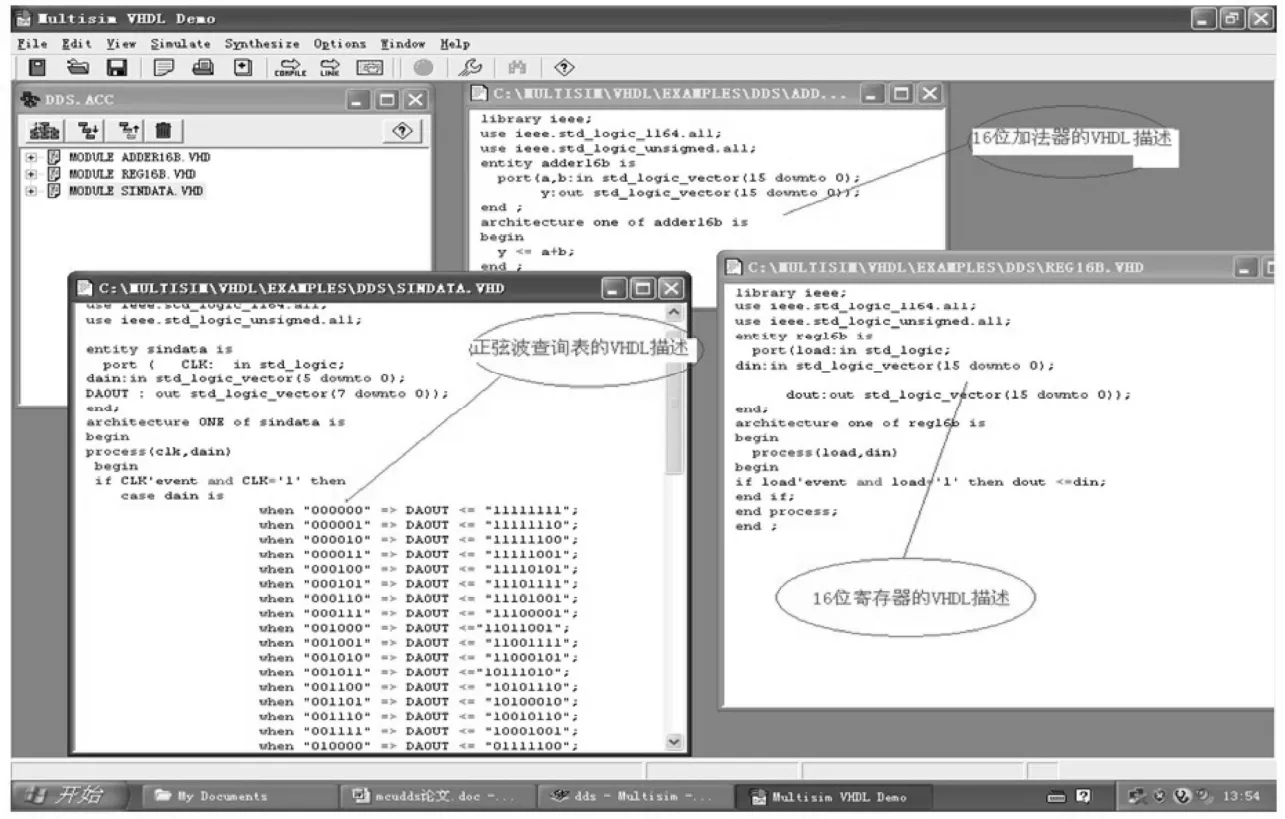

DDS芯片的构建由Multivhdl来完成(Multivhdl是Multisim10的一个附属工具,用于实现vhdl语言的编程,仿真,最后通过制作一元件的形式在Multisim10中完成系统的仿真,在实际中相当于设计一具有相应功能的可编程逻辑器件)。各模块实现原理分析和说明如下:

(1)相位累加器由加法器和寄存器构成

加法器的一个输入与寄存器输出相连,另一个输入是外部输入的频率控制字。这样,在每个时钟到达时,相位寄存器采样上个时钟周期内相位寄存器的值与频率控制字之和,并作为相位累加器在这一时钟周期的输出。频率控制字决定了相应的相位增量,相位累加器则不断地对该相位增量进行线性累加,当相位累加器积满两时就会产生一次溢出,从而完成一个周期性的动作,这个动作周期即是DDS合成信号的一个频率周期。

(2)波形存储器设计

波形存储器的作用是完成相位到幅度的转换。将相位累加器输出的相位数据作为取样地址,来寻找正弦ROM表进行相位到幅度的变换,输出不同的幅度编码。

(3)相位累加器和波形存储器在Multivhdl中的编写,调试和仿真过程如图2。

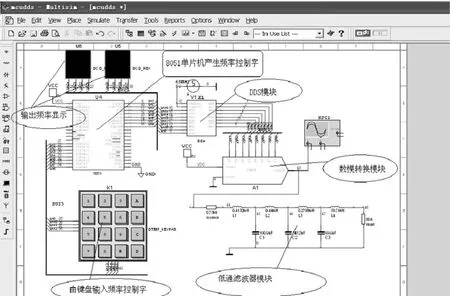

(4)将编写调试完成的相位累加器和波形存储器模块在Multisim10中生成元件以供调用。最终生成的DDS芯片如图3中所示。

2.数模转换及滤波输出电路模块设计

通过DAC可将数字量形式的波形幅值转换成所要求的合成频率模拟量形式信号,低通滤波器用于衰减和滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

在Multisim10中具有快捷的滤波器编辑器,利用它可以方便,快速,准确的设计滤波器。下图3中的低通滤波器即是笔者用该编辑器设计的低通滤波器,其截止频率位30khz,当然我们也可以设计得更精确一些,而这是以提高滤波器的复杂性为代价的。

3.用8051单片机连接DDS芯片构建系统

MultiMCU是Multisim10中的一个单片机仿真工具,它支持8×51,8×52及部分PIC单片机。汇编与仿真同在一个窗口,可以实现程序的即时编写即时仿真,修改调试方便,非常适合相关专业人员的程序调试和高校的辅助教学。本文中为了充分发挥芯片的高速性能,8051与DDS芯片的连接采用并行接口方式。8051单片机与DDS芯片的连接如图3所示。

4.单片机软件设计

DDS频率控制字存放在30h开始的单元中。8051主要用于将从键盘输入的数字输出到P1口作为DDS芯片的频率控制字,并将频率值通过数码管显示出来。程序工作流程依次为:程序开始、初始化动作、读取键值、频率字输出、程序结束等。

至此整个系统硬件以及软件已设计完成。

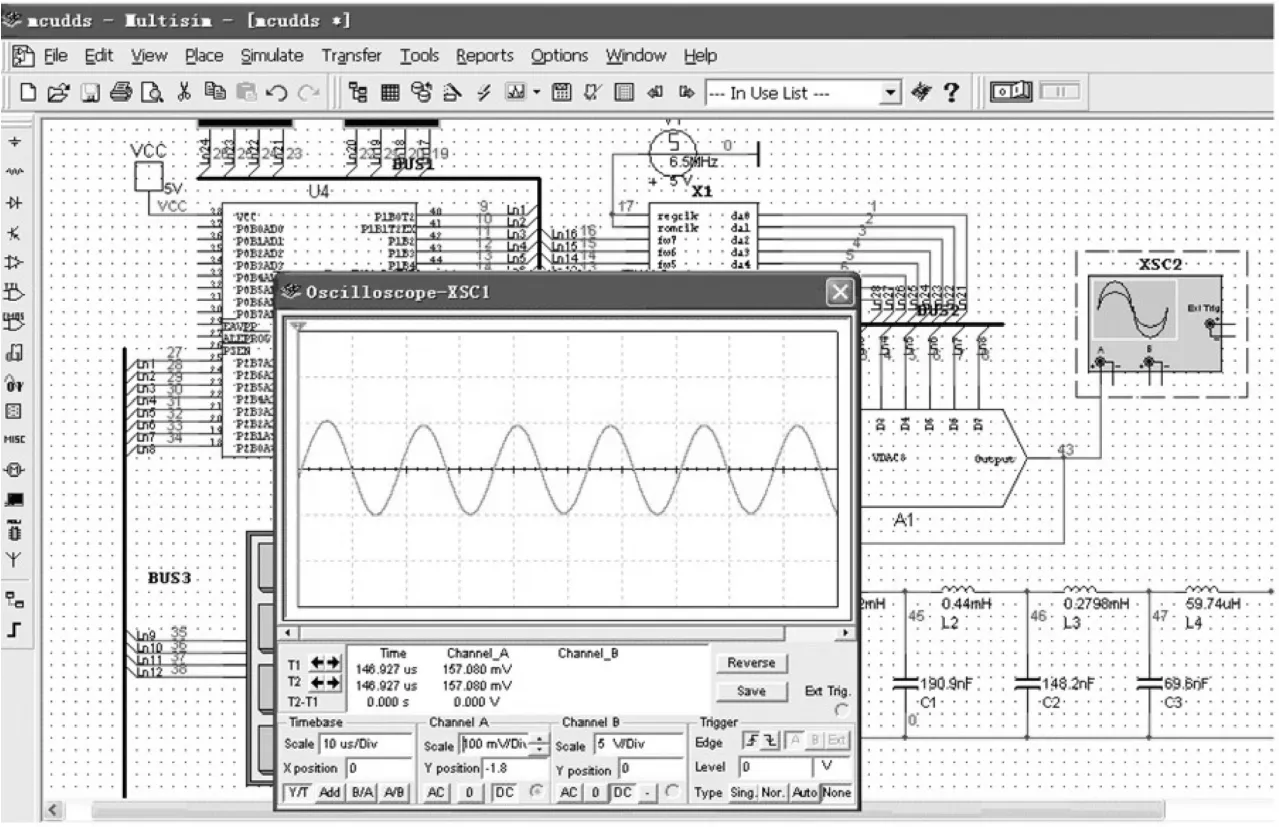

三. 仿真结果输出,测试及验证

Multisim10用软件的方法虚拟电子与电工元器件,虚拟电子与电工仪器仪表,实现了集元器件和仪器于一体。Multisim10的虚拟仪器仪表库种类齐全,有一般的实验用通用仪器,如数字万用表、函数信号发生器、功率计、示波器等,还有一般实验少用或者没有的仪器,如波特图示仪、逻辑分析仪、IV特性分析仪、频谱分析仪、网络分析仪、安捷伦示波器、实时测量探针等。这些虚拟仪器与实际显示仪器的面板以及基本操作都非常相似,它们可用于模拟、数字、射频等电路的测试。本次设计我们用逻辑分析仪测试DDS芯片的功能,用示波器观察输出波形,用滤波器测量频率。测试过程方便快捷。当按下仿真按钮时,一个标准的正弦波就呈现在眼前。通过频率计测量,输出的正弦波频率与理论计算一致。仿真结果如下图4所示。

图2 相位累加器及波形存储器的调试和仿真过程图

图3 8051单片机与DDS芯片的连接关系图

图4 DDS芯片仿真结果图

四.结束语

本文介绍利用Multisim10设计出基于FPGA的直接数字频率合成系统的全流程。与传统电子电路设计方法相比具有如下特点:可以边设计边调试;设计的元器件及测试仪器仪表齐全可以完成各种类型的电路设计;可以方便地对电路参数进行测试和分析;可以直接打印输出实验数据,测试参数,曲线和电路原理图;设计中不消耗实际的元器件,所需元器件的种类和数量不受限制,设计成本低,速度快,效率高;设计成功的电路可以直接在产品中使用。

[1]聂典.Multisim 9计算机仿真在电子电路设计中的应用.电子工业出版社.2007

[2]潘松,黄继业编著.EDA技术实用教程.科学出版社.2002

[3]李云,侯传教,等编著.VHDL电路设计实用教程.机械工业出版社.2009

[4]张晓乡.89C51单片机实用教程.电子工业出版社.2009

10.3969/j.issn.1001-8972.2011.15.045