基于FPGA的NAND FLASH控制器的设计

2011-10-18李槐生

李槐生

(太原理工大学信息学院,山西 太原 030024)

随着科技的进步,电子产品已经以各种各样的形式进入到了千家万户。如人们每天接触的MP3、手机、数码相机、移动存储设备等电子产品。数据的存储是电子设备的关键技术之一。而目前应用最为广泛的存储介质就是NAND FLASH,它具有存储容量大、价格低廉、速度快等优点。对NAND FLASH的控制可以直接使用专用的控制芯片,这种方法比较简单,但是性价比较低,该芯片的部分功能得不到使用,造成浪费,兼容性较差。目前随着FPGA(即现场可编程逻辑门阵列)技术的发展,越来越多的工程师选择自己开发专用集成芯片。这种方法可以根据用户特有的需求来量身打造,且IP核可以与其它系统很好地集成互联,兼容性好。本设计就是用FPGA来实现了NAND FLASH的控制器,并通过测试验证了该IP核。

1 NAND FLASH控制器实现

本控制器所实现的是对NAND FLASH的读、写、擦除以及坏块处理等操作,其中利用FPGA内部RAM资源设计出32 K缓存,用来暂存FLASH中的数据,并留下控制端口,与MCU系统进行互联,使得MCU等对NAND FLASH进行操作时不需要考虑具体的控制时序以及坏块等问题,只需关注存储数据以及存储位置即可,使得MCU代码开发者不需要过多地考虑物理底层的设计,简化开发难度。控制器基本架构框见图1。

图1 NAND FLASH控制器

本设计选用的NAND FLASH为三星公司的K9F5608U0B,其容量为32 M×8 Bit。它有2 048个块,每块32页,每页有528个字节,其中每页的最后16个字节用来存储ECC校验码。FPGA选用的是Xilinx公司所生产的XC3S1000-4-FT256C。

1.1 FLASH控制模块

该模块作为整个控制器的核心模块,起到了协调各个子模块运行以及实现与MCU通信的作用。主要实现以下功能:

(1)首先接收到MCU发送过来的读写命令以及起始地址和数据总数。

(2)根据接收到的上述数据,该模块计算出起始块地址、起始页地址、终止块地址、终止页地址以及总共块数、总共页数。

(3)如果从MCU读命令,则用one page read命令来启动FLASH读模块,按页连续读取。

(4)如果从MCU写命令,启动FLASH写模块,并进行如下操作:①首先将起始块中未涉及到的页的内容用Sequential Row Read命令读取出来,并放入缓冲中;②对终止块中未涉及到的页进行上述处理;③对所涉及到的块,用erase命令全部擦除;④将缓冲的数据再放回到FLASH中原先的位置中;⑤开始从MCU接收数据,并用write命令,一页一页地写进FLASH中;⑥在写完之后,启动坏块处理模块,对所涉及的块进行扫描,确定坏块。

1.2 FLASH读模块

K9F5608U0B的读命令种类比较多,有READ1与READ2两种。Read2命令读取的是spare area,即存放ECC校验位的区域;Read1又可分为Read one page与Sequential Row Read1 Operation两种操作。Read one page即一次只能读一页,而Sequential Row Read1 Operation则可以连续读取多页。连续读取的范围仅限于本块当中,即如果控制器不发送停止该读命令的信号,则在读完本块的最后一页后Flash会自动停止读取。当然,大部分的命令识别工作已经由FLASH控制模块实现了。读操作模块中所写的状态机部分代码如下:

process(cu_st,read,r_b,counter_we,counter_re_cyc,counter_re)begin

case cu_st is

when por=>

when wait_cmd=>

when cmd_adr_input=>

when wait_busy=>

when wait_ready=>

when read_process=>

end case;

end process;

该状态机与控制模块配合便可实现FLASH读命令的各种时序。

图2 写模块流程图

1.3 FLASH写模块

从控制模块接收到启动命令,在接收了要写入的地址以及数据之后,开始启动状态机。写命令之前要进行块擦除,这个是由控制模块来协调的。流程见图2。首先写入write命令(80 H),之后输入地址,由于地址有3个字节,所以需要在3个WE周期将地址输入。首先输入列地址,之后两个字节为行地址(即页地址)。将ALE地址锁存信号拉低,依次输入一页的数据。输入program command(80 h),FLASH将R/B信号拉低,并开始写入数据。写完之后FLASH将R/B信号置高,FLASH控制器检测到R/B的变化,则输入read status command,从I/O 0口获取反馈,如果是0,表明写操作成功,否则失败。

2 擦除模块

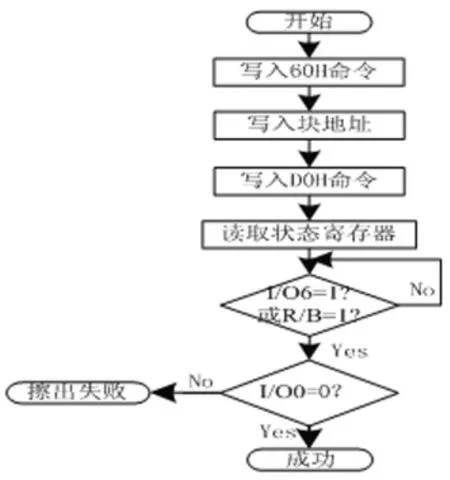

块擦除(Block erase)命令每次擦除一块,所以在系统设计中,要设计一个32 K缓冲。当要写一块数据时先将该块中有用的数据存储到缓冲中再进行擦除,防止数据的丢失。块擦除的工作流程见图3。

图3 擦除模块流程图

首先写建立擦除命令(60 h),然后写块地址,这儿的地址为两个字节。之后写擦除指令(D0 h),在擦除的过程中,R/B信号为低,擦除完成之后置高。这时控制器检测到R/B的高电位,输入read status command命令来读取状态。如果I/O 0为低说明擦除成功,为高则说明擦除失败。

每块flash难免会有坏块,但第一块要确保是正常的。厂商在出厂时就会在坏块上有相应的标记。Flash在使用之前,所有的字节都为FFH,但如果是坏块的话,厂商会在其第1或第2页的列地址为517处设置成non-FF,即spare field的第六个字节为非全1。

当所设计的系统准确度要求非常高的时候,对flash首先要做一次检测,确定有哪些坏块,并建立一个表来存储这些坏块的地址。而且在以后正常使用后,还要在每次擦除以及写操作之后读取flash状态,如果是状态为error的话就将这块的地址存储到坏块表中。

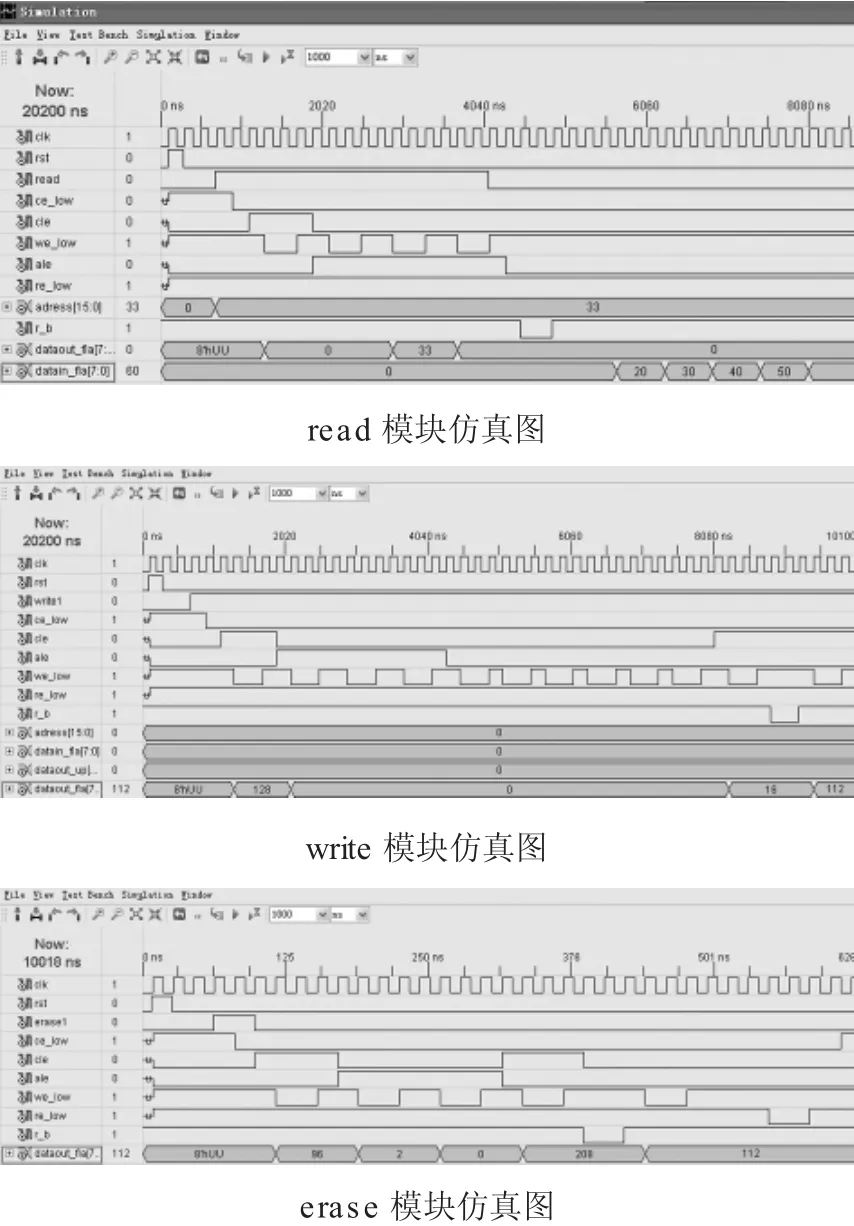

3 仿真验证

分别通过对读、写以及擦除模块的仿真,验证了该设计的正确性以及可行性。仿真结果见图4。

图4 仿真结果

4 结束语

NAND FLASH存储器已经成了存储介质的主流产品,而其控制器大部分是国外产品,加快集成电路设计行业的发展是我国的当务之急,利用FPGA可以设计出具有自主知识产权的IP核,并且增强了兼容性与灵活性。

[1]K9F5608U0B FLASH MEMORY datasheet.http://www.samsung.com.2003.

[2]曾祥萍.ISE集成开发环境下基于FPGA的数字设计.电脑知识与应用,No.12P.156-158.2006.

[3]杨之廉.超大规模集成电路设计方法学导论(第二版).清华大学出版社,1999.

[4]徐欣,于红旗等.基于FPGA的嵌入式系统设计.北京:机械工业出版社,2005.