基于FPGA的曼彻斯特编解码器设计

2011-10-09汤晓曦陈泉根

汤晓曦,尹 蕾,许 晏,陈泉根

(中国工程物理研究院 电子工程研究所,四川 绵阳 621900)

1553B总线是广泛应用于飞机综合航电系统、外挂物管理与集成系统的总线系统。并逐步扩展到飞行控制等系统及坦克、舰船、航天等领域。我国于1987年颁布了相应的军标GJB289《数字式时分制指令/响应型多路传输数据总线》。但是由于该标准的核心技术为欧美公司所垄断,因此,倘若能够自主研发基于1553B总线标准的协议芯片或产品具有重要的战略和经济意义[1]。随着可编程逻辑器件的高速发展,越来越多的设计者在FPGA、CPLD等的硬件基础上开展设计研究。本文基于FPGA的硬件基础设计实现了1553B总线中曼彻斯特II型码的编解码器。

1 1553B总线

MIL-STD-1553B总线网络由终端、子系统和总线传输介质组成。终端是使数据总线和子系统相连接的电子组件。子系统为从多路数据总线上接收数据传输服务的装置或功能单元[2]。总线控制器(BC)是总线系统组织信息传输的终端。总线监视器(BM)是总线系统中指定作接收且记录总线上传输的信息并有选择地提取信息以备后用的终端。远程终端(RT)是总线系统中不作为总线控制器或总线监视器的所有终端[3]。

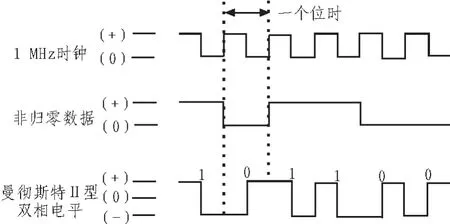

1553B总线的传输速度是1 Mb/s,采用曼切斯特Ⅱ型编码,半双工工作方式。信号以串行数字脉冲编码调制(PCM)形式在数据总线上传输。逻辑1为双极编码信号1/0,即一个正脉冲继之一个负脉冲,逻辑0为双极编码信号0/1[4],即一个负脉冲继之一个正脉冲。

图1 曼彻斯特II型码与NRZ码对比Fig.1 Compare of the Manchester II code and NRZ code

2 1553信号的3种传输方式

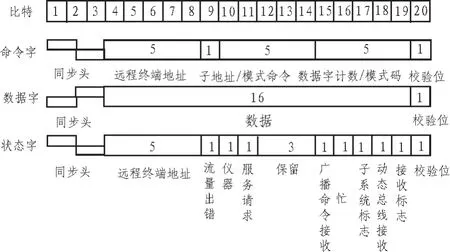

1553B信息流由一串1553B消息构成。1553B消息由命令字、数据字、状态字组成。所有1553B字都是20 bit[5]长,每个字都应是:

3位同步头+16位数据/命令/状态位+1位奇偶校验

3 曼彻斯特解码器设计以及仿真结果

解码器的工作方式就是从收发器接收曼彻斯特II型编码的串行数据,然后以并行数据的方式送出。而为实现,首先得实现同步头的检出,通过同步头来区别命令字数据字和状态字。然后解码串行数据,通过末尾的奇偶校验之后,再并行输出。

图2 1553B的3种数据传输格式Fig.2 3 formats of 1553B transmit in

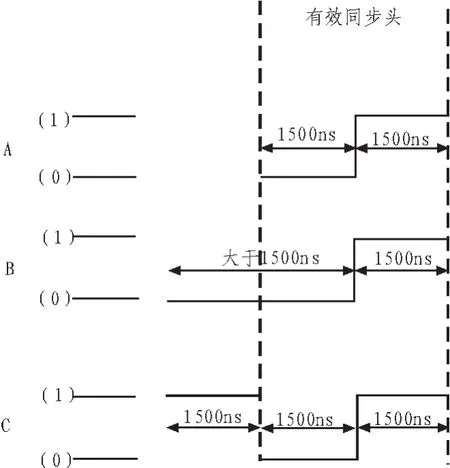

根据图2可以得知,1553B的同步头分为两种,而根据1553B协议,传输速率为1 Mb/s,因为一个有效的同步头占3个bit,它的传输时长应该为3 000 ns,而因为同步头前后电平的不同,以数据字同步头为例,分为以下几种情况[2]。

图3 数据帧同步头可能出现的情况Fig.3 Possible results of data-frame syncode

解码部分首先因该由判断同步头开始,这里用状态机来实现同步头的检测,而状态机的状态变化由在相应时间内有多少个连续相同电平的采样点决定。本次设计的采样与解码时钟频率均可采用5 MHz。这样以一个时钟上升沿作为采样点的间隔为200 ns。那么无论同步头的前半或者后半部分都应该采到大于7次,若少于7次,则判定为同步头检测失败,不能进入下一状态。而整个同步头应该采样15次。图3显示了数据字可能遇到的几种同步头的情况。

图3中A为理想情况的同步头。在检测出有效同步头后即进入数据接收解码状态。

图3中B为同步头开始前一直为低电平的情况,这需要状态机在第一个同步头计数器采样到7后如果采集点还为同样电平则一直将计数器置7,直道出现跳变再继续计数进入同步头的后半部分检测。

图3中C为在有效头部头之前有一个长度大于1 500 ns的干扰信号会直接导致状态机进入状态字或者数据字检测完毕的状态,这时需要在第一次采样时纠错,在进入预计的同步完毕的情况下(其实是误码干扰),若第一次采样的结果为同1或者(即采集到了同步头的真正后半部分),则状态机修正状态从判断为状态字或命令字进入数据字(或者从数据字进入命令字或者状态字),而所采集的第一个误码bit的数据会在下次采集时被覆盖。为下面介绍下本次设计的数据采样方式。

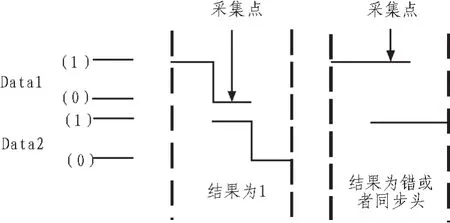

由于1553B使用的是曼彻斯特码II型码。不论传输的是0还是1,在该bit中间位置都会产生跳变,所以我用一个寄存器data2将该bit复制并延后半个bit位。然后同时对原信号data1和延后的data2采样如下图所示。

图4 信号采样方式Fig.4 Example of data sampling

如果data1为1,data2为 0,即为信号从 0变成1,则解码结果为0,反之则为1。在严格控制采样时刻必为data2的前半个电平后,采样结果中data1和data2是肯定不同的,倘若出现相同的情况,则必为电平错误或者正在传输的信号为同步头。

状态字和命令字的状态转移条件和示意图将在图5中给出。

状态机状态:idle(空闲)、s0(同步头前半部分为 0)、s01(同步头前半部分为 0后半部分为 1)、s01_r(数据字采集态)、s1(同步头前半部分为 1)、s10(同步头前半部分为 1后半部分为0、s10_r(命令字或者状态字采集态)。

图5 状态机以及转移条件示意图Fig.5 State machine indicator

在接收完16 bit的数据后,通过最末位bit的奇校验位校验完数据正确性后,通过并口dataout输出,至此,一字的解码采集结束。

解码通过串口以数据帧输入16 bit(1110001010001100)仿真时序结果如图6所示。

图6 曼彻斯特解码Modelsim仿真结果Fig.6 Modelsim result of Manchester decoder

4 曼彻斯特编码器设计以及仿真结果

本次设计的曼彻斯特编码主要由两部分组成:同步头生成部分和携带信息编码部分。

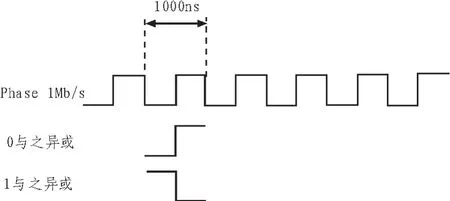

4.1 信息编码部分

根据1553B协议分析,在1 Mb/s的传输速度下,每个bit的传输时长为1 000 ns[6]。而本次编码的核心思想就是生成一个和同为1 Mb/s的周期信号phase,将并口接收的信号通过移位寄存器从高至低的一位一位的在符合1553B要求的时钟传输速率下与phase进行异或操作,当phase的波形与移位寄存器中的信号异或,若信号为0与之异或,结果为其本身,而当信号为1与之异或,结果phase的波形相反,正好符合1553B的传输方式。而得到的波形称之为enc_data。同时需设置一个busy编码指示位和bit_count编码计数器,分别用来标示当前是否处于编码阶段,能否读取新的并口数据和编码已经进行了多少位。编码是否完毕来将busy置0来接收新的并口数据。其波形如图7所示。

图7 phase的波形Fig.7 Shape of phase

4.2 同步头生成部分

同步头分为两种,状态字和命令字为一种[7],数据字为一种,这里还是以数据字为例。在相应的系统时钟下,设置一个计数器,在3 000 ns(一个有效同步头所占用的时间)内计数,当计数完成后(生成一个完整的同步头所需时间结束),对编码标志位busy置1(即可以开始数据编码)。而同步头的生成只需要根据需要生成的同步头在1 501 ns的位置跳变电平即可生成。以本次设计采用的100 MHz的系统时钟为例,即系统时钟周期为10 ns,利用一个系统时钟上升沿敏感触发的计数器,在同步头前半部分开始时计数,当计数到150时,也就是下一时刻在1 501 ns时让生成波形电平跳变,再持续150个计数器时间生成的同步头的后半部分。而这时具有同步头的波形叫enc_wave,然后在同步头生成结束后(即进入并口数据编码段)将enc_data的波形赋给enc_wave即可。这样得到的enc_wave即是符合1553B传输规则和速率的串口信号。

下面是并口依次输入11001001101000011和11100011 10001110后自动生成奇偶校验位和串口波形的modelsim仿真结果。

5 结束语

本设计根据曼彻斯特码型特点,设计出一种符合MIL-S TD-1553B协议的曼彻斯特编解码器。硬件描述语言采用verilog[8],选用ISE作为硬件综合工具,Modelsim作为仿真工具,通过准确的时间约束实现了1553B总线曼彻斯特码[9]编码器的设计,通过mealy状态机实现了1553B总线曼彻斯特码解码器的设计。与组合逻辑电路实现相比较更具有优越性。本模块已应用于基于硬件FPGA来实现1553B总线和光纤总线的协议转换板,经过验证,解码正确。具有很强实用性。

[1]武鹏,毕君懿.1553B总线中曼彻斯特编解码器的设计[J].现代电子技术,2011,34(4):61-64.

WU Peng,BI Jun-yi.Design of manchester codec in 1553B bus[J].Modern Electronics Technique,2011,34(4):61-64.

[2]牛茜,靳鸿,基于有限状态机的1553B总线解码器设计[J].电子测试,2010(12):74-78.

NIU Qian,JIN Hong.Design of the Manchester II decoders for the 1553B bus by state machine[J].Electronic Test,2011(12):74-78.

[3]张飞,王焕玉,徐玉朋,等.基于FPGA控制实现的1553B总线通讯设计[J].航天控制,2010,28(6):67-71.

ZHANG Fei,WANG Huan-yu,Xu yu-peng,et al.1553B2Bus communica tion design based on FPGA control[J].Aerospace Control,2010,28(6):67-71.

[4]曹素芝,张善从.光纤通道与MIL-STD-1553B协议的兼容性设计[J].计算机测量与控制,2010,18(7):1624-1626.

CAO Su-zhi,ZHANG Shan-cong.Design on bridge between fiber channel and MIL-STD-1553B[J].Computer Measurement&Control,2010,28(6):67-71.

[5]孙涛,张华春.基于1553B协议的总线控制器和远程终端的FPGA 实现[J].中国科学院研究生院学报,2010,27(4):523-529.

SUN Tao,ZHANG Hua-chun.Realization of FPGA-based MIL-STD-1553B bus remote terminal’s controller[J].Journal of the Graduate School of the Chinese Academy of Sciences,2010,27(4):523-529.

[6]张传武,黄勤珍.Mil-Std-1553总线协议分析[J].西南民族大学学报:自然科学版,2007,33(2):381-383.

ZHANG Chuan-wu,HUANG Qin-zhen.Protocol analysis of the Mil-Std-1553 bus[J].Journal of Southwest University of Nationalities:Natural Science Edition,2007,33(2):381-383.

[7]胡亚平.1553B远程终端的设计 [J].安徽电子信息职业技术学院学报,2008,7(4):55-56.

HU Ya-ping.The design of 1553B remote terminal[J].Journal of Anhui Vocational College Electronics& Information Technology,2008,7(4):55-56.

[8]夏宇闻.Verilog数字系统设计[M].北京:北京航空航天大学出版社,2008.

[9]USA:Department of Defence.MIL2STD21553B digital time divi2sion command/response multiplex data bus[S].1978.