基于VHDL的多功能数字闹钟设计

2011-09-29万军华刘瑞通

万军华,刘瑞通

(1.湖南理工学院 信息与通信工程学院,湖南 岳阳 414006;2.西南交通大学 电气工程学院,成都 610031)

基于VHDL的多功能数字闹钟设计

万军华1,刘瑞通2

(1.湖南理工学院 信息与通信工程学院,湖南 岳阳 414006;2.西南交通大学 电气工程学院,成都 610031)

针对多功能数字闹钟的设计提出了三种可行性设计方案,并对这些方案的优缺点进行了比较论证,在充分考虑各种方案优缺点的前提下,选择利用FPGA芯片来设计多功能数字闹钟.本设计选用可编程器件FPGA采用硬件描述语言VHDL按照自顶向下的设计方法设计了数字闹钟的各个模块,并对各个功能模块进行了软件仿真.

VHDL;FPGA;数字闹钟;状态机;电子琴

引言

随着电子技术的发展,特别是大规模集成电路的研制和发展,电子电路的设计变得越来越复杂,这使得采用了“自顶向下”设计思想的EDA解决方案得到了广泛的应用,从而极大地提高了设计效率,缩短了产品的研制周期.再加上其采用硬件描述语言作为输入、库的引入、设计文档管理、强大的电路仿真功能和知识产权的保护等优点[1],使其在现在大规模电子设计中得到了广泛的应用.

硬件描述语言VHDL是EDA的重要组成部分,VHDL语言具有很强的电路描述和建模能力、与具体硬件电路无关和与设计平台无关的特性,以及良好的电路行为描述和系统描述能力.

针对现代社会生活对时间观念越来越重视和对生活质量要求越来越高的现状,本文设计了一种以FPGA为核心、以Xilinx公司的ISE为开发工具、以VHDL为硬件描述语言的多功能数字闹钟.

1 设计方案的提出

能满足多功能数字闹钟设计要求的设计方案有以下三种.

方案一:利用纯数字芯片实现数字闹钟的设计

采用外部6MHz晶振作为脉冲源,然后由14位分频器CD4060和计数器74HC190进行分频得到1Hz的时钟.然后由6个十进制计数器74HC190来分别完成时、分、秒位的BCD码计数.用8个四线—七段锁存译码器/驱动器CD4511实现七段数码管的编码、驱动,使用LED显示时分秒.其定时功能由8位数值比较器74HC688完成时、分位的比较,然后驱动蜂鸣器.

方案二:利用AT89S52单片机实现数字闹钟的设计

利用单片机内部的定时/计数器进行中断定时,配合软件延时实现对时、分、秒的计时.在上电后系统自动进入时间显示,通过按下时间设定/启动计时键,系统停止计时,进入时间设定状态,系统保持原有的显示,等待键入当前时间,根据需要按相应的数字键可以顺序设置时、分、秒,并在LED上显示设置值,设置完毕后,系统将从设定后的时间开始计时显示;当按下闹钟键时,进入闹钟模式,到设定时间时蜂鸣器鸣响.

方案三:利用FPGA芯片实现多功能数字闹钟的设计

利用FPGA精度高、处理速度快的特点,利用外部50M石英晶振提供高精度系统频率,经分频得到所需要的不同频率时钟,利用软件消除按键抖动,分别设计了百分之一秒、秒、分和时计时,分、时调时,整点报时和闹铃等功能,闹铃的铃声有不同选择,由软件直接控制、编码的显示功能.

综上所述,第一种方案,全由数字芯片构成,芯片数目比较大,外围电路比较复杂,给设计和制作带来很多不便,并且容易出现电路不稳定、精度低、开发周期长等问题;第二种方案,外围电路比较简单,利用单片机的内部定时器完成计时功能,但其精度不是很高.第三种方案,外围电路比较简单,精度较高,能够满足更高精度的要求,并且设计比较人性化.

本文采用第三种方案设计了多功能、人性化、精度高、外围电路简单的多功能数字闹钟.

2 系统整体设计

本设计选用可编程器件FPGA采用硬件描述语言VHDL按照自顶向下的设计方法设计了多功能数字闹钟.该数字电子闹钟主要包括时钟分频、消除抖动、百分之一秒计时、秒计时、分计时−分设置、时计时−时设置、显示选择控制、总控制、设定时间比较、闹钟铃声和显示输出等11个模块.图1为此系统的设计顶层文件方框图.

图1 顶层文件方框图

在复位信号Reset有效时,计时和调时的所有位都复位.当复位信号Reset无效、显示选择信号Choose为低时,进入正常计时模式,由分频器产生的100Hz频率的信号作为百分之一秒计时的时钟信号进入正常计时状态,百分之一秒采用100进制的BCD码计数,当计数到99后,再来一个计时脉冲,此位变成0并向秒位输出一个计时脉冲;秒计时采用60进制的BCD码计数,当计数到59后,再来一个计时脉冲,此位变成0并向分计时输出一个计时脉冲;分计时也采用60进制的BCD码计数,与秒计时的工作方式一样;时计时采用24进制的BCD码计数,当计数到23时,再来一个脉冲则变成0.用选择键信号En分别选择调时和调分的位,被选中调整位闪烁,通过加一键Add来调整此位的值.当选择信号Choose为高时,进入定时模式,数码管只显示时、分定时位,也是通过选择信号En选择相应的定时位,加一键Add来调整相应的值.当定时时间和计时时间相同时,Bell根据音节频率的不同输出一分钟悦耳音乐;当整点时输出整点报时音乐.

设计采用了外部 50MHz石英晶振作为频率源,提高了时钟的精确度;采用电子琴乐曲设计方法设计铃声,给人以悦耳的闹铃和整点报时铃声;在设置和调整时间时,采用相应位闪烁技术,使用户方便操作.

3 主要模块的设计介绍

3.1 消除抖动模块

由于弹性作用的影响,按键的机械触点在闭合及断开的瞬间都会有抖动的现象,即不能马上实现按键的完全闭合或断开,从而使输入电压信号也出现抖动现象,抖动时间的长短由按键的机械性决定,一般为5~ 10mS[2].

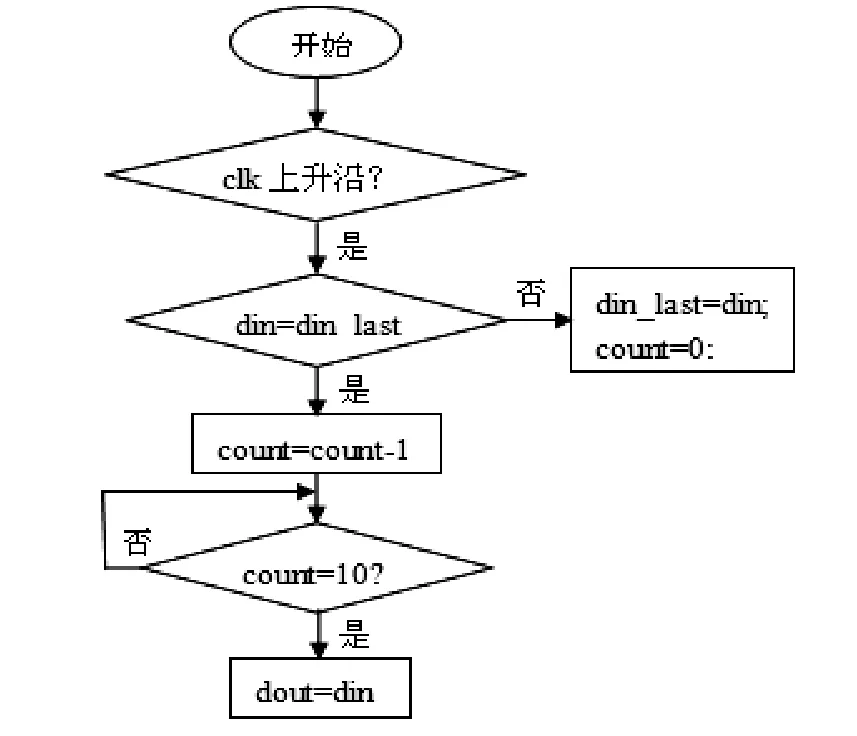

本设计中采用对按键输入信号 din延时计数10mS后,如果按键仍被按下,则判断为有效按键;否则此信号为无效信号.其流程图如图2所示.

图2 消除抖动模块流程图

3.2 分计时-分设置模块

此模块主要实现分计时、分调整和分设定的功能.分计时功能是实现对正常时间分位的计时,并产生时计时信号;分调整功能是校正数字闹钟分位;分设定功能是闹钟分位数值的设定,它通过调时/定时信号键Choose和分选择信号min选中,然后通过加1信号键Add对分位进行调整.

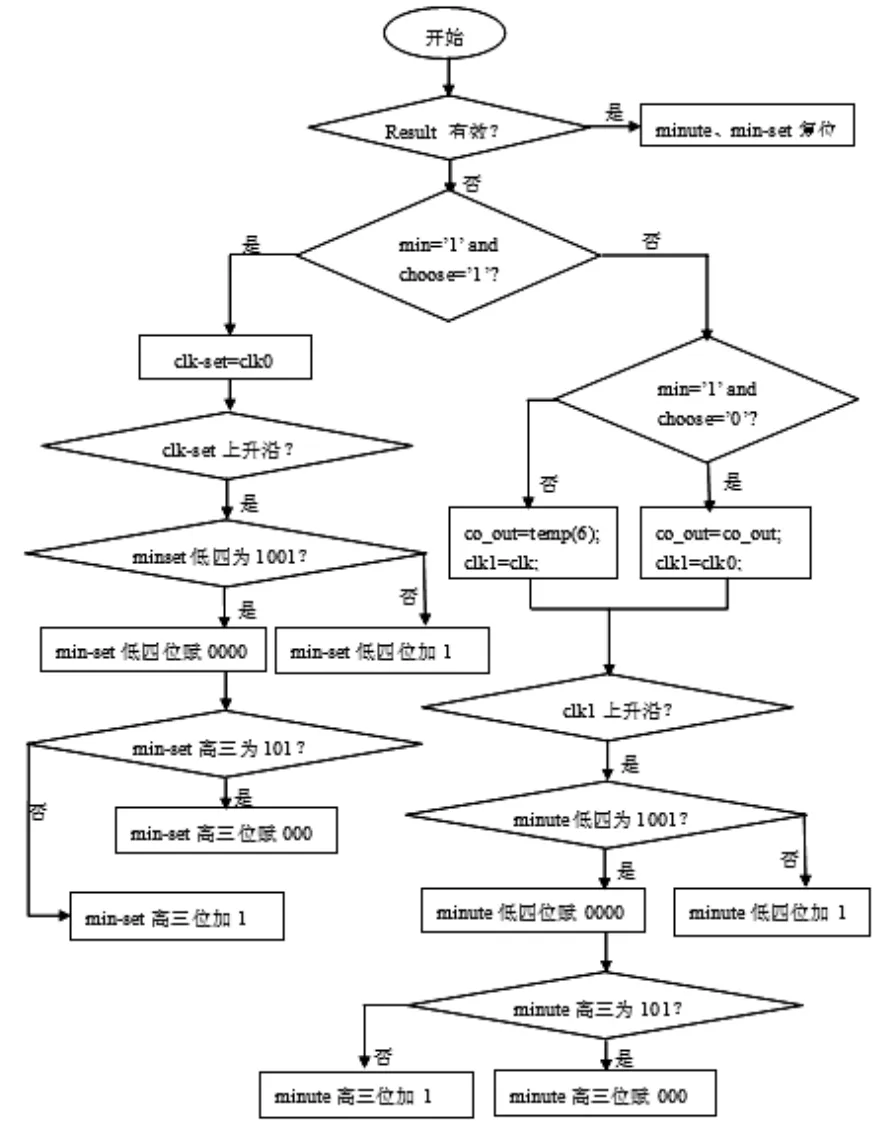

当复位信号 Result为“1”时即复位信号有效,minute、minute_set复位;而Result为“0”时,如果调分信号min和选择信号Choose同时为“1”时,通过加1键Add对闹钟分位minute_set进行手动设定;当调分信号min为“1”且选择信号Choose为“0”时,实现对计时分位 minute调整;当调分信号 min为“0”时,进入正常计时状态.此模块的计数采用了十进制计数,并且把个位和十位的数字分别采用BCD码计数,方便用LED显示.

此模块把计时、定时和调时三大功能放在一个模块中实现,简化了程序,也减少了整个系统的模块个数,使整个系统的设计更加简单、方便.但此模块的程序整体来看比较难理解,并且不太容易分析.其流程图如图3所示.

图3 分计时-分设置模块流程图

3.3 控制模块

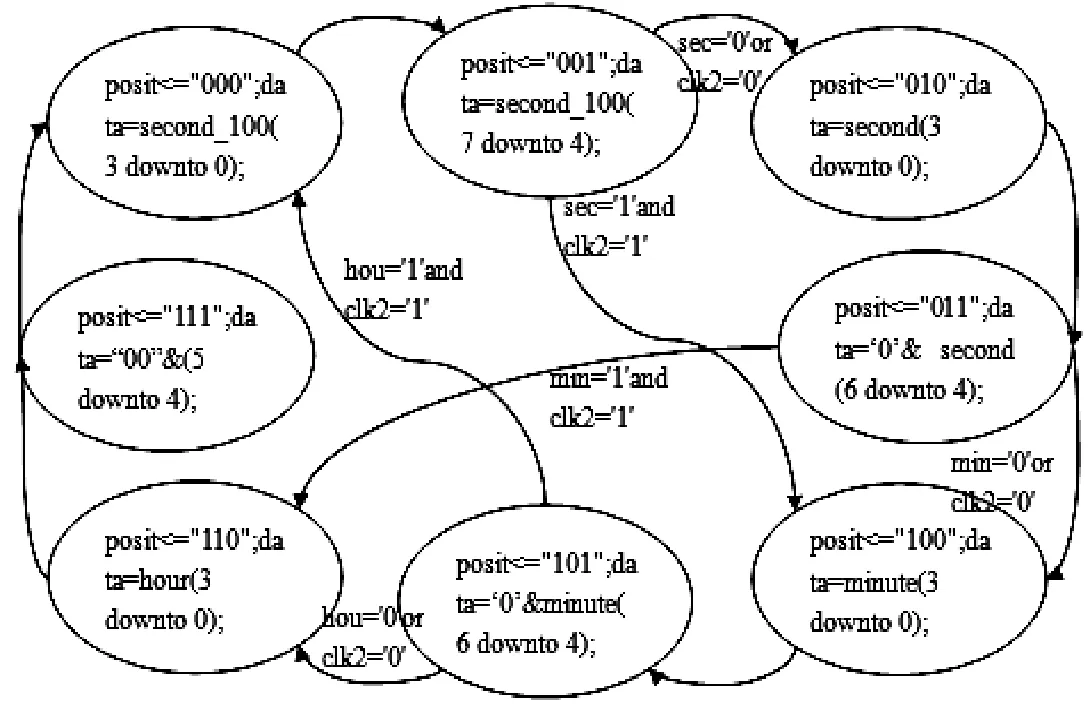

此模块用状态机[3]实现控制LED显示的数据和位置.当选择信号Choose为“1”时,进入定时显示模式,根据min、hou和clk2信号来选择显示的数据和位置,并确定下一个状态;当选择信号Choose为“0”时进入计时显示模式.此模块也是实现对相应调整位闪烁的重要控制模块,在显示闪烁信号和闪烁时钟信号都有效时,此位闪烁显示;闪烁时钟无效时此位不显示.控制模块的状态图如图4所示.

图4 控制模块状态图

3.4 闹钟铃声模块

此模块是根据八音符电子琴自动演奏乐曲设计的.八音符电子琴系统[4,5]由数控分频器和乐曲存储模块组成.数控分频器对FPGA的基准频率进行分频,得到与各个音节对应的频率输出.乐曲存储模块产生节拍控制和音阶选择信号,即在此模块中可存放多个乐曲曲谱真值表,有一个计数器来控制相应真值表的输出,由计数器的计数时钟信号作为乐曲节拍控制信号.

数控分频模块对时基脉冲进行分频,得到与1、2、3、4、5、6、7七个音符对应的频率.

音调发生器的作用是产生获得音阶的分频预置值.当8位发声控制输入信号index中的某一位为高电平时,则对应某一音阶数值将在端口tone输出,该数值即为该音阶的分频预置值,分频预置值控制数控分频器来对4MHz的脉冲进行分频,由此可得到每个音阶对应的频率.

音乐存储模块的作用是产生8位发声控制输入index.由存储在此模块中的8位二进制数作为发声控制输入,可自动演奏乐曲.

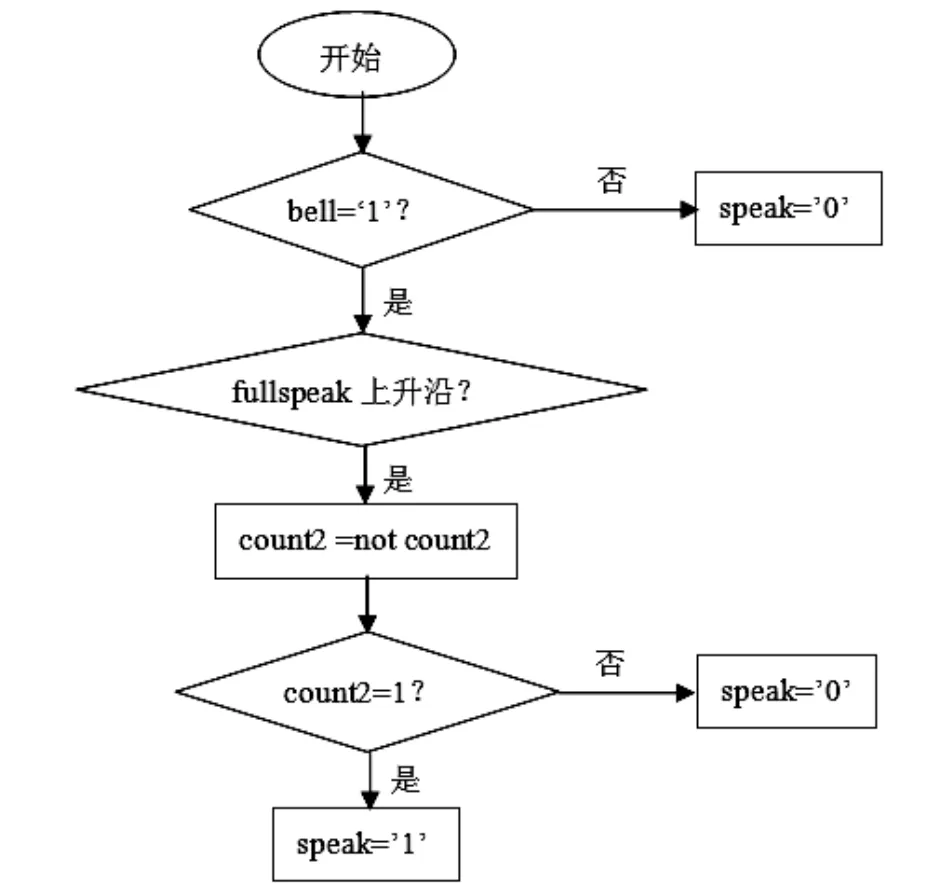

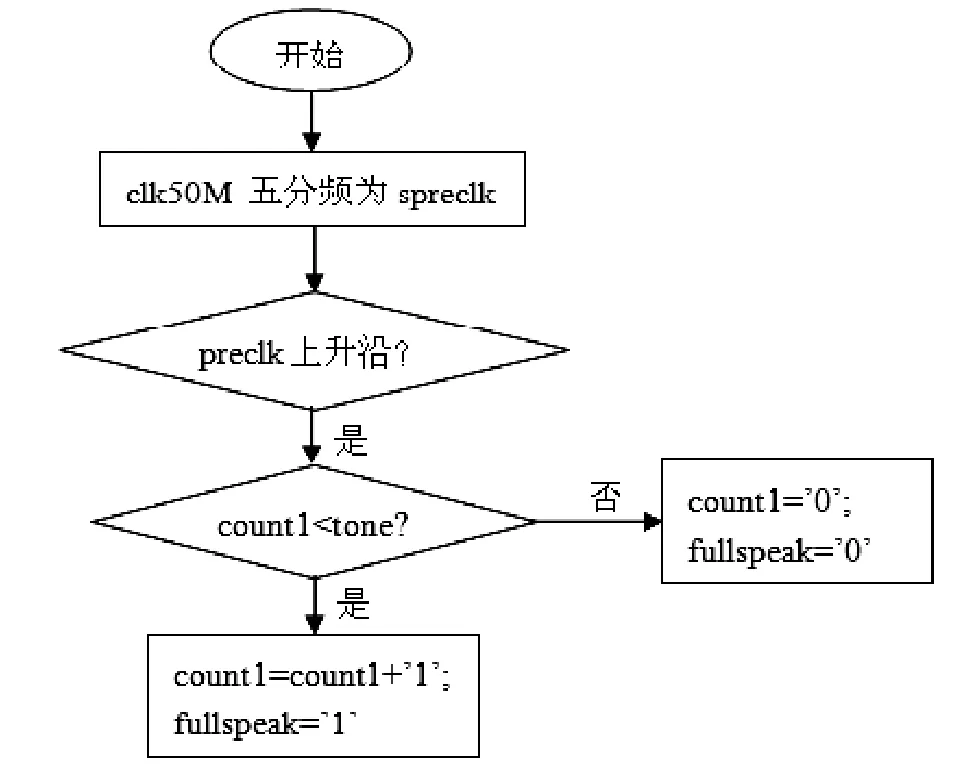

由于本设计中加入了闹钟铃声和整点报时模块,在闹铃时能够发出比较委婉的音乐,能够使使用者生活在一个相对和谐的环境中,和悦的音乐作为闹钟的铃声也使刚从睡梦中醒来的使用者不被惊吓,并且很容易从睡梦中清醒去处理自己的事情.其流程图如图5和图6所示.

图5 乐曲模块流程图

图6 数控分频器模块流程图

4 部分功能模块的软件仿真

本设计的软件仿真采用了Xilinx公司ISE软件上的Simulation,对各个功能模块进行了波形时序的仿真,经过分析各个模块时序都是准确的.下面是典型模块的仿真图:

图7 消除抖动仿真波形图

图8 分计时-分设置仿真波形图

图9 控制功能仿真波形图

5 总结

本文采用硬件描述语言VHDL编写、利用Xilinx公司的ISE仿真软件开发实现多功能数字闹钟各个模块的功能,提出了一种方便实用的多功能数字闹钟设计方案.整个系统的程序下载到硬件中,经测试所有的设计功能都能实现.

[1]潘 松,黄继业.EDA技术实用教程[M].北京:科学出版社,2006:7~10

[2]赵全利,肖兴达.单片机原理与应用教程[M].北京:机械出版社,2004:162~163

[3]邱玉娟.基于FPGA的数显测温系统的设计[J].自动化技术应用,2008,27:93~95

[4]张 亮,罗小巧,董继承.基于FPGA的乐曲演奏器的设计[J].电子技术,2007,(09):101~102

[5]熊 杰,彭 力,薛德恒,等.简易电子琴设计[J].企业技术开发,2009,(05):33

Design of Multifunctional Digital Clock Based on VHDL

WAN Jun-hua1, LIU Rui-tong2

(1.College of Information and Communication Engineering,Hunan Institute of Science and Technology,Yueyang 414006,China;2.School of Electrical Engineering,Southwest Jiaotong University,Chengdu 610031,China)

Three feasible proposals are given aiming at the design of multifunctional digital clock and the strong and weak points among the proposals are compared.And then,taking all kinds of strong and weak points into consideration,the multifunctional digital electronic clock is designed by using FPGA.The modules of the digital electronic clock are designed using programmable device FPGA and hardware description language VHDL in accordance with the method of top-down design,and each module are simulated with software.

VHDL;FPGA;digital clock;state machine;electronic organ

TP271

A

1672-5298(2011)01-0067-05

2010-11-03

万军华(1969− ),男,湖南岳阳人,湖南理工学院信息与通信工程学院高级实验师.主要研究方向:控制工程