基于CPLD的LVDS数据传输系统的设计与研究

2011-09-12郭鹏翔祖静尤文斌

郭鹏翔, 祖静, 尤文斌

(中北大学仪器科学与动态测试教育部重点实验室,太原,030051)

0 引言

随着信息化的高速发展,工程人员面临着大数据量的高速传输问题。采用低电压差分信号LVDS技术的设备电路系统可使传输速度每秒高达数百Mb,可以很好地解决这一瓶颈问题[1-2]。另外本设计中还引入了FIFO芯片作为缓冲给LVDS发送端,从而确保数据的高速传输不会中断。同时应用CPLD对FIFO以及LVDS器件进行时序精确,逻辑准确的操作,以达到设计要求。最后应用Modelsim软件对设计系统进行了时序仿真以验证其达到了所需要求。

1 系统工作流程

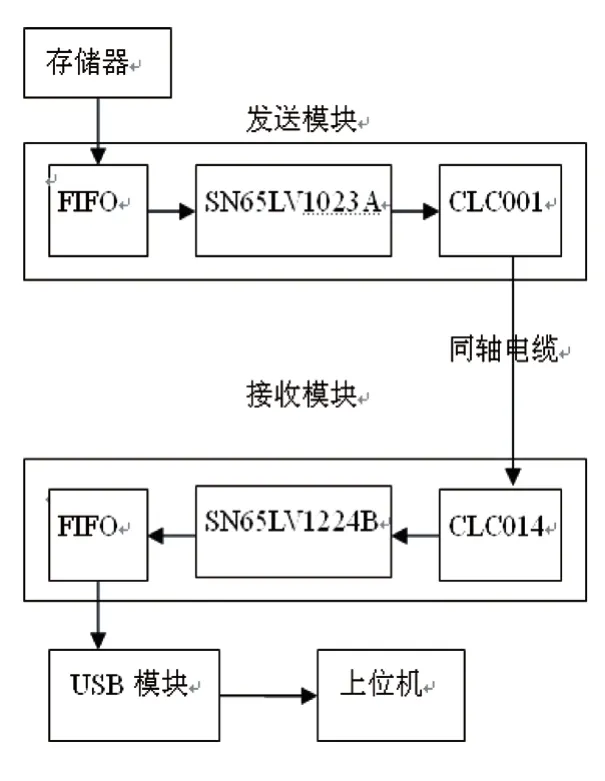

系统设计框图如图1所示。以模块化设计,主要分为LVDS发送模块,LVDS接收模块,USB模块。系统从存储器中读取的数据通过LVDS总线高速传输给USB模块,可以在上位机进行存储与实时显示。

2 系统原理

本系统的LVDS器件选用美国国家半导体公司推出的10位总线型低压差分信号芯片组SN65LV1023A、SN65LV1224B。其中SN65LV1023A是可将10位并行CMOS或TTL数据转换为具有内嵌时钟的高速串行差分数据流的串化器[3];而SN65LV1224B则是接收该差分数据流并将它们转换为并行数据的解串器,它同时又可以重建并行时钟[4-5]。采用该器件组进行数据串化时采用的是内嵌时钟,这样可有效地解决由于时钟与数据的不严格同步而制约高速传输的瓶颈问题。

图1 系统组成框图

上电后,两芯片分别置所有输出管脚为三态,而后启动锁相环跟踪并锁定本地时钟(对于串化器为TCLK,对于解串器为REFCLK)。当解串器检测到LVDS输入端的边缘跳变后,它试图锁定到内部嵌入时钟[6]。当解串器内部锁相环锁定到输入的数据时,解串器LOCK输出端为高;当解串器锁定到LVDS数据时,LOCK输出端变低。所以只有当LOCK为低时,此时解串器的输出才是为输入端的LVDS数据。在数据传输过程中一旦解串器中的锁相环失锁,LOCK位将变高。这时解串器锁相环会在较短时间内自动再次锁定到内部嵌入时钟以达到再次同步[7]。

在实际情况下,如果出现失锁,串化器会继续发送数据,解串器会在很短时间内(小于500µs)重新完成同步[8],但是在这个时间内解串器输出的数据并不是输入端的LVDS数据。即输入端的LVDS数据会有部分遗漏由于失锁。对于大容量数据的高速传输,这部分遗漏的数据对接收端数据的完整性会有较大的影响。为此,本设计在CPLD内部设置了一选通功能,使得系统在失锁的这段时间内,CPLD会内部发假数据给串化器输入端,直至系统再次同步。并且在发假数据的同时,会发送标志位R8=0,从而在接受模块接收数据时,可以根据R8的数值来甄别真假数据。

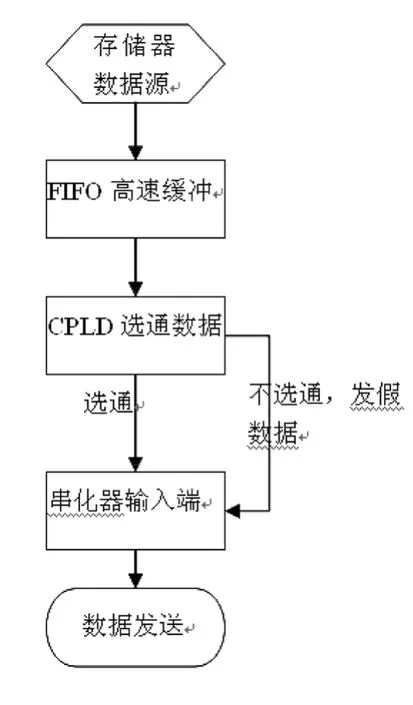

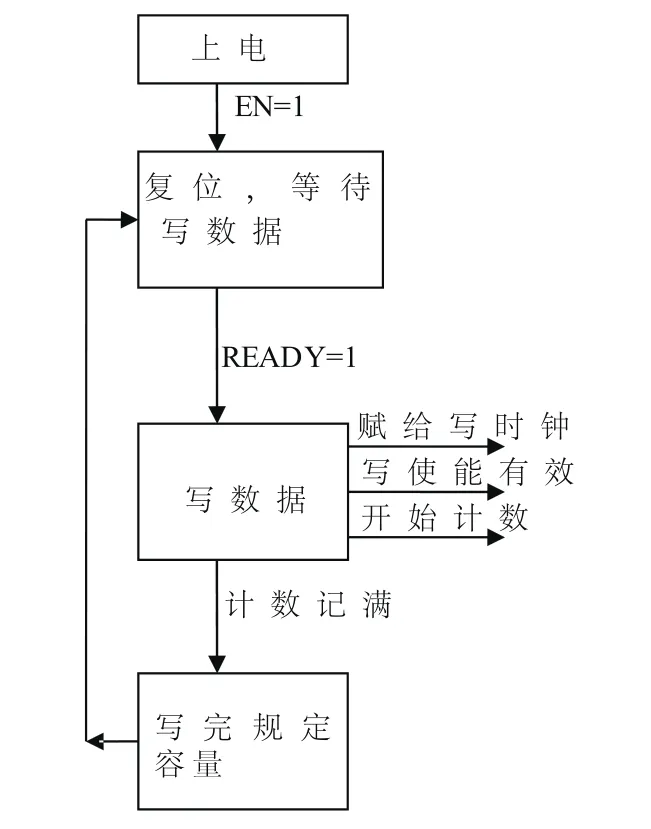

以发送模块为例,它的工作流程如图2所示。

图2 发送模块组成框图

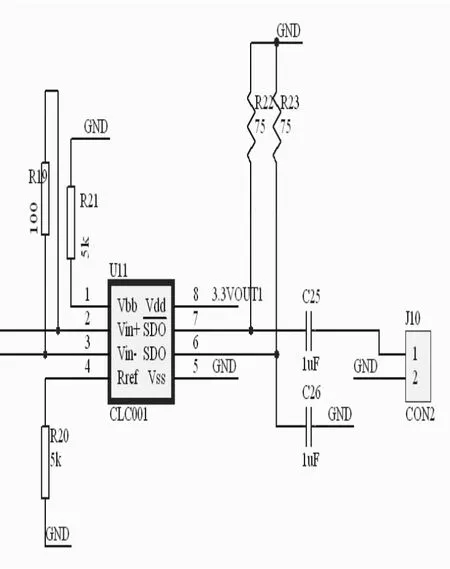

本设计中发送模块采用的串化器SN65LV1023A的具体电路连接图如图3所示。高速驱动器CLC001的电路连接如图4所示。在发送模块中,由于是高速数据传输且在传输过程中可能会出现短时间(小于500µs)的失锁,所以本方案中特地引入了FIFO芯片IDT72V241,从存储器读取的数据先写入FIFO,在确认系统同步的情况下,再将FIFO中数据读出赋给串化器。从而确保数据的有效性,且保证了数据高速传输的不间断性。可见,在发送模块中,通过CPLD控制FIFO芯片的读写操作是实现LVDS高速传输且不丢失有效数据的关键。

图3 串化器SN65LV1023A连接图

图4 高速驱动器CLC001电路连接图

3 CPLD程序设计

FIFO芯片IDT72V241的容量为4096x9 bit。CPLD采用XILINX公司的XCR3128,其内部程序采用模块化设计。分为复位,写FIFO,读FIFO 3个模块。

3.1 复位模块

与许多芯片类似,FIFO芯片在正常工作之前,也需要进行复位操作。本设计中CPLD在检测到EN信号变高后,会先赋给FIFO复位管脚RS端一个低脉冲(不小于120ns),使得FIFO芯片复位,以准备好下一步的工作。

3.2 写FIFO模块

在本设计中,大容量的数据在进入LVDS系统传输前先经过FIFO芯片进行数据缓冲。用CPLD控制数据写入FIFO的过程可以用状态图来表示,如图5所示。

图5 写FIFO流程

3.3 读FIFO模块

FIFO中的数据都是有效数据,在被读出后通过CPLD赋给串化器的输入端,从而通过LVDS的数据形式发送出去。如前面所述,在这个传输过程中,可能会出现短时间(小于500µs)的失锁,这是为了防止FIFO内有效数据的丢失,应停止读取FIFO中的数据,并通过CPLD赋值假数据给串化器直到再次同步完成。

4 仿真结果

根据CPLD内部各模块的设计思想,在XILINX ISE9.1环境下编辑程序,并在MODELSIM软件中通过时序仿真来验证构想的正确性。通过各仿真时序图来看,程序很好地完成了设计要求。

各模块仿真结果如下。

4.1 复位模块仿真

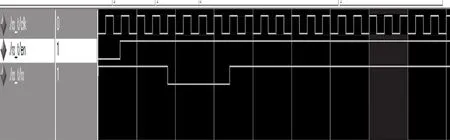

时序仿真如图6所示。

图6 复位模块仿真图

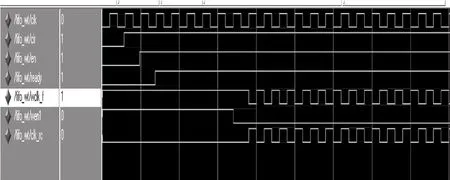

4.2 写FIFO模块仿真

该模块时序仿真如图7所示。图中wclk_f信号为FIFO的写时钟信号。WEN1为FIFO的写使能信号,低有效。

图7 写FIFO模块仿真图

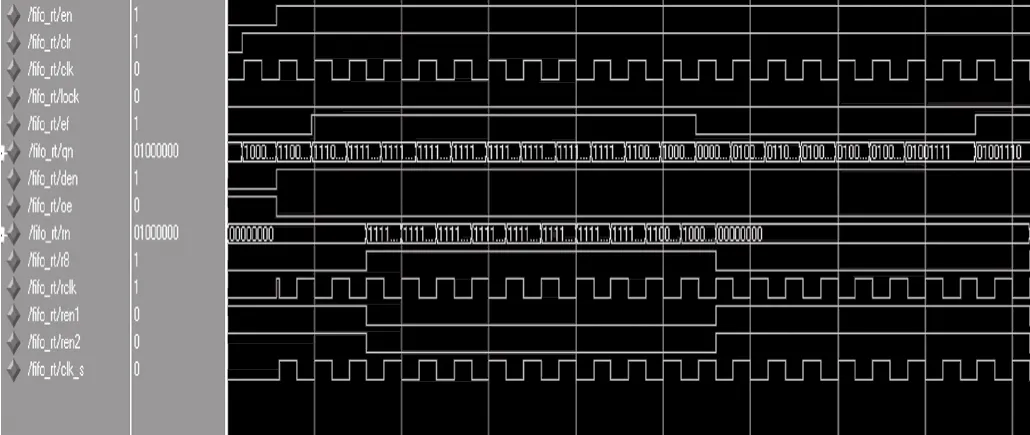

4.3 读FIFO模块仿真

该模块时序仿真如图8所示。

图8 读FIFO模块仿真图

5 结束语

本文设计的基于CPLD的LVDS总线高速数据传输系统,充分考虑了实际情况中可能出现的失锁现象,做到高速数据传输的同时且不丢失有效数据。有着非常好的应用前景。

[1]陈一新.基于USB+LVDS的FPGA远程测试系统[J].电子测试,2009(4):73-75.

[2]刘祥远,陈书明.LVDS 高速 I/O 接口单元的设计研究[J].计算机工程与科学, 2001,23(4):54-58,62.

[3]来卫国.基于无线激光通信的数字视频接收机的研究[J].国外电子元器件,2002(2).

[4]倪春波,应建华,刘三清,等.LVDS高速I/O接口电路设计[J].华中科技大学学报:自然科学版,2003,31(10):16-18.

[5]薛隆全,文丰,张时华.基于LVDS总线的高速长距数据传输的设计[J].电子设计工程,2009(2).

[6]杨建义.基于Visual Basic与RS232串行通信的温度监测系统[J].电子测试,2007(12):47-50.

[7]National Semiconductor .LVDS Owners' Manual[R].National Semiconductor , Spring 1997.

[8]彭乡琳.LVDS在长距离信号传输中的应用[J].兵工自动化,2006(7).