基于SystemC的片上网络仿真实验研究

2011-08-16任胜兵潘震宇张万利

任胜兵,潘震宇,卢 念,张万利

(1.中南大学 软件学院,湖南 长沙 410075;2.中南大学 信息科学与工程学院,湖南 长沙 410083)

0 概述

芯片制造工艺飞速发展,芯片上元件的集成度也越来越高,片上系统SoC的结构日益复杂。为了获得更高性能的SoC,采用点到点专用的或分布式的片上网络NoC(Network on Chip)成为可替代片上共享总线系统的新型解决方案。

在嵌入式系统多核课题中,目前NoC技术成为解决SoC互联问题的研究热点,关于NoC的研究主要集中在任务映射和路由器等[1]。软件模拟和综合成硬件是NoC领域主流的分析方法[2]。考虑到教学实验和创新研究的通用性和灵活性等特点,综合定制芯片原型无助于由浅入深地理解NoC的体系结构,且因其特性固定故不适合进行灵活地实验,再者原型实际测量工作很复杂,教学实验并不适合采用综合芯片原型的方法。软件建模和模拟方法对于设计流程、模块集成和NoC概念的验证相当重要。在设计NoC时,有一个具备分析处理单元、片上互联等性能参数的仿真实验平台,对研究NoC的实验教学以及创新设计有重要意义。

本文以NIRGAM[3]模拟器作为NoC仿真实验平台,因其开源、文档丰富、支持完善和程序稳定可靠等优点,且基于SystemC开发便于未来进行软硬件协同设计和验证。

1 NoC的架构分析

本文所研究的NoC体系结构通常由路由节点、网络接口以及处理单元三种基本要素构成[5],如图1所示。

图1 NoC基本结构

1)路由节点实际上相当于计算机网络中的交换机,它的功能是保障数据能够成功地到达目的地。以较流行的2D MESH NoC拓扑结构为例,一个路由节点拥有4个方向端口,分别与邻居节点的对应方向端口通过物理链路相连,还有1个本地端口与本地处理单元保持连接。路由节点根据路由算法选择端口做下一步转发。路由算法的优劣不仅对传输时延,还对网络能耗和容错能力产生影响。

2)网络接口起到了数据连接和转换的功能。

3)处理单元实际上是任何异构的IP核,如微处理器核、DSP核、微控制器核、存储器核或I/O设备控制器核等,也可以是SoC中各个任务进程的抽象化,分为发送器、接收器和加工器三大类[6]。

2 基于SystemC的NoC实验平台

SystemC是由OSCI(the Open SystemC Initiative)开发的统一建模平台,为系统设计提供了统一的语言以便更好地进行软硬件协同设计和验证。它在C++基础上添加一个SystemC类库。类库是采用C++编写的各种函数和数据类型等的程序库,将并发、时钟和特殊数据类型等硬件描述概念引入C++,使其能够对硬件进行建模描述。

基于SystemC的NoC仿真实验平台主要有三个:Noxim、NIRGAM 和NNSE。

1)Noxim由意大利卡塔尼亚大学的计算机体系结构团队开发和维护。Noxim以命令行形式对模拟器中NoC的拓扑、缓冲区、数据大小分布、路由算法、交换算法、数据注入率、流量类型和分布进行配置,以吞吐量、时延和能耗作为性能参考。

2)NIRGAM由英国南安普顿大学电子与计算机科学院电子系统设计团队和印度Jaipur Malaviya国家技术研究所计算机科学与工程系联合开发。NIRGAM是一个模块化设计,可扩展的NoC模拟器,能够对拓扑、虚通道、缓冲区、路由算法以及IP核进行配置,可以方便地对模拟器进行扩展,如新的IP核和路由算法,以平均时延和吞吐量作为性能参考。

3)NNSE由瑞典皇家技术研究所电子、计算机和软件系统系研究开发。NNSE支持AXI,属性配置以XM L形式对拓扑、流控机制、路由算法及流量类型等进行配置,以时延和吞吐量作为性能参考。

3 NIRGAM仿真实验平台教学实验

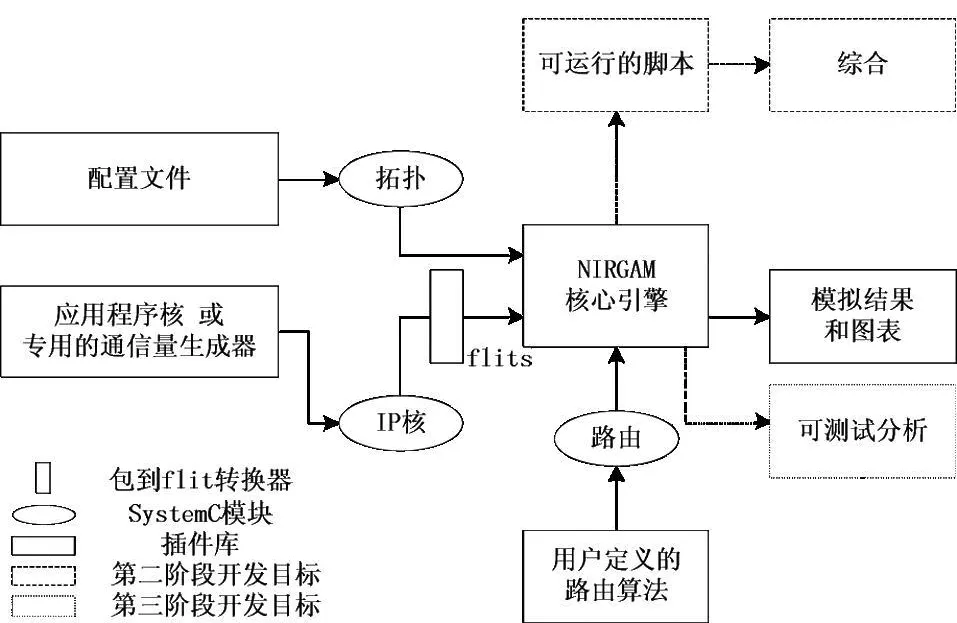

NIRGAM仿真实验平台的核心引擎从配置文件nirgam.config中获取模拟器配置,从配置文件application.config中获取任务映射结构,然后按此构建NoC实验平台并全局控制仿真工作。NIRGAM仿真结束后,将期间采集到的信息进行统计并保存成文件,以供导出分析和绘制 Matlab或gnuplot图表。

图2 NIRGAM仿真实验平台架构[3]

学生通过对NIRGAM模拟器的解析,可以较直观地从不同层面上理解NoC体系结构及其基本的通信机制,并通过亲自动手配置模拟器的参数来加深对概念的消化理解。在此基础之上对NoC课题展开多方面的兴趣研究。以下介绍两个典型的实验,分别对处理单元和路由算法的设计做了简单的实现和分析,以此表明利用NIRGAM模拟器对NoC的教学研究具有可行性。

3.1 NIRGAM处理单元设计实验

罗丹提出将流量生成机制与注入机制封装在一个处理单元内部,可以在不影响处理单元内其他模块时,仅改变流量生成机制以此改变资源子网向通信子网发送的数据特征,全面地评估NoC性能[7]。

本文构建了一组处理单元不是代表某种抽象的流量类型,而是代表JPEG编码过程中各个任务,协作完成JPEG基本的编码功能。其中节点上的IP核分别代表一个任务进程。NIRGAM允许将IP核动态的与任何节点绑定。如果没有绑定任何IP核,那该节点只作为一个路由节点。处理单元设计实质上是继承基础IP核模块上的方法为自己创造新的IP核,甚至对基础IP核做修改。

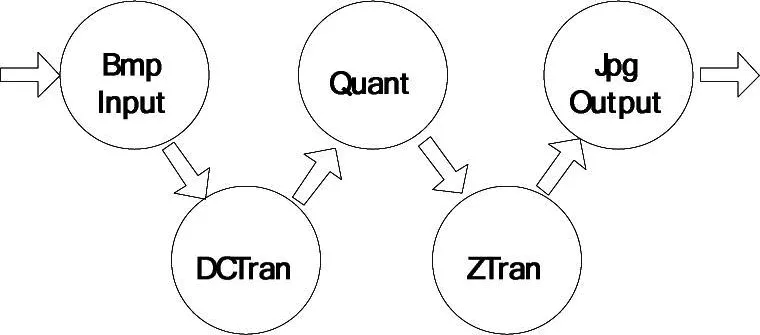

1)JPEG编码器任务进程IP核设计

据JPEG编码原理[8],参考进程网络模型[9]理论,编码过程被分解成5个独立的进程,依次是位图输入、FDCT(Forward Discrete Cosine Transform)、量化、Z字形变换和哈夫曼编码输出,如图3所示。根据这5个任务,在IP核模块中加入实现相应任务的函数,使得触发recv进程时调用函数处理数据包,处理完毕的同时触发send进程将新数据包送回网络中,传递给下游任务。

图3 JPEG编码器进程网络模型

2)JPEG编码器任务映射

本实验以3x3的2D MESH为NoC拓扑结构,采用分组交换机制、虫洞式流控机制和XY路由算法。以微片作为最小数据单元,每个数据包由64个微片组成。如图4所示JPEG编码器任务进程在NoC上映射拓扑结构图。其中黑色箭头表示按照XY路由算法的数据流轨迹。各IP核由NIRGAM通过文件application.config分别与节点0,1,2,6,8绑定。

3)实验与分析

图4 JPEG编码器任务映射图

本实验工作频率1 GHz,共运行200000个周期。仿真结束生成.m文件,由Matlab运行得到此次仿真中所统计各个通道的吞吐量,如图5所示。

图5 JPEG编码任务吞吐量

通过节点间的数据通信和上下游任务进程间的相互协作,最终由节点BmpInput输入的位图图像经过NoC的一系列处理流程,在节点JPGOutput成功生成了JPEG编码压缩后的图像。但由图可知这5个任务的负载是不均衡的,其中数据都是从BmpInput节点注入,所以该处的端口吞吐量非常大,且产生了较大的发送时延。其他模块边接收,边处理,边发送,及时将数据送出,缓解了输入和输出通道的拥塞。该实验采用XY确定性维序路由算法,是2D MESH下最高效最简单的确定性路由算法,但不会根据网络的拥塞状况均衡负载。参考图5的反馈的信息,我们可以对IP核在拓扑上的布局做优化,使得负载更均匀,避免网络局部拥塞,提高网络整体的资源利用率。

学生通过NIRGAM处理单元设计实验,可以理解软IP核的构造以及NoC节点的通信机制,并切身体会到NoC如何组织和协调各个节点的任务进程,最终实现一个具体的应用。同时NIRGAM以其结果直观灵活的优点,便于学生缩短对任务映射方案调试和修正的周期,提高实验效率。

3.2 NIRGAM路由器设计实验

越智能的路由节点,其硬件逻辑越复杂,功耗也越大。针对NIRGAM的路由算法扩展可以直接使用模拟器所提供的API(Application Program Interface)。复杂度更高更智能的路由算法,甚至需要对NIRGAM的核心引擎进行修改,如输入和输出通道等,这是因为路由机制的设计与网络整体的架构以及其他机制息息相关,如交换和流控机制。

1)XYYX路由算法设计

本文以文献[4]提出的基于Turn Model的XY增强型XYYX路由算法为例,进行路由算法的设计实验。为了更好地理解,我们把2D MESH NoC拓扑结构的四边依次标记为北、东、南和西。该算法对当前节点与目的地节点的相对位置分作两种情况考虑。当当前节点位于目的地节点的南方时,使用YX路由算法思想,那么总是从 Y维度开始路由;在当前节点位于目的地节点的北方时,使用XY路由算法思想,那么总是从X维度开始路由。因此当处在一个均匀概率随机目的通信的情况下,相对XY路由算法,X维度的负载被均分给了X与Y两个维度,达到了减轻X维度拥塞的目的。

图6 XYYX路由轨迹示意

如图6所示XYYX路由算法数据流轨迹图。该增强型XYYX算法的特点是改善了XY路由算法在X维度上的拥塞情况,算法思想巧妙但不复杂,可以直接利用API的calc_next函数进行设计。

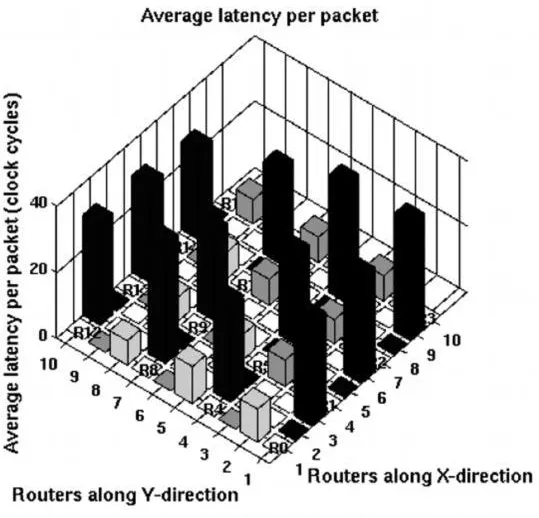

2)实验与分析

本实验以4x4的2D MESH为NoC拓扑结构(图6),采用分组交换机制、虫洞式流控机制和XYYX路由算法。以微片作为最小数据单元,每个数据包由3个微片组成,分别是头片、数据片和尾片。本实验工作频率为1 GHz,共运行1000个周期,其中从第5个周期开始生成流量,到第300个周期时停止生成流量。实验通过转置流量模式分别对XY和XYYX路由算法进行了时延的分析和比较,如图7和图8所示。转置流量模式是指X维度与Y维序互换的一对节点之间互为源节点和目的地节点,相互朝对方发送数据。

图7 XY路由算法网络平均时延

图8 XYYX路由算法网络平均时延

图7所示采用XY路由算法后,网络所统计到的在各个方向通道上的数据包时延。我们可以观察到在整个网络中时延很大的都是东西方向通道,这正是XY路由算法总是从东西方向开始路由所致。

图8所示改用XYYX路由算法后,网络所统计到的在各个方向通道上的数据时延。我们可观察到在时延很大的通道中,西向和北向各占50%,也就是说X与Y维度共同承担了以前仅由X维度承担的负载。可见XYYX路由算法起到了均衡X与Y维度负载的能力。我们根据图7和图8的反馈信息,可以直观看到XYYX路由算法的改进优势。

学生通过XYYX路由算法设计实验,可以从中理解,路由算法在网络流量中所起到的协调作用。由于NIRGAM模拟器反应迅速,便于学生在路由算法之间做对比实验。

4 结语

在多核课题中,NoC成为解决SoC互联问题的研究热点。本文以免费开源的NIRGAM模拟器为例,实现了基于NoC架构的JPEG编码器和XYYX路由算法。实验中分析的基于SystemC的NIRGAM仿真实验平台拥有灵活的扩展能力,满足了NoC教学实验研究的需要,也为开展NoC设计与创新提供了支持。实验平台皆采用软件方式模拟NoC的行为,能对配置和设计做出快速反应,有效地缩短了NoC设计和验证的周期,基于SystemC的NIRGAM仿真实验平台。

[1] Tobias Bjerregaard,Shankar Mahadevan.A survey of Research and Practices of Network-on-Chip[J].Lyngby:ACM Computing Surveys(CSU R),2006,38(1):1-51.

[2] Erno Salminen.On network-on-chip comparison[J].Tampere:Digital System Design Architectures,Methods and T ools,2007:503-510.

[3] Lavina Jain.NIRGAM.http://nirgam.ecs.soton.ac.uk

[4] 欧阳一鸣,董少周,梁华国.基于2D M esh的NoC路由算法设计与仿真[J].合肥:计算机工程,2009,35(22):227-235.

[5] William J Dally.Principles and practices of interconnection networks[M].California:M organ Kaufmann Publishers,2004:1-42.

[6] S.Kubisch.E-Core-A Configurable IP Core for Applicationspecific NoC Performance Evaluation[J].Anaheim:DAC Workshop on Diagnostic Services in Network-on-Chips,2007.

[7] 罗丹,吴宁.基于OCP接口的片上网络性能评估平台[J].南京:中国集成电路,2010,19(8):45-50.

[8] Chung-Jr Lian,Liang-Gee Chen,Hao-Chieh Chang,Yung-Chi Chang.Design and Implementation of JPEG Encoder IP Core[J].Yokohama:Design Automation Conference,2001:29-30.

[9] Yongjin Ahn.Process Network M odeling and TLM Generation for H.264 Codec Design[R].Irvine:Center for Embedded Computer Sy stems,2008.