高输出频率GPS接收机FPGA优化设计

2011-08-13李英飞丁继成

李英飞,丁继成,赵 琳

(哈尔滨工程大学 自动化学院,黑龙江 哈尔滨 150001)

当前,以FPGA+DSP为硬件平台实现的软件接收机,由于参数设置灵活、可验证新的导航算法而备受重视。伴随着新算法的日益复杂和对接收机要求的不断提高,对系统的速度提出了更高的要求[1-2]。比较GNSS接收机不同解决方案的处理能力与灵活性[3],将更多的任务交给FPGA处理以减少DSP的负担、提高系统速度。本文采用FPGA完成GPS的基带处理,保留了软件接收机参数的灵活性;节省了DSP资源,增加了定位结果的输出率;在FPGA硬件资源允许下,通道个数可以任意扩展。

1 基带处理FPGA实现方案

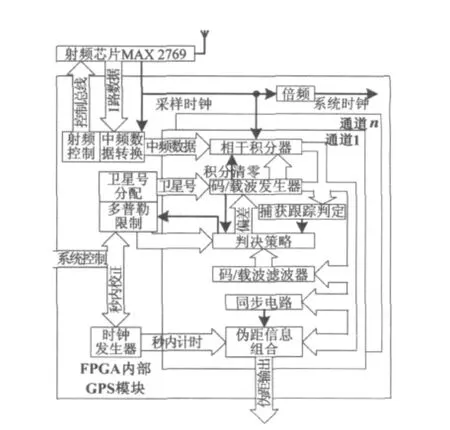

如图1所示,GPS信号经天线、射频下变频至中频,进入FPGA。载波环路和码环路对中频信号进行解扩,得到数据比特流。同步电路对数据流进行同步,输出伪距等相关信息。系统启动时,卫星号分配模块和多普勒限定模块接收DSP发送的配置方案。时钟发生器模块用于产生时钟脉冲。

1.1 数控振荡器设计

图1 FPGA基带处理模块总方框图

载波发生器按照输入值产生不同频率的同相I、正交Q两路正弦信号。码发生器除了产生不同频率的C/A码外,还具有对码相位进行移位的操作。为减少资源使用,只采用每次延迟一个码片的操作。延迟移位可减少捕获到多径信号的危险。

1.2 环路滤波器参数调整

考虑到FPGA除法运算的舍入误差和射频芯片带宽的影响,环路参数的调整工作按以下步骤进行。

(1)按滤波器典型值计算公式,计算环路的增益、载波环带宽100 Hz和码环的10 Hz的参数值。此外,为了FPGA能够利用移位进行运算,应化简计算结果。

(2)修改载波环环路增益,使环路稳定。

(3)修改载波环和码环增益,使环路波动最小。

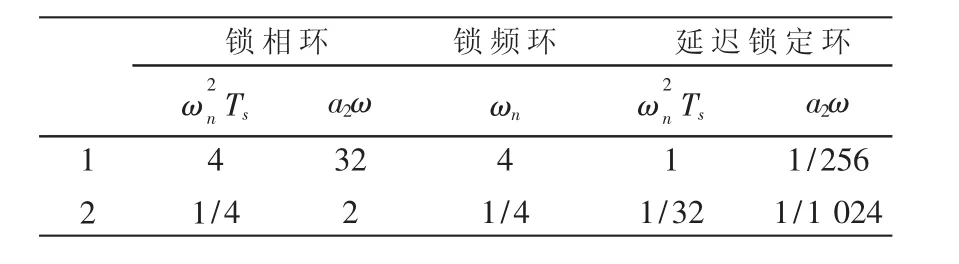

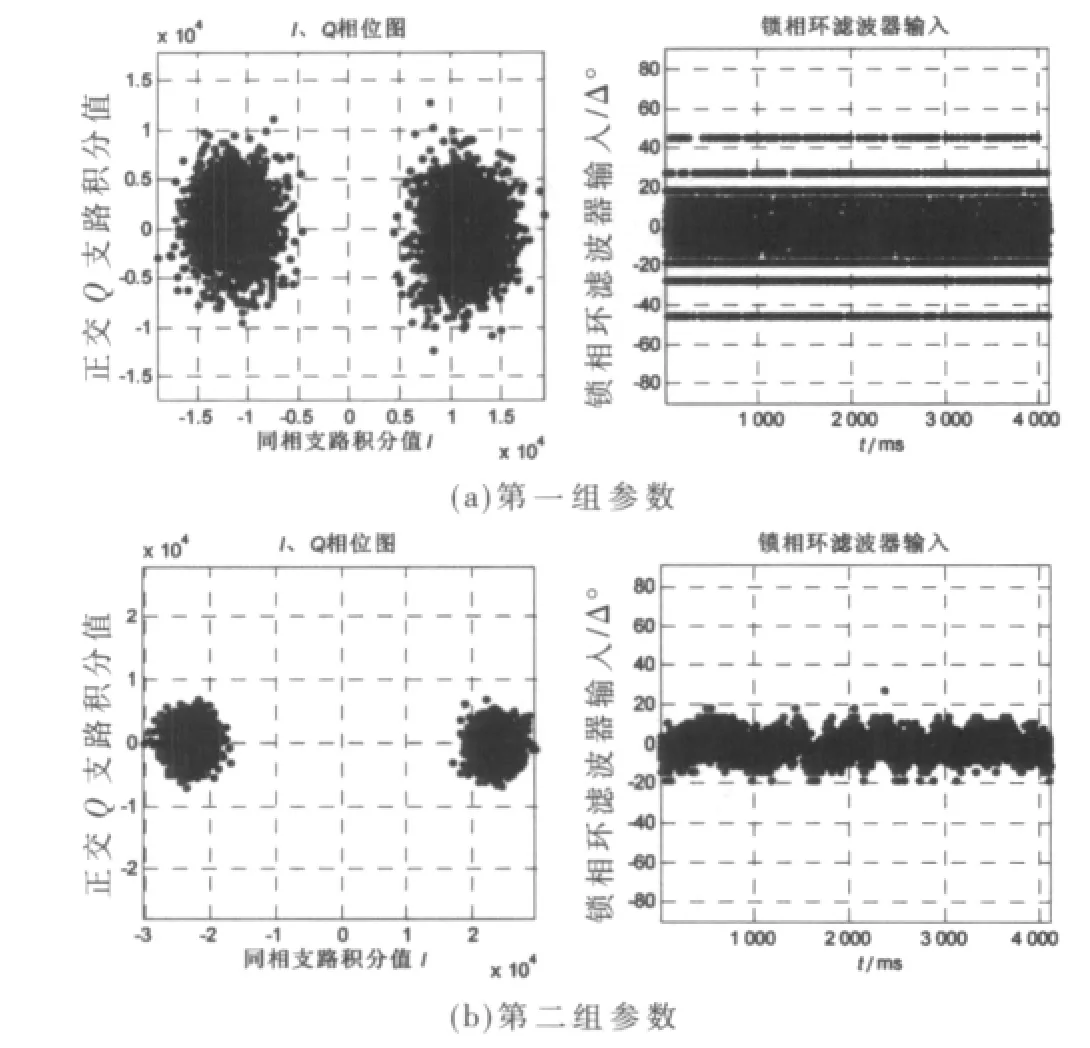

系统使用一阶锁频环辅助二阶锁相环滤波器。当滤波器使用表1的参数时,得到图2所示的系统时域性能。从图2可以看出,第一组锁相环鉴相器的输出抖动大,系统相位误差大。同时I、Q相位图中在正交支路Q上还有很大的能量,环路收敛性差。逐步调整参数比例后,在第二组中相位误差减小到20°以内。

表1 环路参数对比

图2 不同参数的环路状态

1.3 伪距信息输出

在位同步和帧同步完成后,FPGA能够检测到子帧头位置并通过数据流得到子帧头部的发送时刻(周内时)。为得到子帧头后任意一点的发送时刻,FPGA在检测到子帧头部时对各计时寄存器清零,然后按照各自的频率累加计时。当DSP请求提取伪距信息时,FPGA将该时刻的各计时寄存器值同时转移锁存,并传送给DSP处理。DSP计算出计时寄存器值对应的时间,再加上子帧头对应的周内时即可得到信号的发送时刻。

2 基带处理辅助模块优化设计

接收机的正常工作需要一些辅助模块,以协助接收机在信号遮挡、消失等条件下正常运行。

2.1 卫星号自动分配方法

在系统冷启动时,FPGA自动搜星。为避免自由通道同时搜索同一颗星,需要设计卫星号分配方法。自动分配方法采用申请交换方式。如果自由通道没有捕获到当前卫星,则向卫星号分配库申请新的卫星,同时将正在使用的卫星号上交。为适应热启动,DSP需要将优先搜索的卫星排在分配器前端以获得高的优先级。PRN码库可将刚刚处理过的卫星号自动变为低优先级,以保证系统及时处理新出现的卫星。

2.2 热启动载波多普勒限制

多普勒限制模块与卫星号分配库结构相同。DSP系统根据历书、时间和预存储的位置计算出可视卫星号、概略多普勒频移信息,把结果传送至FPGA,并通知FPGA使用何种搜索模式进行搜星捕获等。此处理方式可大大减少首次定位时间。

2.3 秒时钟脉冲输出

为输出与UTC同步的精准秒脉冲,在FPGA内部设计了时钟发生器。时钟发生器以系统时钟为基准,并输出时钟秒内计时累加器值tc,为DSP系统校正使用。当DSP请求伪距信息时,FPGA同时将tc锁定送出。DSP定时计算后,可得到秒内时误差为系统当前时间中不到1 s的部分),滤波后把校正值反馈给FPGA进行校正。

3 系统验证

系统使用表1中第二组参数时,环路的牵引过程如图3所示。从即时码支路输出可以看出,开始阶段环路积分值不断增大,最后正交支路积分值变小,同相支路解调出数据流。载波多普勒频移显示环路承受了250 Hz左右的偏差,达到了设计目标。

图3 环路牵引过程

图4(a)所示的位同步是图4(b)帧同步的局部放大,Data_in为解调出的数据流输入。可以看出,Count_bit将一个数据位分成了20份,Head_bit指示出数据位的头部且第0位置处在数据位的开头。由于环路积分,Data_in晚于真实数据位一个积分周期,真正的子帧头在Count_bit为18时的末端,即图4(a)中TOW_short值发生改变的时刻。从图4(b)可以看出,在Head_subframe指示子帧头部后,Data_in的后续输入即为子帧头的标识“10001011”。当遥测字和交接字均通过校验后,帧同步成功。Head_subframe的触发由前一子帧数据计算得到。

图4 同步及伪距相关信息生成

图4(c)中,在子帧头部TOW_short发生改变的时刻,计时寄存器中过子帧头的完整C/A码码片个数Num_CA、过码片周期的完整系统周期个数Num_81 MHz重新计数。由于Num_81 MHz晚于真实子帧头CA_reset的上升沿一个系统时钟周期,即从2开始计数,这样,就能够统一时间计算方法。

综上所述,基于FPGA的基带处理,向DSP系统提供伪距相关信息的最大频率和FPGA的系统时钟有关。本系统理论最大提供频率为81.84 MHz,但受DSP处理速度和数据传输速度影响,在DSP满负荷运行下,系统最快输出定位频率为100 Hz。

本文将基带处理功能全部转移至FPGA,设计实现了GPS信号捕获、跟踪、同步、伪距相关信息整理等模块。将DSP从繁重的基带处理部分脱离后,可专注于复杂的导航解算,大大提高了导航解算的速度,为复杂导航算法的实现和导航结果的高频率输出提供了宽裕的硬件资源。

本系统采用Altera公司Cyclone II系列的EP2C70-F672C6芯片,实现了12通道GPS模块和EMIF接口电路。逻辑单元共占用60%,因此本款芯片支持更多的GPS通道模块设计。

[1]胡锐,薛晓中,孙瑞胜,等.基于 FPGA+DSP的嵌入式GPS数字接收机系统设计[J].中国惯性技术学报,2009,17(2):188.

[2]ABOELMAGD N,KARAMAT B T,Mark D E,et al.Performance enhancement of MEMS-based INS/GPS integration for low-cost navigation applications[J].IEEE Transactions.on Vehicular Technology,2009,58(3):1077-1096.

[3]DOVIS F,SPELAT M,LEONE C,et al.On the tracking performance of a galileo/GPS receiver based on hybrid FPGA/DSP board[C].Proceeding.ION GNSS,2005:1611-1620.