GSM-R 直放站数字下变频的FPGA实现

2011-08-11汪媚

汪 媚

(福建广播电视大学,福建 福州 350003)

0 引言

GSM-R是专用移动通信的一种,专用于铁路的日常运营管理,主要提供无线列调、编组调车通信、区段养护维修作业通信、应急通信、隧道通信等语音通信功能,可为列车自动控制与检测信息提供数据传输通道,并可提供列车自动寻址和旅客服务。铁路无线列车调度通信系统的通信质量直接关系铁路的行车安全,我国大部分的铁路地处山区及多隧道地区,造成列车无线调度通信系统在这种传播环境中遇到许多弱电场区。为满足弱电场区信号的连续覆盖,现在已采用多种技术方式,如漏泄同轴电缆+中继器、光纤直放站、无线直放站等。由于目前光纤资源丰富,光纤直放站可靠性高等特点,铁路弱场覆盖解决方案中广泛采用光纤直放站[1]。

数字光纤直放站是利用软件无线电技术,将GSM Um口信号数字化,通过光纤传送到远端,利用远端射频单元再生、放大,实现基站信号拉远覆盖的无线网络覆盖设备。数字上/下变频(DUC/DDC)是数字光纤站的重要组成部分,其功能是将基带信号经过内插滤波后变到中频的频率,或者将中频的信号经过抽取滤波后降到基带的频率上[2]。文章主要介绍了一种GSM-R光纤直放站数字下变频模块的FPGA实现方法。

1 数字下变频的系统结构与设计

1.1 GSM-R直放站数字下变频器的参数设计

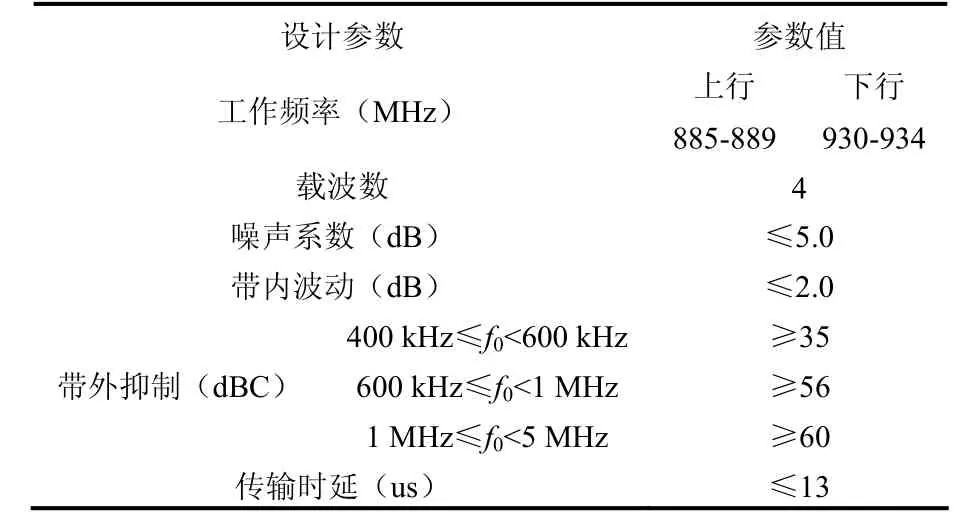

表1为GSM-R光纤直放站的基本参数,要求4载波GSM信号在4 m的带宽内任意可选择地通过光纤传输。本设计为数字中频信号处理模块,在滤波器特性上,要求至少符合模拟声表滤波器的一般指标性能:即通带带宽大于等于200 kHz,阻带带宽小于等于1 MHz,带外抑制不小于60 dBC,载波中心偏正负400 kHz的抑制不小于35 dBC,达到工程可用的目的。

由于存在模数转换过程,设计利用了奈奎斯特带通采样定理[3],使用现行的高速ADC直接对中频信号进行带通采样从而保证有用带宽内的信号不发生失真[4]。在实际的 AD转换过程中,由于幅频特性的非理想,在整个通带内越靠近带宽边缘处,信号受到的衰减越大,一般比频带中心处的幅度差值大约在0.5 dB以上。对于本下变频系统来说,所采样的信号最大带宽范围是 4 MHz,考虑到预留一定的冗余带宽,将采样率设为61.44 MSps,为滤波器实现良好的带内平坦度提供了保障。

表1 GSM-R 系统的基本参数

下变频之后带宽和数据速率之间有着相互制约的关系,一定的数据速率fs,由于iq正交关系的2路信号表示的是复频域信号,则最大可表示的信号带宽为fs。这样,若明确了所感兴趣的载频带宽之后,经抽取的基带信号速率则不可能小于载频带宽。另一方面,基带信号在上变频时需要经过插值处理,还原为下变频之前的数据速率,在插值过程中由于镜像滤波的需要,使处理的时延变大,因此基带速率大小的选择需要进行时延和基带表示信息量之间的权衡。综合考虑带宽与时延等指标,系统基带的数据数率选为7.68 mb/s。

1.2 GSM-R直放站数字下变频器的系统结构

系统光纤传输接口采用的是 cpri协议,由于需要预留外部透传数据的 cpri容量,因此系统要求使用宽带传输,即传输的是一通道4 m宽带信号,考虑到系统要求4载波信号任意可选,本DDC模块采用2次混频过程。第一次混频是下变频,将4通道载频信号分别往下搬移到零频;第二次混频为上变频,再将4通道零频信号上搬移至基带相应频点,并合路为带宽4 m的一通道基带信号。这样后级的数字上变频模块(DUC)只需将该 4 m信号上搬移至指定频点即可,降低了后级资源的要求。

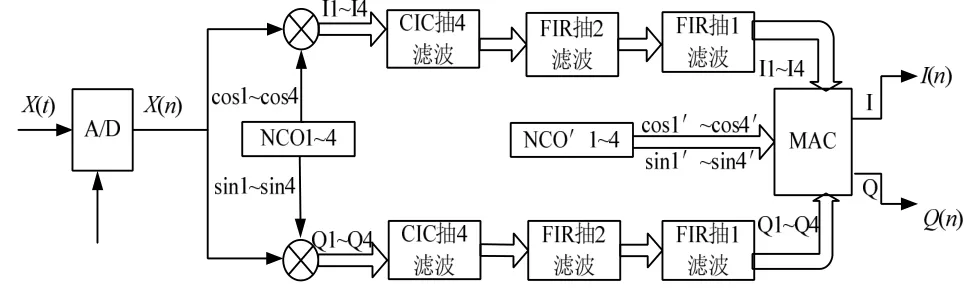

数字下变频器DDC的功能结构如图1所示,模拟中频信号X(t)经AD芯片数模转换后得到数字中频信号X(n),DDC模块将输入的X(n)信号分为4个通道,为每个通道配置独立工作的 NCO(数控振荡器)、数字混频器、数字滤波器等子模块。其中,NCO用于选择输入载波信号的工作频率,只有符合频率的载波信号才能进入该DDC通道;数字混频器即为乘法器,将X(n)与第一级NCO产生的本振信号相乘;数字滤波器包括CIC抽4滤波器,FIR抽2滤波器,FIR单倍滤波器,将信号抽取后频域上的混叠信号滤除并实现对信号的整形以满足带外抑制要求。最后将4通道信号与第二级NCO′产生的本振进行乘累加(MAC)合路后得到I、Q 2路基带数字信号,该信号以7.68 mb/s的数据数率送给光纤传输模块。

图1 GSM-R 数字下变频结构

2 数字下变频的FPGA实现

2.1 数控振荡器NCO的FPGA实现及仿真

数控振荡器 NCO的目标是产生一个理想正交本振序列cos(w0n)和sin(w0n),这里采用直接数字频率合成器DDS实现。直接数字频率合成器DDS由相位累加器、相位加法器、正弦查找表组成[5]。每到一个时钟脉冲,通过相位累加器使相位在原来的基础上加一个相位累加量即频率控制字 M,再利用相位加法器加上初始相位,最后用相位值作为正弦查找表的地址,查出正弦值。每当累加器溢出时就产生一个新的循环,累加器完成一个循环的时间就是正弦波形的周期。

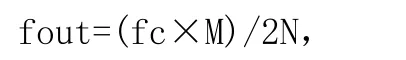

设fout为DDS的输出频率,fc为输入信号的采样频率,N为相位累加器的字长,则输出信号频率与频率控制字M的关系为:

当M为1时,上式代表DDS的输出频率分辨率,即:

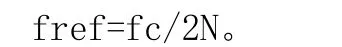

直接数字频率合成器DDS可以采用XILINX公司提供的IP核DDS Comlpier实现。将DDS的时钟频率设为61.44 MHz,与DDC的输入采样率相同,将相位宽度N设为20位,频率控制字M设为20’h40000,则DDS输出频率为15.36 MHz的两路正余弦信号,并与原始信号混频后产生两路零中频正交信号,实现下变频。其中DDS的参数设置为:SFDR为84 dB;频率分辨率58.6 Hz。通过调用Modelsim,DDS的综合仿真结果如图2所示。

图2 DDS 的Modelsim仿真

2.2 多级滤波模块的设计

多级滤波器模块对混频后的信号进行滤波、抽取,降低数据速率并且达到滤波选频的效果。抽取滤波器级数没有统一的标准,由于多级抽取[6]可减少硬件中资源的使用而达到同样目的,因此本设计采用3级的抽取过程,通过CIC滤波4倍抽取,FIR滤波2倍抽取,FIR滤波单倍抽取将61.44 mbps的基带数据数率降低到7.68 mbps以进行内部混频。

CIC滤波器由于其实现结构特点常用来在数字系统中实现大采样率的改变[7],但较大的旁瓣使得其难以达到良好的滤波性能,可以通过阶数的增加来提高阻带的衰减性能[8],因此本设计第一级抽取滤波器采用4阶CIC滤波器来实现对信号的4倍抽取。

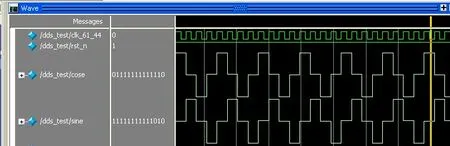

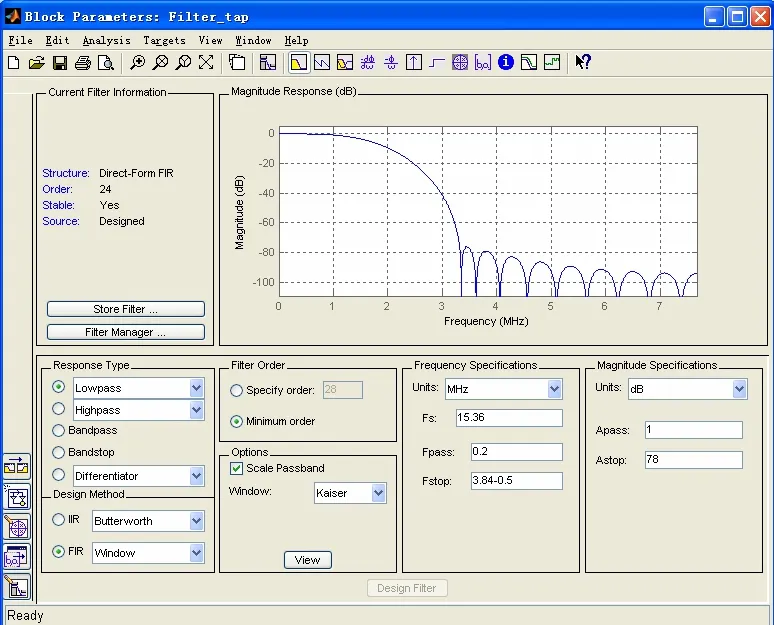

假定通带等纹波大小,FIR滤波器理论上的设置主要考虑通带和阻带位置。为在工程上可用,根据gsm载波特性,对单载波信号本系统3 dB的通带带宽设为0.4 MHz,阻带带宽设为1 MHz。系统中的滤波器参数可以在matlab的滤波器设计工具fdatool中得到体现,多级滤波器的设置如图3和图4所示。

图3 FIR抽2滤波器的响应曲线

图4 FIR抽1滤波器的响应曲线

2.3 内部混频模块的实现

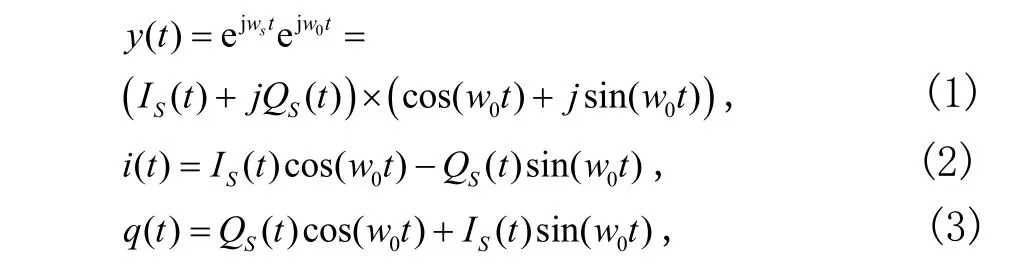

在DUC内部的混频处理上,采用正交混频的方案,7.68 m的IQ基带数据与相同数据速率的本振信号进行正交混频,使频谱上搬。正交混频的计算公式如下:

公式(1)为正交混频公式,公式(2)、(3)为其实部和虚部的分解式。其中w0为本振信号的角频率,ws为待处理信号的角频率。

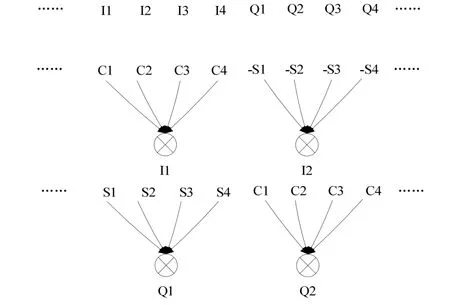

从上式中可看出此复数运算要进行 4次乘法和 2次加法,由于系统时钟为数据速率的8倍,通过利用FPGA内部DSP48的时分复用可实现多个通道数据的乘累加运算,即在混频过程中直接将不同通道的数据进行合路,进而省去一级加法器。为此,需要要求IQ和DDS数据按照一定的顺序对应输出,4载波8个iq通道的处理只需2个DSP48即可完成,如图5所示。

图5 DUC混频DDS输出和数据对应关系

3 硬件测试与结果分析

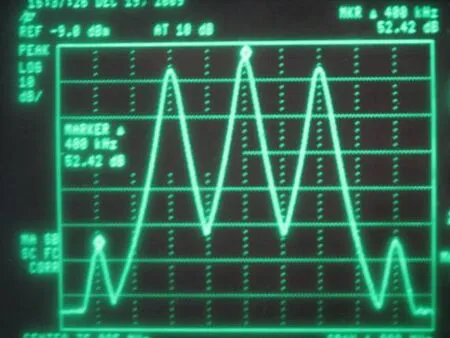

数字下变频器 DDC最终在 XILINX公司的 FPGA芯片Virtex-4 XC4VSX35上实现。采用信号发生器Agilent E4433B产生模拟中频信号76.8 MHz作为采样率为61.44 MHz的ADC(型号为 AD11C125)的输入信号。ADC芯片过采样后输出15.36 MHz的中频信号输入数字下变频模块进行下变频处理。最后I、Q两路正交信号输出到DA芯片AD9779A。

其中DA芯片输出的模拟信号频谱如图6所示。在测试过程中,通过调节信号发生器的频率可以将信号变频到不同的中频频率上,验证了下变频器设计的正确性。由图6可知,在载频中心偏±200 kHz时该处带外抑制为2.98 dB左右,符合不大于3 dB抑制的指标要求;在载频中心偏±400 kHz时带外抑制为52 dB左右,大于35 dB抑制的指标要求,验证通过。

图6 AD9779模拟输出信号频谱

4 结语

详细介绍了GSM-R直放站数字中频模块下变频器的设计与实现。依据GSM-R系统的指标要求,利用FPGA的高速率、可实现在线重构等优点,采用SIMULINK建模与Verilog语言相结合的方法实现了数字下变频的设计,仿真与测试结果达到了设计要求。综上所述,所提出数字下变频方案具有实际的应用性及独特性,在工程实践中有一定的参考价值。

[1]李玲姣.光纤直放站在 GSM-R系统中的应用[J].铁路通信信号工程技术,2010(08):33-35.

[2]秦明伟,李德建,姚远程.软件无线电数字下变频及抽取技术研究[J].通信技术,2008,41(09):84-85.

[3]汪敏,肖斌.基于 FPGA的数字中频系统设计[J].通信技术,2011,44(01):29-31.

[4]池琛,张彧,杨知行.软件无线电中的多频段信号带通采样[J].清华大学学报:自然科学版,2009,49(08):1176-1179.

[5]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[6]杨旭峰.多级数字抽取滤波器设计与MATLAB仿真研究[J].南宁职业技术学院学报,2009,14(05):94-97.

[7]冯振伟,武小冬,梅顺良.基于FPGA的数字中频接收机设计与实现[J].通信技术,2010,43(04):17-19.

[8]谢白玉,杨士中,张承畅.基于FPGA的CIC滤波器的设计[J].计算机仿真,2009,26(08):323-325.