基于灰度投影法的电子稳像平台设计与实现

2011-08-10杨光宇佟新鑫王玉良栗霄峰

杨光宇,朱 丹,佟新鑫,王玉良,栗霄峰

(1.中国科学院沈阳自动化研究所,辽宁 沈阳 110016;2.中国科学院光电信息处理重点实验室,辽宁 沈阳 110016;3.辽宁省图像理解与视觉计算重点实验室,辽宁 沈阳 110016)

责任编辑:孙 卓

0 引言

电子稳像技术是综合电子、计算机、数字信号处理等技术,利用数字图像处理方法直接确定图像序列的偏移并进行补偿的技术[1]。利用电子稳像技术对不稳定的视频序列进行稳定处理,可提高监视质量,便于后续应用处理。电子稳像技术广泛用于机器导航、目标识别与跟踪、安全监控等视频分析和处理领域。实际应用中对电子稳像系统的处理时间、体积、重量、功耗等要求不断提高,基于嵌入式的实时电子稳像系统具有更高的实际应用价值。

鉴于电子稳像技术在军事和民用领域中的重要作用,美国、加拿大、以色列等国家较早地进行了研究和开发,并取得了一定成果。我国在2000年之后开始进行稳像技术研究。中国科学院长春光机所钟平针对具体应用环境特点,采用基于特征跟踪的电子稳像方法用于机载电子稳像,取得了良好的结果[2]。哈尔滨工业大学张博等将基于帧矢量叠加和自适应中止技术的快速运动估计方法用于电子稳像,运算量显著减小[3]。国防科大罗诗途等采用了一种由粗到精、由局部到全局配准的高效匹配策略实现了车载图像匹配,满足了车载图像跟踪系统对电子稳像技术的实时性及精度要求[4]。这些电子稳像系统大多基于VC编程在PC机上实现。北京理工大学赵跃进采用XC95144XL CPLD+DSP6711为处理平台实现了256×256像素图像的实时稳定[5]。中国科学院长春光机所孙辉采用灰度投影法检测序列图像当前帧和参考帧之间的运动矢量实现亚像元检测,并基于DSP6416图像处理平台应用在船载电视监视系统中,但没有讲述硬件实现过程[6]。本文重点研究了基于EP2S30 FPGA+DSP6416架构的电子稳像平台硬件开发流程。采用灰度投影算法,本平台能实时完成25 f/s的标准PAL制视频的稳定。

1 灰度投影算法简介

电子稳像的原理是对不稳定的视频序列图像进行局部运动估计和全局运动估计,并对运动参数进行综合评价得到运动补偿参数,进而对图像进行运动校正得到稳定的输出图像序列。依据上述原理,电子稳像过程分为运动估计、运动滤波、运动补偿3个部分,而关键技术就在于估计视频序列图像相邻两帧之间的全局运动参数。

灰度投影算法的原理是基于行列灰度曲线的变化规律进行运动估计,其方法是将灰度图像的二维图像信息映射成2个独立的一维波形,即获取图像的行列灰度投影曲线,然后进行相关运算,找到相关值曲线中的单峰值即为当前图像相对于参考图像的位移值。灰度投影算法作为一种二维平移模型的算法具有独到的优势,例如计算速度快,易于VLSI实现等。

2 电子稳像平台设计

2.1 平台硬件设计方案

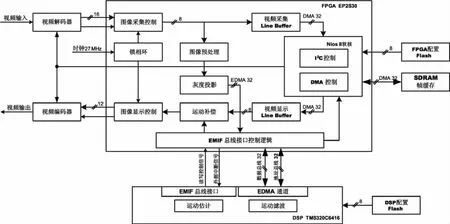

电子稳像平台硬件结构框图如图1所示。平台完成灰度投影法电子稳像的流程为:视频解码器接收模拟视频并将其转换为数字视频数据流送入FPGA内部的图像采集控制模块。图像采集控制模块进行图像处理区域的剪裁和图像数据的YCbCr分解,分解之后的灰度数据分成两路,一路通过视频采集FIFO存入SDRAM进行帧存储;另一路先进行图像预处理,然后进行行列方向的灰度投影数据累加。DSP通过EMIF总线读取这个累加结果,完成运动估计和运动滤波的计算得到运动矢量数据。Nios II处理器通过EMIF总线读取这个运动矢量,在下一帧图像扫描开始时将SDRAM帧存储中的图像数据读入到视频显示FIFO中,经运动补偿模块后得到稳定的数字视频数据流,最后通过图像显示控制模块送到视频编码器输出稳定的模拟视频。

图1 电子稳像平台硬件架构图

2.2 平台软件设计方案

电子稳像平台的软件设计分为两部分,分别在DSP6416和Nios II处理器中完成,其中DSP6416完成稳像算法的运动估计、运动滤波功能,Nios II处理器完成图像帧存储设计、视频编码器、视频解码器配置等功能。软件框架分为3个层次:

1)顶层管理。利用C6416芯片支持库以及DSP/BIOS完成系统配置及实时多任务调度[6];

2)设备驱动。利用Nios II处理器的HAL完成编码器、解码器及SDRAM等外设的配置[7];

3)算法应用。利用C6000的FastRTS函数库完成稳像算法中的浮点运算部分。

2.3 平台整体时序设计

图2是通过FPGA内部的逻辑分析仪采集到的稳像平台硬件设计时序图。

图2 硬件设计时序图(截图)

系统上电后FPGA通过内部Nios II处理器完成视频编码器、视频解码器的配置,之后通知DSP配置过程结束,DSP接收到配置结束信号后产生稳像开始信号(图2中信号4)送给FPGA。对于FPGA,接收到这个信号的时间是随机的,而本文的稳像算法是基于帧处理的,所以FPGA必须从稳像开始信号有效之后最新到来的一帧图像开始进行稳像处理。稳像平台的整体时序设计如下:

1)帧起始信号(图2中信号5)代表着稳像开始信号有效后每一帧新图像的到来,本文用这个信号触发Nios II处理器的外部中断来读取DSP计算出来的全局运动矢量。

2)处理区域奇场、偶场行有效信号(图2中信号6和信号7),这2个信号的下降沿分别代表稳像开始后每帧图像中奇场及偶场处理区域的结束,通知DSP通过EDMA通道读取图像灰度投影累加数据。为了完成实时稳像,DSP必须在信号7的下降沿和信号6的上升沿之间完成全局运动矢量的解算。

2.4 图像帧存储时序设计

电子稳像算法中,根据全局运动估计算法复杂程度的不同,需要存储图像的帧数就不同,图像延时的时间也就不同。基于灰度投影法的电子稳像平台需要进行一帧的图像存储,稳定之后的图像有一帧的延时。

在FPGA中利用SOPC_Builder生成SDRAM控制器通过DMA方式将图像存储在外部SDRAM中。同时在FPGA中还分别设计了采集FIFO和显示FIFO对图像采集和显示作行缓存。需要注意的是对于显示FIFO,本文必须提前写入一行数据以防止图像处理区域扫描信号到来时显示FIFO的读空。

图3是逻辑分析仪采集的帧存储时序波形,为了便于显示省略了中间的部分。分析如下:

图3 图像帧存储时序设计图(截图)

1)利用处理区域列有效信号(图3中信号3)作为采集FIFO的写使能信号,信号的下降沿代表着一行有效数据采集完毕同时中断通知Nios II处理器通过DMA方式将数据写入SDRAM的采集存储区。采集FIFO的读使能、数据入、数据出分别对应于上图中的信号4,5,6。

2)利用提前一行的列有效信号(图3中信号8)上升沿去触发Nios II处理器的外部中断,通过DMA方式从SDRAM显示存储区中读出一行有效数据写入显示FIFO,而显示FIFO的读使能信号仍然使用信号3,这样便能防止显示FIFO的读空,同时保证显示FIFO中处理区域最后一行的有效数据被读出。显示FIFO的写使能、数据入、数据出分别对应于上图中的信号9,10,11。

由图3可见,上述设计中SDRAM读写操作时序不会出现重叠,完全满足时序要求。进行运动补偿时,上述设计的采集FIFO时序不发生变化,而显示FIFO的输出数据及相应的使能信号会发生变化。具体设计见图像运动补偿时序设计部分。

2.5 灰度投影数据累加时序设计

灰度投影数据累加包括行方向和列方向的数据累加,累加结果存储在FPGA片上的双端口RAM中。由于视频数据流的输入是随着行方向的扫描而来的,因此行方向上只要随着像素时钟对行方向投影数据作累加就可以了。

列方向投影数据累加采用2个双端口RAM,第1个双端口RAM存储图像处理区域内除最后1行图像外的列向投影数据累加结果,当图像扫描到处理区域最后一行时,从第1个双端口RAM读出之前的累加数据、加上图像最后1行当前列的数据、写入到第2个双端口RAM对应于列地址的存储单元中,同时将第1个双端口RAM对应列地址的存储单元清零。为了在1个像素时钟内完成数据读出、累加、写回的操作,本文用像素时钟的4倍频时钟驱动一个具有4个状态的状态机来完成上述的操作。图4为双端口RAM完成列方向投影数据累加过程示意图。

图4 列方向灰度投影数据累加(截图)

2.6 图像运动补偿设计

图像运动补偿模块的功能就是根据全局运动矢量计算出经过运动补偿之后的图像在SDRAM帧存中的位置并将图像取出来作显示。对于运动补偿之后产生的空白区域,本文作补零处理。

图像运动补偿功能由FPGA逻辑和Nios II处理器共同完成。Nios II处理器接收来自DSP的水平向和垂直向的全局运动矢量d x,d y,计算出运动补偿图像区域的首地址作为DMA的起始源地址。由于本文定义的DMA总线位宽为32位,为了地址对齐,定义每次DMA的数据长度为图像处理区域的长度img_h,为4的整数倍。这样对于每帧图像的运动补偿,实际上启动了(img_v-d y)次DMA传输,而每次DMA传输的数据中包含了d x个无效数据,其中img_h和img_v分别为图像处理区域的长度和宽度。

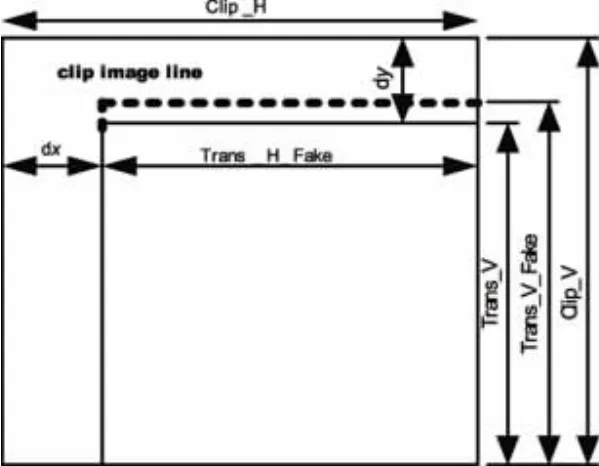

在FPGA的逻辑设计中,本文产生运动补偿所需的各使能信号控制显示FIFO接收DMA数据,在图像显示控制模块中去除每行的d x个无效数据,并最终将运动补偿图像区域的图像作显示。各使能信号的定义如图5所示。

图5 运动补偿使能信号

在图5中,Clip_H为处理区域列有效信号;Clip_V为处理区域行有效信号;Trans_H为图像补偿区域列有效信号;Trans_V为图像补偿区域行有效信号;Trans_H_Fake为提前一行的图像补偿区域列有效信号;Trans_V_Fake为提前一行的图像补偿区域行有效信号。图5在空间位置上定义的图像补偿区域与2.4节中从时序上定义的图像处理区域是一致的,只不过2.4节中是在图像不发生抖动时将全部图像处理区域作显示,而在图像发生抖动时,本文只将运动补偿之后的有效图像区域作显示,无效部分作补零处理。

3 实验结果

为验证稳像平台的稳像效果,本文做了如下实验。通过人为随机设定的水平和垂直偏移量,截取摄像机输出100帧序列图像的512×512区域大小来模拟抖动的视频序列,图像所加偏移量的大小在[-30,+30]个像素之间。在DSP6416程序中记录算法解算出的抖动图像序列的帧间运动矢量。将当前帧前面的所有帧间运动矢量作累加即可得到当前帧图像相对于基准帧图像的运动轨迹。将实际运动轨迹和滤波后的运动轨迹数据通过Matlab软件绘图如图6所示。

图6 x,y方向运动轨迹

由图6可见稳像算法能正确计算帧间运动矢量,并通过运动滤波去除视频中的无意抖动将摄像机的有意运动提取出来。同时将抖动的图像视频和稳像之后的视频分别在监视器上输出,稳像之后的视频达到了稳定效果。

4 设计总结

本文详细介绍了基于EP2S30 FPGA+DSP6416架构的电子稳像平台的硬件开发流程。采用灰度投影算法,平台能实时对水平向和垂直向抖动的范围为[-30,+30]个像素之间的标准PAL制视频进行稳定,稳像精度为1个像素。表1显示了FPGA中硬件资源的使用情况。

表1 FPGA硬件资源使用结果

本文没有对稳像算法本身作深入地研究,而将重点放在了稳像平台的硬件架构设计和时序设计上。由表1可见FPGA内部硬件资源的裕量很大,同时在FPGA的外部也扩展了足够的存储器,加之DSP6416的使用,本稳像平台完全有能力完成更复杂的算法。

[1]赵红颖,金宏,熊经武.电子稳像技术概述[J].光学精密工程,2001,9(4):353-359.

[2]钟平,于前洋,金光.基于特征点匹配技术的运动估计及补偿方法[J].光电子.激光,2004,15(1):73-77.

[3]张博,吴芝路,张欣宇,等.基于矢量叠加和自适应中止的快速运动估计[J].电视技术,2006,30(4):7-10.

[4]罗诗途,王艳玲,张圮,等.车载图像跟踪系统中电子稳像算法的研究[J].光学精密工程,2005,13(1):95-103.

[5]周渝斌,赵跃进,刘明,等.基于C6711 DSP的实时数字稳像系统[J].北京理工大学学报,2004,24(5):435-438.

[6]孙辉,熊经武,赵红颖.电子稳像技术在船载电视监视系统中的应用[J].光电工程,2008,35(2):103-108.