SHH应力下超薄栅氧PMOS器件退化研究

2011-08-04胡仕刚吴笑峰席在芳

胡仕刚,吴笑峰,席在芳

(湖南科技大学 信息与电气工程学院,湖南 湘潭,411201)

随着MOS器件尺寸减小,氧化层厚度越来越薄。栅氧化层退化和击穿已经成为制约超大规模集成电路(VLSI)迅速发展的重要因素[1-6]。当器件进入到90 nm工艺节点时,栅氧化层的厚度减小到2 nm以下,由于受软击穿和噪声的影响,用 TDDB(Time-dependent dielectric breakdown)来评估栅氧化层的质量将不能用来准确地衡量栅氧化层的寿命。而SILC(Stress induced leakage current)已经成为评估氧化层退化和击穿的有效方法[7-9]。SILC指 MOS器件中由于高场应力中的栅电流,这种栅电流随着氧化层厚度的减小而增加。SILC的基本物理机制是陷阱辅助隧穿。由于超薄氧化层中很难直接测量中性电子陷阱,SILC可以作为一种间接工具来监测中性电子陷阱产生。对于PMOS器件,不仅横向电场会引起热空穴产生,纵向电场也会导致热空穴出现。如果在PMOS器件衬底端施加一定的正电压,就会在器件中产生衬底热空穴(SHH)效应[10-12]。迄今为止,人们对由衬底热空穴引起的PMOS器件退化的研究(尤其是在超薄栅氧器件情况下)很少。在此,本文作者通过衬底热空穴注入技术,对厚度为1.4 nm的超薄栅氧PMOSFET衬底热空穴应力过程中器件退化进行研究,重点对应力下 SILC退化和氧化层击穿特性进行研究。

1 器件和实验

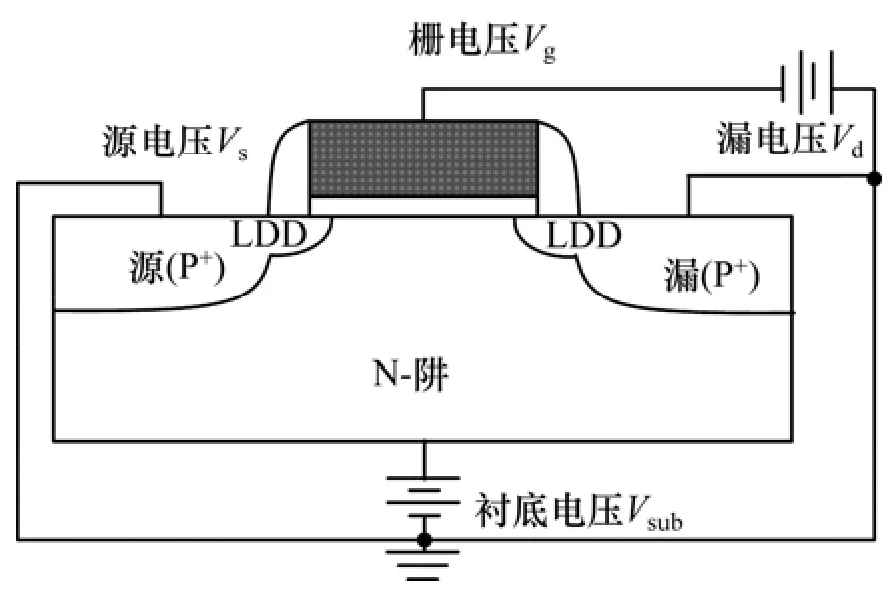

采用的器件为90 nm标准工艺制造的表面沟道器件,多晶硅栅采用P+注入,器件采用LDD轻掺杂漏与STI浅沟隔离结构。器件宽长比(W/L)为 10 μm/4 μm,栅氧采用DPN工艺,其氧化层厚度为1.4 nm。依然采用应力间断方法提取器件参数,测试过程由高精度半导体参数分析仪来完成,所有的应力测试都在暗箱中完成。在室温下,对器件施加 SHH应力,示意图如图1所示。

图1 PMOS器件SHH应力偏置条件示意图Fig.1 Schematic diagram of SHH stress bias condition in PMOSFET

衬底热载流子来源于热产生的衬底电流及在衬底耗尽层中产生的倍增电流。衬底偏压在沟道耗尽层上的压降所形成的高电场,是载流子获得足够能量而发射进入栅氧的首要条件。这些载流子被沟道耗尽层中的高电场加速,获得足够的能量而成为热载流子,它们向氧化层中均匀注入。在衬底热载流子应力条件下栅氧被击穿,对应的氧化层电场却较低,其击穿过程与恒定栅压应力过程不同。

2 结果和讨论

2.1 SHH注入退化现象

图2所示为PMOS器件在SHH应力下器件参数随应力时间退化曲线。其中阈值电压(Vth)是通过在线性漏电流(Idlin)中采用最大跨导法得到的。线性漏电流的测试条件为漏端电压Vd=-0.05 V,栅电压Vg从0~-1 V扫描。饱和漏电流(Idsat)的测试条件为:Vd= -1 V,Vg从0~-1 V扫描。从图2可见:Vth的退化量大于Idsat的退化量,Idlin退化量最小。漏电流的退化意味着器件驱动能力降低和可能的延迟时间增加,这将严重影响到MOS电路的正常工作。Vth的漂移量为负且绝对值变大,这是由于在SHH注入过程中器件氧化层俘获了带正电的电荷,使得Vth绝对值变大,Vth负向漂移导致器件驱动电流降低。此外,这些正电荷还会增加载流子的散射效应,导致载流子有效速率下降,从而进一步使器件驱动能力降低。从图2可以看出:双对数坐标下Vth,Idsat和Idlin的退化都与时间呈现很好的线性关系。

图2 SHH应力下PMOSFET器件参数退化与应力时间的关系Fig.2 Time dependence of degradation of device parameters in PMOSFET under SHH stress

图3所示为固定栅压不同衬底偏置的SHH应力下Vth的退化比较结果,其中,箭头表示被击穿。从图3可以看出:衬底偏置越大,器件参数退化越大,击穿所需时间越短。

图3 固定栅压不同衬底偏置下SHH应力下Vth退化比较Fig.3 Comparison of Vth degradation under SHH stresses at fixed gate voltage and different substrate bias voltage

图4所示为SHH注入过程中SILC随时间退化关系曲线。定义ΔIg/Ig0×100%为SILC(其中,Ig0为初始时刻的栅电流,ΔIg为Ig的变化量)。从图4可以看出:开始时栅电流随着应力时间增加不断减小,随后慢慢增加,然后发生1个突变,氧化层被击穿。电流在开始阶段减小是正电荷在氧化层中积累的结果。这一结果在阈值电压的漂移实验中得到验证。随后,漏电流慢慢地增加;最后,当在氧化层中积累的正电荷密度达到1个临界值时,栅上漏电流迅速跳变到较大数量级上,说明器件被击穿。

2.2 SHH注入退化机理

施加衬底偏置电压后,器件阈值电压将由未加衬底偏置时的

图4 SHH注入的过程中SILC随时间退化关系Fig.4 Time dependence of SILC degradation during SHH stress

变化到

式中:tox为氧化层厚度;εSi和εox分别为Si和SiO2的介电常数;εo为真空介电常数;Qeff为氧化层等效电荷;NA为受主杂质浓度;Фms为金属与半导体功函差;φF为费米势;q为电荷电量;Vb为衬底电压。

若考虑到衬底电压的影响,则器件阈值电压绝对值变大,在相同的栅压应力下,反型层空穴应该减少。然而,尽管在衬底偏置应力下器件反型层空穴减少,器件退化却随着衬底偏压的增加而增大,如图3所示。因此,可以认为:衬底偏压应力引起的器件退化加剧作用要超过反型层空穴减少所引起的退化减小作用。

图 5所示为在固定栅压应力下,衬底电压应力Vb=0 V和Vb>0 V这2种情况下的PMOSFET能带。从图5可见:当Vb=0 V时(如图5(a)所示),衬底表面反型层中有空穴存在。其中一部分是空穴进入栅氧,使Si—H键断裂,从而产生Si的悬挂键Si·即界面陷阱,这种普通空穴的作用被称为冷空穴效应;当Vb>0 V时(如图5(b)所示),耗尽层宽度明显增加,空穴在空间电荷区强电场作用下,从衬底到表面沟道的运动过程中不断获得能量,形成热空穴。此时,器件中存在2种空穴,即普通的冷空穴和具有更高能量的热空穴。热空穴隧穿进入栅氧并使Si—H键断裂的效率比冷空穴的更高,且随着衬底偏压的增大,一些空穴还有可能获得更高的能量可以使Si—O键断裂[13],产生氧化层缺陷,进而可以更多地俘获H+或者隧穿进入栅氧的空穴,从而使器件退化概率大大增加,这种热空穴作用被称为热空穴效应。当衬底偏压较高时,热空穴效应十分严重。

图5 固定栅压应力下,PMOSFET在Vb=0 V和Vb>0 V条件下的能带Fig.5 Energy band diagrams of PMOSFET under constant gate voltage stress when Vb=0 V and Vb>0 V

SiO2的结构可认为是4个氧原子位于三角形多面体的脚上,多面体中心是1个硅原子。这样,每4个氧原子近似共价键合到硅原子。同时,每个氧原子是2个多面体的一部分,氧的化合价也被满足。由SiO2的结构可以看到:每个Si—O四面体中心的硅都与4个顶角上的氧形成共价键,而每个顶角上的氧最多与2个硅形成Si—O键(桥键氧)。因此,硅要运动就必须“打破”4个Si—O键,但对氧来说,只需“打破”2个Si—O键,对于非键氧来说只需“打破”1个Si—O键。在SiO2网络中,氧的移动比硅的移动更容易,硅在 SiO2中的扩散系数比氧的扩散系数小几个数量级[14]。正因为这样,在SiO2网络中,氧空位可能形成,但考虑到键能的关系,非桥键氧空位更容易形成。因为SiO2中的氧离子是带负电的,故氧空位就带正电荷[14],同时,氧空位被认为是缺陷中心并导致陷阱产生和SiO2被击穿。氧空位的形成使得氧化层缺陷数目增加,在热空穴注入应力过程中,很多空穴自身会陷入缺陷中而成为陷阱正电荷。在热空穴注入过程中,注入的空穴在衬底电压下加速进入到氧化层中,注入到氧化层的空穴因为具备了相当大的动能,当它与氧化层晶格发生碰撞以后使得氧化层中的Si—O键断裂,介质特性退化。断裂的Si—O键在整个SiO2网络中分布,对器件性能退化造成影响。图6所示为由空穴引起的介质击穿示意图。从图6可以看出:在氧化层中的化学键断裂概率与注入的空穴流有很大关系,随着空穴流的增加,断裂概率也明显增大。从图6(b)可见:在氧化层晶格中1个Si原子上的2个Si—O键同时断裂就会引起晶格永久被破坏,这种破坏的不断积累就会使氧化层介质击穿。

图6 空穴引起的介质击穿示意图Fig.6 Schematic diagrams of dielectric breakdown caused by holes

3 结论

(1) 在SHH应力下,Vth的退化量大于Idsat的退化量,Idlin退化量最小。

(2) SHH应力受衬底偏置的影响,衬底偏置越大,器件参数退化越大,击穿所需时间越短。

(3) 在 SHH注入过程中,SILC刚开始随着应力作用时间增加不断减小,这是由于正电荷在氧化层中积累的结果。随后,栅电流慢慢增加,当在氧化层中积累的正电荷密度达到一个临界值时,栅电流氧化层被突变,从而发生击穿。

(4) 在SHH应力过程中,氧化层发生击穿是热空穴注入导致Si—O键断裂所致。

[1] HU Shi-gang, HAO Yue, MA Xiao-hua, et al. Study on the degradation of NMOSFETs with ultra-thin gate oxide under channel hot electron stress at high temperature[J]. Chinese Physics B, 2009,18(12): 5479-5484.

[2] HU Shi-gang, HAO Yue, MA Xiao-hua, et al. Hot-carrier stress effects on GIDL and SILC in 90nm LDD-MOSFET with ultra-thin gate oxide[J]. Chin Phys Lett, 2009,26(11):017304-1-01704-4.

[3] HU Shi-gang, HAO Yue, MA Xiao-hua, et al. Degradation of ultra-thin gate oxide NMOSFETs under CVDT and SHE stresses[J]. Chin Phys Lett, 2008,25(11): 4109-4112.

[4] Weir B E, Alam M A, Silverman P J, et al. Ultra-thin gate oxide reliability projections[J]. Solid State Electron, 2002, 46(3):321-328.

[5] Wu E Y, McKenna J M, Lai W, et al. The effect of change of voltage acceleration on temperature activation of oxide breakdown for ultrathin oxides[J]. IEEE Electron Device Lett,2001, 22(12): 603-605.

[6] Cheung K P. Temperature effect on ultrathin SiO2timedependent-dielectric-breakdown[J]. Applied Physics Letters,2003, 83(12): 2399-2401.

[7] Buchanan D A, Stathis J H, Cartier E, et al. On the relationship between stress induced leakage currents and catastrophic breakdown in ultra-thin SiO2based dielectrics[J]. Microelectron Eng, 1997, 36(4): 329-332.

[8] Dimaria D J, Cartier E. Mechanism for stress-induced leakage currents in thin silicon dioxide films[J]. Journal of Applied Physics, 1995, 78(6): 3883-3894.

[9] Rodriguez R, Miranda E, Pau R, et al. Monitoring the degradation that causes the breakdown of ultrathin (<5 nm)SiO2gate oxides[J]. IEEE Electron Device Lett, 2000, 21(5):251-253.

[10] Vogel E M, Edelstein M D, Suehle J S. Defect generation and breakdown of ultrathin silicon dioxide induced by substrate hot-hole injection[J]. Journal of Applied Physics, 2001, 90(5):2338-2346.

[11] Heh D V, Vogel E M, Bernstein J B. Impact of substrate hot hole injection on ultrathin silicon dioxide breakdown[J]. Applied Physics Letters, 2003, 82(19): 3242-3244.

[12] Cho B J, Xu Z, Guan H, et al. Effect of substrate hot-carrier injection on quasibreakdown of ultrathin gate oxide[J]. Journal of Applied Physics, 1999, 86(11): 6590-6592.

[13] Zhu S Y, Nakajima A, Ohashi T, et al. Influence of bulk bias on negative bias temperature instability of p-channel metal-oxidesemiconductor field-effect transistors with ultrathin SiON gate dielectrics[J]. Journal of Applied Physics, 2006, 99(6):064510-1-064510-7.

[14] Mahapatra S, Saha D, Varghese D. On the generation and recovery of interface traps in MOSFETs subjected to NBTI, FN,and HCI stress[J]. IEEE Electron Device, 2006, 53(7):1583-1592.