基于光纤通信和PCI Express总线的高速图像传输系统

2011-07-28李明伟

李明伟,刘 鹏

(大连理工大学 信息与通信工程学院,辽宁 大连116024)

高帧频和高分辨率的图像采集在高科技研究、工业、医疗、交通等众多领域有着广泛的应用,例如航天和军工中高速物体运动轨迹的捕捉、3D动漫、视频定位和测量、高速公路交通监控等。然而,连续的图像采集将产生巨大的数据量,要实时远程传输并存储这些图像数据,就必须解决数据量的问题。

光纤通信技术具有频带宽、损耗低、抗干扰能力强等优点,广泛应用于大量数据的远程传输。与PCI、PCI-X总线相比,PCI Express(以下简称 PCI-E)总线采用了串行点对点通信,传输速率有了很大提高,PCI-E 1.0单通道的单向速率高达 2.5 Gb/s,且最大支持32位通道[1]。最新发布的PCI-E 3.0标准将单通道速率提高到了 8 Gb/s,使得PCI-E代替传统的PCI总线成为了必然的趋势。因此,选用光纤通信技术和PCI-E总线进行传输系统设计,使得高速图像到计算机端的实时远程传输成为可能,且具有很大的研究和应用价值。

1 系统方案

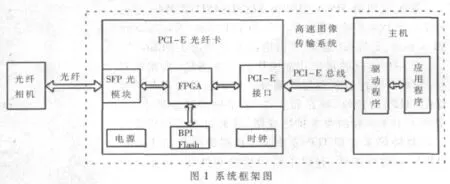

系统的整体设计方案如图1所示,本文设计的高速图像数据用于传输前端光纤相机采集的图像数据。

在硬件上,采用Spartant-6 FPGA为主控器设计了PCI-E光纤卡,实现光模块的数据收发以及整个PCI-E协议,使得设计简洁紧凑且易升级。SFP光模块完成光电信号的相互转换,BPI Flash用于存储FPGA的配置数据。板上时钟源有两个,一个来自主板的125 MHz时钟,用于PCI-E协议的实现;一个是25 MHz的时钟晶振,通过PLL芯片5倍频后用于FPGA内GTP收发器的参考时钟。在主机端,开发了Windows XP下的PCI-E驱动程序和MFC应用程序,完成高速图像的接收、处理、显示以及存储等功能。

2 FPGA逻辑设计

2.1 FPGA总体逻辑框架

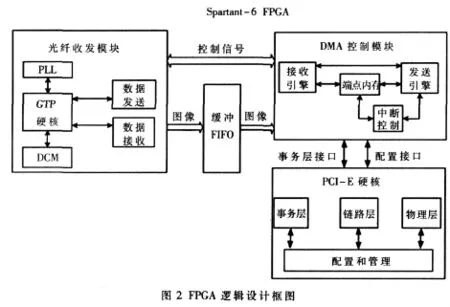

FPGA作为PCI-E光纤卡的核心控制器,不仅要完成光纤接口的数据收发,还要通过PCI-E总线与主机通信。由此可见,FPGA逻辑设计是系统设计的重点和难点,图2给出了FPGA内部逻辑框图。在接收图像时,SFP光模块接收到的串行数据流先经GTP完成串并转换,经过必要的处理后送进FIFO。FIFO可编程标志位有效时,DMA控制模块根据主机设置的参数发起DMA传输,按照事务层接口时序要求,组装数据包发送给PCIE硬核,PCI-E硬核通过PCI-E协议向主机发送数据。主机端向光纤相机发送命令的过程类似,这里不再赘述。

2.2 PCI-E端点硬核介绍

系统选用的FPGA型号为XC6SLX45TFGG484,它内嵌了一个PCI-E硬核模块,符合 PCI-E Base Specification V1.1标准,支持X1通道,单向链路速率可达 2.5 Gb/s[2]。

PCI-E硬核的顶层功能模块分为事务层、数据链路层、物理层和配置管理层四部分。事务层负责事务层数据包(TLP)的接收、缓存和发送,为了提高通信效率,还实现了PCI兼容的事务排序规则,并通过基于信用度的流控制协议来管理TLP缓冲区。数据链路层用于保证TLP传输的可靠性,提供了错误检测和恢复、初始化服务、DLLP的生成与拆解等服务。物理层使用GTP高速收发器实现,分为逻辑子层和电气子层:逻辑子层通过链路训练与状态指示状态机完成链路初始化、训练以及维护工作,并且实现了扰码与解扰码、8/10 bit编码与解码等功能;电气子层负责输入输出差分信号的接收与发送。配置管理层实现了PCI配置空间、电源管理以及中断等功能。

PCI-E硬核模块提供给用户四类接口:系统接口是时钟和复位接口;链路接口用于连接板卡的金手指;事务层接口用于TLP的发送和接收;配置接口用于配置空间的访问以及中断信号的发送。在进行DMA控制模块设计时,主要使用事务层接口和配置接口。

2.3 DMA传输逻辑设计

PCI-E总线的数据传输有可编程输入/输出 (PIO)和直接内存存取(DMA)两种方式。PIO方式通过CPU执行I/O端口命令进行数据读写,用于传输少量的数据。DMA方式在无CPU参与的情况下对存储器进行数据读写,适合大量的数据传输[3]。为了接收大量的图像数据,实现DMA传输控制逻辑,分为接收引擎、发送引擎、端点内存和中断控制4个模块。

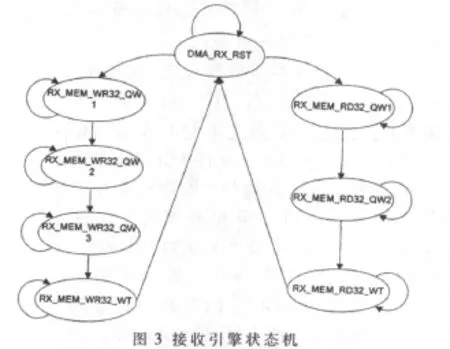

接收引擎用于解析从PCI-E硬核接收到的TLP,包括存储器读请求TLP和存储器写请求TLP,图3给出了接收引擎的控制状态机。系统复位后,状态机处于空闲状态(DMA_RX_RST),接收到数据包后,立即对数据包包头进行解析并判断TLP类型,然后跳转到相应状态。通过RX_MEM_RD32_QW1和RX_MEM_RD32_QW2对存储器读请求TLP的参数进行解析并通知发送模块进行响应,在RX_MEM_RD32_WT状态等待发送模块操作完成并返回空闲状态。对存储器写请求 TLP的操作通过RX_MEM_WR32_QW1、RX_MEM_WR32_QW2和RX_MEM_WR32_QW3三个状态完成,在RX_MEM_WR32_WT状态等待TLP完成并返回空闲状态。

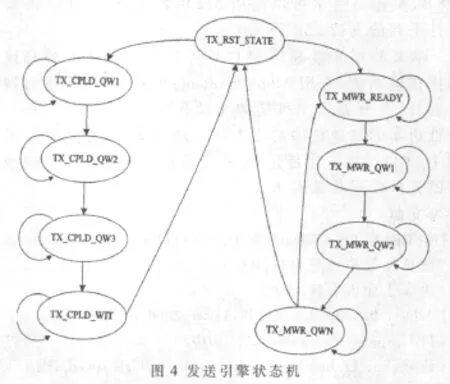

发送引擎负责TLP的封装,完成对存储器读TLP的响应,并背靠背地进行存储器写TLP的发送。发送引擎控制状态机如图4所示。复位后,状态机处于空闲状态(TX_RST_STATE),根据条件分别发送完成TLP和储存器写TLP。当收到接收引擎发来的请求信号后,立即发送完成包的包头的第一个双字,并通过TX_CPLD_QW1、TX_CPLD_QW2、TX_CPLD_QW3 三 个 状态发送数据包的其他部分。DMA传输的过程中,当FIFO可编程满标志和DMA写开始信号均有效时,进入TX_MWR_READY状态发送存储器写TLP的包头,然后通过TX_MWR_QW1和TX_MWR_QW2发送其他参数,最后在TX_MWR_QWN发送数据负载。每个储存器写TLP发送完毕后重新返回TX_MWR_READY状态,而每次DMA传输完成后进入空闲状态,等待下次DMA传输的开始。

使用FPGA内RAM块实现了端点内存,大小为1KB,被映射到计算机的存储器空间,用于实现DMA控制寄存器和存储主机发给光纤相机的命令。

中断控制模块用来控制PCI-E硬核中断的发送和禁止,根据中断时序设计状态机实现。PCI-E总线支持消息信号中断和传统中断。由于使用的Windows XP操作系统不支持消息信号中断,因此只能使用传统中断,可以通过PCI-E硬核配置向导进行设置。

2.4 光纤数据收发

光纤收发模块完成光纤通路上的数据收发,包括GTP硬核、PLL、DCM、数据接收和数据发送5个子模块。

GTP硬核模块是通过ISE IP核生成向导生成的,用来对GTP硬核进行配置。设计中,GTP主要参数设置以及注意到的问题有:(1)参考时钟REFCLK使用外部提供的125 MHz时钟,由于GTP对时钟要求比较严格,一般不使用FPGA内部DCM或PLL产生的时钟作为参考时钟。(2)使用自定义的链路协议,链路速率为2.5 Gb/s,使用8/10 bit编码。(3)comma码的设置是链路协议传输的关键,使用K28.5作为comma码。(4)物理电气参数的设置因外部SFP光模块的使用而不同,比如TX预加重、RX均衡、耦合电容、差分电平摆幅等,使用时必须使用Xilinx提供的 IP核 IBERT进行测试[4]。

光纤通路使用自定义的协议:(1)链路空闲时一直发送comma码K28.5,工作时发送需要的数据码。(2)传输图像时,为每帧图像添加帧头和帧尾,以定界每帧图像。发送模块负责向图像采集卡发送控制命令,用来设置图像传感器的参数。接收模块接收GTP输出的并行数据流,去除comma字符 K28.5和图像帧头帧尾,将图像数据流写入FIFO。

3 软件设计

3.1 驱动程序

在Windows操作系统中,为了保证系统的安全性、稳定性和可移植性,用户模式的应用程序必须通过驱动程序才能对硬件进行操作[5]。本设计使用Windows DDK开发了PCI-E接口的驱动程序,采用WDM驱动模式,支持即插即用操作。

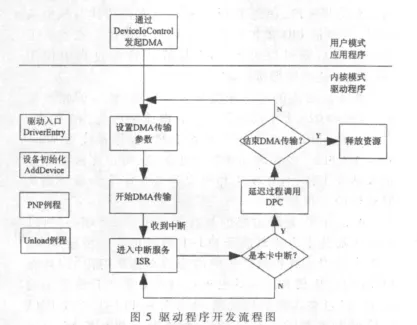

图5为驱动程序开发流程。当驱动程序收到应用程序启动DMA传输请求后,首先设置DMA传输参数,然后开始DMA传输并等待中断产生。驱动收到中断后,如果判断是PCI-E光纤卡产生的,就立刻转到延迟过程调用DPC函数,在其中设置触发事件通知应用程序,并启动下一次传输。在本驱动程序中,申请了8块DMA缓冲区进行轮流传输,这样既可以提高DMA传输的效率,又方便应用程序对缓存区内的图像数据进行操作。

3.2 应用程序

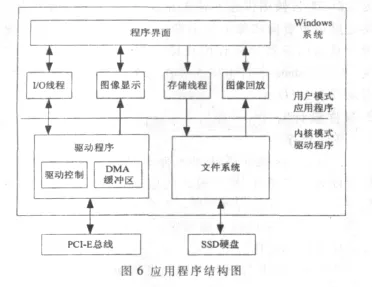

根据需要,使用VC++6.0开发了基于MFC的应用程序,完成了图像的处理、显示、存储、回放等功能。采用多线程编程,提高了程序的运行效率,在实时显示视频图像的同时,还可以完成图像存储工作。图像显示使用DirectDraw函数组,直接将图像数据送入显存,充分发挥显卡性能,消除了图像闪烁现象。使用固态硬盘进行图像数据的存储,克服了普通硬盘读写速度慢的问题。在图像存储完成之后,可以对存储的视频图像进行慢放,便于对高速运动的物体轨迹进行细致观察,并且可以调整回放的帧率。应用程序的功能结构及其与驱动程序的关系如图6所示。

4 系统测试

FPGA内逻辑均采用Verilog HDL实现,使用Xilinx ISE Design Suite 12.3完成整个FPGA流程的开发,包括仿真、综合、布局布线、调试等。利用 Xilinx的IBERT IP核进行光纤模块的测试,通过实时地改变GTP的各种参数来观察链路的状况。对光纤链路进行长时间测试发现,链路十分稳定,误码率比较小,基本在-10数量级内。驱动开发前,使用WinDriver进行寄存器读写和中断监听,以验证PIO操作和中断发送的正确性。在安装了驱动程序后就可以进行DMA传输,传输过程中使用ChipScope捕获波形进行调试。

本实验使用的光纤相机最大能以80帧/s的帧率采集1 280×1 024大小的图像,其数据速率约为 563 Mb/s。主机硬件采用Intel i5平台的组装机,操作系统为Windows XP SP3。经长时间连续工作测试,可以完成图像显示及储存工作,且系统工作稳定可靠。图7为系统测试时软件的工作界面。

本设计中,光纤通路的最高速率可达2.5 Gb/s,所以系统传输速率主要取决于PCI-E总线的实际传输速率。由于实验中光纤相机产生的图像数据速率有限,因此在FPGA内产生仿真图像数据进行PCI-E最大传输速率的测试。经过多次测试后发现,本设计中PCI-E总线DMA传输最大速率可达1.2 Gb/s,而理论上PCI-E X1通道的单向传输速率为2.5 Gb/s(考虑8/10 bit编码效率)。经详细分析,限制其传输速率的主要因素有:(1)系统采用中断方式,主机对中断的响应会占用一定时间;(2)PCIE数据包有一定的包头信息,目前使用的数据包大小为128 B,要提高速率可以改用512 B数据包,但是这需要硬件平台的支持。

本文利用光纤通信和PCI-E总线实现了一种高速图像传输系统,选用Xilinx Spartant-6系列FPGA进行硬件设计,并开发了主机端的驱动程序和应用程序,是一套低成本的高速传输解决方案。测试表明,系统速率可达1.2 Gb/s,且工作稳定,基本能满足大多数高清高帧视频图像的实时传输需求。

[1]BUDRUK R,ANDERSON D,SHANLEY T.PCI express系统体系结构标准教材[M].田玉敏,王崧,张波,译.北京:电子工业出版社,2005.

[2]Xilinx,Inc.Spartan-6 FPGA integrated endpoint block for PCI express user guide[Z].2010.

[3]Peng Yu,Li Bo,Liu Datong,et al.A high speed DMA transaction method for PCI express devices[J].Journal of Electronic Science and Technology of China,2009,7(4):380-384.

[4]Xilinx,Inc.Spartan-6 FPGA GTP transceivers advance product specification[Z].2010.

[5]ONEY W.Programming microsoft windows driver model[M].Washington:Microsoft Press,1999.