潜射导弹模型微小型内置测试系统设计

2011-07-26张斌珍刘建林

高 杰 张斌珍 刘建林

(中北大学电子与计算机科学技术学院1,山西 太原 030051;电子测试国防科技重点实验室2,山西 太原 030051)

0 引言

利用海洋进行水下军事活动的技术早己引起人们极大的重视。导弹在现代战争中具有突出地位,而潜射导弹由于其良好的生存性,愈加受到人们的重视。潜射导弹水下发射技术的研究与设计方案紧密相关,且需要大量的试验研究工作。因此,只有在充分的、大量的水下试验的基础上,才能对水下发射技术进行透彻的认识和了解,从而作出明确的方案选择。

本设计主要针对某型号导弹模型试验的实际要求,进行导弹模型水下发射动响应动态参数的测试,目的在于为某一类潜射导弹的型号设计提供重要的参考依据[1]。

1 系统试验过程

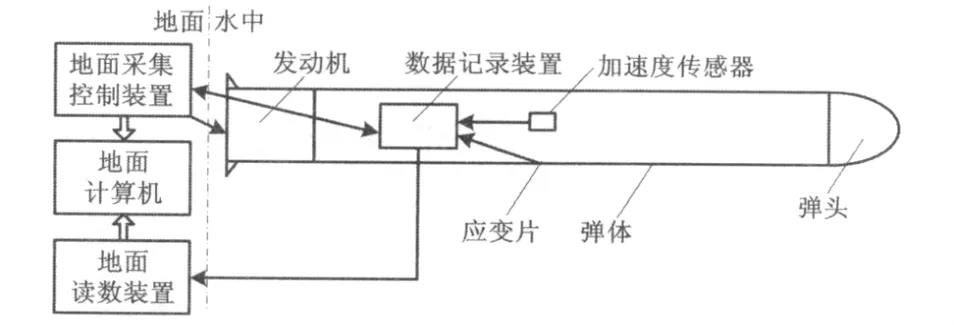

系统由导弹模型、地面计算机、传感器、地面采集控制装置和内置测试系统五部分组成,其组成原理框图如图1所示。

图1 系统组成原理框图Fig.1 Composition principle of the system

地面采集控制装置用于发动机点火,并启动触发记录装置。地面读数装置在数据记录结束后成为连接数据记录装置与地面计算机的接口。地面计算机通过地面读数装置从数据记录装置来读取数据,并且采用专用软件对数据进行显示、判读和处理等。导弹模型包括发动机、弹体和弹头等。发动机作为弹体水下运动的动力;弹体部分放置配重、数据记录装置和传感器等;弹头呈圆形,以减小水对弹体运动的阻力。测试记录装置将加速度传感器、表面压力传感器和光纤陀螺传感器的模拟信号通过变换电路转变成数字信号,并对这些信号进行记录、存储和保持。加速度传感器安装在弹体的重心处,表面压力传感器和光纤陀螺传感器安装在弹体内关心部位的壁上。

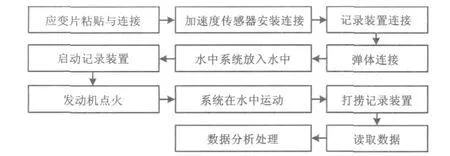

试验过程中,首先将传感器和记录器安装到弹体模型上,连接好弹体后把模型放入水中,再由岸上的控制装置进行点火和启动记录设备。试验结束后,把弹体模型打捞至岸上,连接好地面读数装置、上位机和数据记录设备,读取数据至上位机,由数据分析软件进行数据处理。试验过程示意图如图2所示。

图2 试验过程示意图Fig.2 Schematic of the experimental process

2 系统硬件设计

系统要求能对3路加速度、3路陀螺和9路表压信号进行采集,采样率为每路50 kS/s,选用12位的高精度A/D进行转换,记录时间不小于30 s。系统采用电池供电,待机时间不小于12 h。为了满足至少1.6 MB/s的数据写入能力和48 MB的数据容量,本设计选用三星公司生产的K9K8G08U0A大容量1 GB Flash,其写入速度典型值为300 μs写入2112 B。

整个系统分为电源、信号调理、电源控制、A/D转换和记录存储五个模块,其硬件设计原理如图3所示。

图3 硬件整体设计原理图Fig.3 The general design principle of the hardware

由于系统采用电池供电,而干电池和锂电池不能提供瞬间较大的电流,因此,系统采用了传感器和控制电路分开供电的双电源设计。电源模块采用北京北达众人电源技术研究所生产的DC-DC模块,它具有输入电压宽(6~18 V)、隔离电压高(>500 V)、输出电压精度高(±1%)、带负载能力强和温度系数小(0.03%)等特点,且该模块具有一个片选引脚,通过控制该引脚电平的高低,可以很方便地实现传感器的电源控制。

整个系统通过MSP430F149单片机对DC-DC模块、FPGA和Flash外围电路进行上电与断电的控制,从而实现系统的超低功耗。美国德州仪器公司(TI)推出的MSP430系列超低功耗、16位混合信号处理器集多种领先技术于一体,尤以16位RISC处理器、超低功耗、高性能模拟技术及丰富的片内外设和JTAG仿真调试为特色[2]。A/D转换模块采用AD公司生产的AD7490芯片,它具有精度高(12 bit)、16路信号同步采集、采样率高(最高1 MS/s)和功耗低(典型值5.4 mW)等特点。

在本设计中,我们以Xilinx公司生产的Spartan-E系列的XC3S100E为主控制器,它采用1.2 V的内核电压,系统时钟达到200 MHz。该器件集成了丰富的逻辑门,且内含72 kB的双端口 RAM,通过双端口RAM可以组成内部FIFO来缓存数据[3]。

在硬件设计时,需要注意以下问题。

①在电源的输入端串联一个抗大电流的二极管,以防止电源反接电流过大烧毁器件。

②由于MSP430F149单片机和XC3S100E都为低功耗器件,与TTL电平不兼容。所以必须接一个电平转换芯片74LVC4245,将5 V电平转换为3.3 V。

③由于MSP430系列单片机为超低功耗单片机,所以I/O口的驱动能力不是很强,在驱动一些功耗较大的器件时,需要增加专门的驱动芯片[4]。

3 系统软件设计

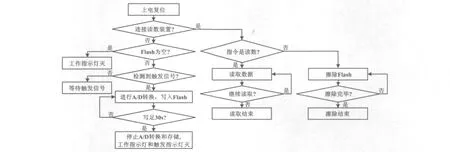

系统的软件设计由单片机和FPGA两部分组成。单片机程序流程图如图4所示[5]。

图4 MSP430F149单片机程序流程图Fig.4 Program flowchart of MSP430F149 MCU

单片机主要控制系统的电源,通过地面采集控制装置发给记录器上电指示。单片机在P1.0引脚接收到指示后,通过发送给DC-DC模块的片选引脚高电平来给传感器和记录器供电。大约1 s后,传感器上电趋于稳定,地面控制装置便会给FPGA发送一个采集触发信号。FPGA在采集完毕后发送一个高电平指示信号给单片机,单片机P1.1引脚接收到采集完毕信号后则断开传感器和记录器的电源,并进入低功耗等待状态,等待下一次的上电指令和采集指令。

FPGA主要控制A/D转换和大容量Flash的读、写和擦除操作,是整个系统的主控制器。其主要工作流程如下。

首先,FPGA检测记录器是否连接地面读数装置,如果没有,则FPGA对Flash芯片进行上电自检,检测Flash芯片是否为空,如果为空,则工作指示灯亮,否则工作指示灯灭。如果工作指示灯亮,FPGA在检测到由地面采集控制装置发出的采集触发指示后,启动A/D转换和存储数据,在采集完毕后工作指示灯和触发指示灯灭。

导弹模型在点火后,触发线会落入水中,这时往往会造成误触发进行下一次采集。因此,设计了外部复位信号,要求设备只有在复位信号和触发信号都触发的时候才开始下一次采集。双触发有效地解决了误触发的问题[6]。

记录器在采集完毕后被打捞到地面,由计算机和读数装置将数据读取到计算机硬盘,并采用专用的数据分析软件对数据进行判读、分析和描绘波形。

FPGA的程序流程图如图5所示。

图5 FPGA程序流程图Fig.5 Program flowchart of FPGA

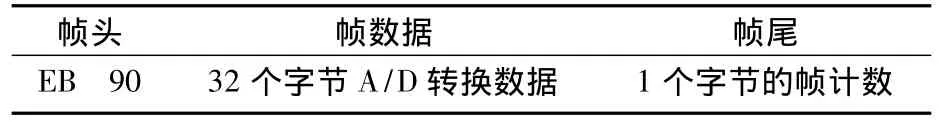

为了便于上位机对采集到的数据进行处理,必须规定好数据的帧结构。经多次试验测试,采用了以EB、90为帧头,中间为16路A/D转换的数据,其排列顺序具体为第1路高字节、低字节,第2路高字节、低字节。依次类推,直到第16路的高字节和低字节数据。其中,每路的高字节的高四位为每一路的标志位,最后为一个字节为递增的帧计数。试验证实,上述帧结构稳定可靠,能有效地防止数据的错位存储或读取。同时,在采样率一定的情况下,对于多通道的数据采集,上述帧结构能使写入的数据流最小。帧计数的加入无论对数据的写入错误还是读取错误都能起到很好的调试作用。数据帧结构如表1所示。

表1 数据帧格式Tab.1 Format of data frame

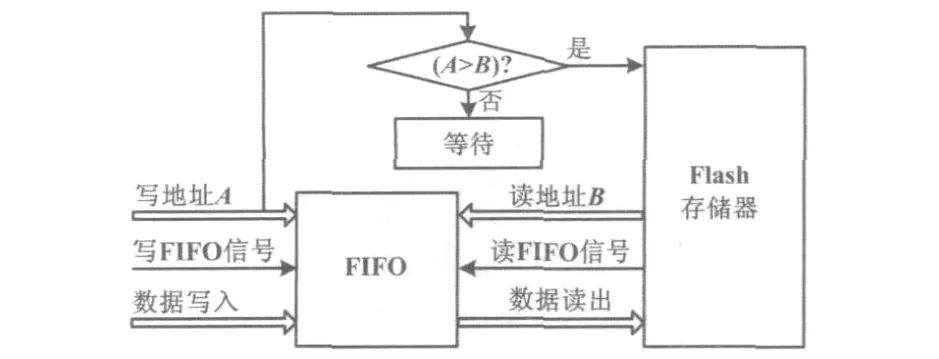

由于制造工艺水平的限制,大容量的Flash芯片往往存在无效块,所以,在存储、读数和擦除的时候必须要检测并跳过无效块。FPGA通过检测每块的第一或者第二页的第2048个字节是否为FF来检测是否为无效块,如为FF,则该块为无效块。由于Flash芯片是按页存储的,当一页写完后要进行下一页的控制字和地址的重新写入,在这段时间内必须有一个缓存装置来存储A/D转换的数据,否则数据会溢出,从而造成丢数的现象。异步FIFO由于不需要同步时钟,数据的写入和读出彼此独立,很适合于不同速度的处理器之间的数据缓存。由于FPGA内部的寄存器资源是有限的,如果在VHDL编程时用数组来构建异步FIFO结构,综合时会耗用大量的寄存器。XC3S100E内部集成了40 kB的块RAM,可以直接调用它来构建异步FIFO,提高了FPGA的芯片资源利用率。在数据读写时采用各自的时钟输入,配合各自不同的时序需要,如果写地址A大于读地址B,则数据写入Flash芯片,否则数据写入内部FIFO中缓存。内部FIFO功能示意图如图6 所示[7]。

图6 内部FIFO功能示意图Fig.6 Schematic of inner FIFO function

下面以Flash的页编程时序为例来说明对Flash的操作。Flash芯片控制时序由命令锁存使能信号CLE、芯片使能信号、地址锁存使能信号ALE、写使能信号、数据输入和输出端口I/OX和Flash芯片反馈信号R组成。Flash页编程时序如图7所示[8]。

图7 Flash页编程时序图Fig.7 Programming sequence of Flash page

具体的页编程时序为首先写入命令字80 H,接着在四个写周期内分别将字节地址、页地址和块地址按顺序依次写入,然后从FIFO中读取2 kB的数据,最后写入页编程命令字10 H。此后,Flash会返回状态信号,在大约 40 μs的时间内,都会一直为低电平,说明Flash一直处于忙状态,此时,对Flash进行任何操作,其都不会有响应;当为高电平,在一页数据写入结束时,开始写入下一页数据。信号是Flash工作状态的真实反映,为了防止信号抖动对Flash工作状态的误判,必须对信号进行软件消抖处理。

4 数据读数与分析

当数据采集完以后,需要将数据读取到上位机,以便软件进行数据处理。这时,远程读数装置便是连接上位机与记录器的桥梁。远程读数装置主要由FPGA、RS-422接口芯片MAX3087、高速数据缓存FIFO和USB单片机CY7C68013组成。Cypress公司推出的USB接口芯片CY7C68013除集成了超强的USB2.0引擎SIE外,还集成了改进的增强型8051内核。所以,开发者只要具有8051单片机的基础和初步的应用程序编程能力,就可以快速开发USB接口[9]。

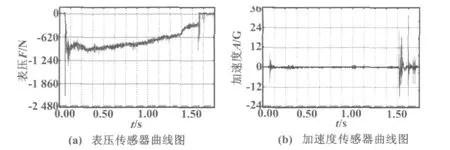

读数时的数据流程为首先读数装置将记录器的数据经RS-422总线接口远程读取到FPGA,然后将数据缓存到大容量的高速缓存FIFO。当FIFO半满后,半满信号经FPGA传递给CY7C68013,CY7C68013接收到半满信号后,将数据经GPIF接口打包上传至上位机。试验后上位机还原的波形如图8所示[10]。

图8 试验波形图Fig.8 Waveforms of experiments

5 结束语

本文针对某潜射导弹模型的点火发射试验的具体要求,设计了基于MSP430F149单片机和FPGA的超低功耗数据采集系统。系统利用双电源供电和MSP430F149单片机控制系统的电源以及配置本身的省电模式,在用电池供电的情况下实现了系统的超长待机;通过手动复位和触发双触发模式,有效解决了系统的误触发,提高了系统的可靠性;通过FPGA对A/D转换和大容量Flash芯片的控制[11-12],完整地获取了试验数据;利用USB接口实现数据的高速传输,兼容性强,充分利用了微机的资源。实践证明,本系统不仅体积小、功耗低,而且便于维护与升级,具有较大的实际应用价值。

[1]张文栋.存储测试系统的设计理论及其应用[M].北京:高等教育出版社,2002.

[2]沈建华,杨艳琴,翟骁曙.MSP430系列16位超低功耗单片机实践与系统设计[M].北京:清华大学出版社,2005:2-10.

[3]覃永新,陈文辉,章帆.实时视频数据采集的FPGA实现[J].电子技术应用,2009,35(9):1 -4.

[4]刘国勤.基于FPGA和DSP的数据采集器设计与实现[J].舰船电子工程,2006,26(6):2 -3.

[5]张贵清,张天序,颜露新,等.数据采集的硬件自校准方法与FPGA实现[J].数据采集与处理,2006(B12):236-241.

[6]胡大可.MSP430系列单片机C语言程序设计与开发[M].北京:北京航空航天大学出版社,2003:2-5.

[7]潘松,王国栋.VHDL实用教程[M].成都:电子科技大学出版社,2005:20 -27.

[8]张明,王礼平.基于FPGA的非对称同步FIFO设计[J].电子设计应用,2005(1).

[9]钱峰.EZ-USB FX2单片机原理、编程及应用[M].北京:北京航空航天大学出版社,2006:20-27.

[10]吴振宇,常玉保,冯林.基于FPGA和USB2.0的高速数据采集系统[J].仪器仪表学报,2006(z1):1-3.

[11]黄容兰,万德焕.基于FPGA的A/D转换采集控制模块设计[J].数据采集与处理,2009,24(S1):238 -240.

[12]陈明义,连帅军,周建国.基于FPGA的Flash控制器系统设计与实现[J].电子科技,2008,21(7):11 -13.