基于FPGA的数据采集系统中20MHz模拟通道设计

2011-07-05曹保银

曹保银

(宿州学院机械与电子工程学院,宿州23400)

0 引言

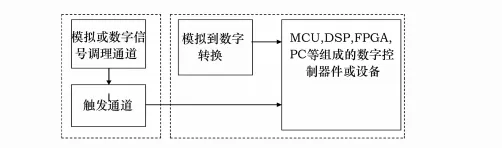

广义上说数据采集是指为了测量电压、电流、温度、压力或声音等物理现象。工业时代的数据采集过程需要大量的人工参与,过程复杂,精度低,耗时长,由于过多的人工的参与必然导致错误率的上升。随着技术的发展,人类进入信息化时代,以计算机和数字化器件为代表的信息计算发展迅速,数据采集技术自然而然的与现代信息技术溶为一体,通过模块化硬件、应用软件和计算机的结合进行测量,成为了当今现代数据采集系统的普遍特征[1][2]。典型数据采集系统结构如图1所示。

图1 典型数据采集系统结构

如图1所示,一个基本数据采集系统主要有两大部分组成:模拟部分和数字部分,模拟部分主要由信号调理通道和触发通道以及一些附属的控制电路组成,他们的功能是把被测信号可控的调节到模数转换器的输入量程之内,以适应模数转换的要求。数字部分主要完成两大功能[2][3]:1)控制整个系统的运行;2)采集存储,处理发送经过数字化的数据信息。其主要由MCU,DSP,FPGA,PC或工控机等组成。在某些应用中,数据采集系统可以配有显示屏,触摸板等人机交互系统。同时可能带有以太网,RS-485,RS-232,USB等通信总线,由此数据采集系统可以独立主机的形式或是集群节点的形式运行,以满足不同的应用需求。数字化仪器是数据采集的一个重要应用领域,不得不提到的就是美国泰克公司和美国安捷伦公司,他们作为世界领先的数字存储设备以及其他数字化仪器的先进供应商,其数字存储示波器的模拟带宽和采样率不断刷新业界记录,模拟通道作为数字存储示波器的关键部件,其性能的高低一直是制约数字存储示波器的关键因素。泰克和安捷伦公司都使用了集成化模拟通道设计,目前泰克公司提供的数字存储示波器的模拟带宽已经达到了20GHz,采样率达到了50GSPS,其售价一般在单台20万美元。高性能数字存储示波器广泛的应用于高速系统的信号抖动测量,高速差分串行信号测量,射频信号测量等。安捷伦公司作为另一家全球先进的仪器制造厂商,其产品涉及军事,医疗,工业,民用,实验室,以及教育领域。其在数字存储示波器产品上也代表了全球最高水平其目前产品中有模拟带宽为13GHz,实时采样率为40GSPS的数字存储示波器。相对于国外水平国内数据采集技术尚处于起步阶段,具有代表性的国内厂商主要是北京普源和扬州绿杨,北京普源是一家本土的一起制造厂商,其数字存数示波的模拟带宽从20MHz—300MHz,采样率从200MSPS—2GSPS,这已经是国内的最高水平,但是相对与国外产品还是有非常大的差距,扬州绿杨是另一家本土仪器设备厂商,其产品性能略低于北京普源的产品。造成国内产品在性能上与国外有巨大差距的原因主要是:国内的芯片研发和制造技术严重落后与国外,国外的数字仪器的模拟通道设计往往是把各种分立的运放,比较器甚至是连同模数转换器集成于一块独立的芯片中,而国内现在还处于基于分立元件的组合设计上,高频段的信号对电路的连线长度,通道的一致性,温度的一致性,电路基板的介电常数的一致性有非常苛刻的要求,而这些要求是分立元件难以满足的,所以目前国内产品在性能上严重受制于芯片设计和制造技术上。20MHz 模拟通道的设计[4][5][6][7],主要包括信号调理通道、触发通道和控制通道的设计。通道设计有关问题介绍如下。

1 信号调理通道的设计

数字采集系统的必须环节是模拟信号的数字化处理,所以模数转换器[4](ADC,以下简称ADC)是系统中必须器件,然而ADC对输入信号的幅度,基线,频率有一定要求,所以信号调理通道的作用就是把不能满足ADC输入要求的待测信号调节到ADC的输入范围之内,并且这种调节是可以人为定量控制的。其信道调理通道的结构框图如2所示。

图2 信道调理通道的结构框图

待测信号先经过耦合切换,来决定信号进入系统的耦合方式,由于信号调理通道工作在正负5V电源轨上,所以如果输入的信号大于系统电源轨,则需要预先分压,另一方面组成信号调理通道的高速运放往往在信号幅度较小的时候,会取得更好的性能,所以信号调理通道是按照先衰减再放大工作的。信号在经过程控放大后进入电平移位级,电平移位级将放大到适合幅度的信号的基线移位至ADC的要求后,信号被送往ADC完成量化。

2 触发通道的设计

数据采集系统采集的数据量是巨大,然而并不一定所有的数据都是我们需要的,如果我们只想观察电源上电那一瞬间的过程,或者是当发现信号上偶发的毛刺之后,才开始记录。另一方面由于数据采集系统所配备的高速存储器是有限的,而在采样速度非常快时,就无法一直不停的连续采样,这时数据采集系统会工作在采样,缓存,发送,这样的循环中,如果此时我们采集的是一个正弦信号,那么在每次数据采集,采集系统必须从同一个起始点开始采集,这样发送到屏幕的波形才是一个稳定的信号波形,否则可能会出现波形重叠,抖动等现象,这样的问题在数字存储示波器中是时常发生的。其触发通道结构框图如图3所示。

系统预设电压作为高速比较器的一个输入,而高速比较器的另一个输入来自信号调理电源的每个信号调理通道的触发信号是来自高速比较器中待测信号的当前值与系统预设的电平值比较而来的,触发信号将被馈送到数据采集系统的负责采集控制的FPGA或者是MCU,DSP等数字器件作为启动采样的信号。数据采集系统的控制部分通过操作DAC来产生一个输出,也就是调理后的待测信号,如果信号调理的输出大于系统的预设电平,则比较器输出高电平,反之输出低电平,在本设计中比较器的输出电平是3.3V-LVTTL兼容的。这种电平标准时当今最广泛的电平标准之一。

图3 触发通道结构框图

3 控制通道的设计

如果把数据采集系统的组成硬件分成模拟部分和数字部分两大类,那么控制通道的作用就是提供一个适合的接口可使数字部分控制模拟部分。本系统中对控制通道的设计大致分为4部分:

1)对高压衰减级的控制;

2)对程控放大级的控制;

3)对程控移位级的控制;

4)对触发通道的控制。

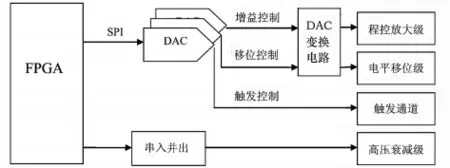

其控制通道的结构框图如图4所示。

FPGA发出两类控制信号:其一是通过DAC产生的电压信号用于控制信号调理通道程控放大级的增益,以及电平移位级的移位电平,还有触发通道的触发比较电平;其二是通过串并准换后的开关信号,用于信号调理通路前段的高压衰减级控制。

从表5可以看出,转移概率矩阵P的变化对m*和N*都有影响。值得注意的是,当维修费用较高的团队有更大的概率称为“先行团队”时,全周期期望维修费率却不总是增加的。进而可以得出以下结论:降低维修费用不是减小全周期费用率的唯一选择,也不一定是有效的选择,在制定维修决策时,应全面考虑维修费用和维修效果的影响因素。

图4 控制通道的结构框图

4 PCB中抗干扰的设计

1)相邻导线的干扰

在布线时应遵守3W原则,即线间距要大于线宽的3倍,同时应在PCB底面连续覆铜,这样可以阻断导线周围磁场,也能在一定限度上减小线间干扰。本设计为双通道设计,在PCB布局上两个通道要尽量远离,这样可以防止通道串扰。

2)外界电磁干扰

在电路板上方焊接金属壳,并将金属壳接地,作为对外电磁波的屏蔽体,可以减少外界电磁干扰。

5 PCB中高速运放布线[10]

1)减小寄生效应

寄生效应就是当电路工作频率升高到一定程度后,线性元件变成了非线性元件,比如电容,电阻,导线,焊盘,过孔等等,有他们产生的寄生电容和寄生电感对高速模拟电路的破坏巨大。典型运放电路在不考虑寄生效应的电路图如图5所示。

图5 不考虑寄生效应的运放电路图

高频时考虑电路寄生效应后的电路图[7][9]如图6所示。

图6 考虑寄生效应的运放电路图

图7 寄生效应的带来的危害图

从上图可以看出运放的负载电容越大,幅频曲线上的峰越高,这会造成信号的过冲和震荡。而寄生电容会进一步恶化这种情况。在设计PCB时高速运放下部的覆铜一定要挖掉,尽量少打过孔,这样可减轻寄生效应。

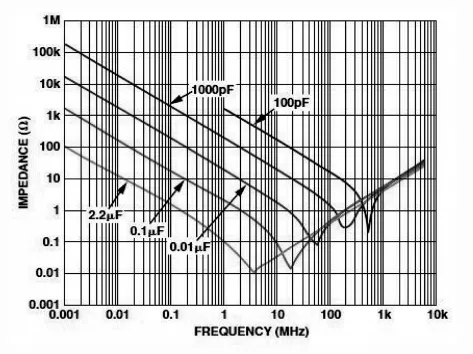

2)电源旁路设计[9]

前边的段落中提到,电源旁路可以减少电源噪声的影响,图8给出不同电容阻抗与噪声频率的曲线。

图8 不同电容阻抗与噪声频率的曲线

可以看出电容越小其高频阻抗越小,可以在运放的电源脚放在不同容值电容的组合从而形成一个宽屏带的噪声低阻通路用于旁路噪声信号,减少对运放的干扰。本设计中使用的是2.2uF钽电容与0.1uF陶瓷电容并联做为运放电源旁路。

3)地平面设计

接地平面起到公共基准电压的作用,提供屏蔽,能够散热和减小寄生电感(但它也会增加寄生电容)的功能。虽然使用接地平面有许多好处,但是在实现时也必须小心,因为它对能够做的和不能够做的都有一些限制。理想情况下,PCB有一层应该专门用作接地平面。这样当整个平面不被破坏时才会产生最好的结果。千万不要挪用此专用层中接地平面的区域用于连接其它信号。由于接地平面可以消除导体和接地平面之间的磁场,所以可以减小印制线电感。如果破坏接地平面的某个区域,会给接地平面上面或下面的印制线引入意想不到的寄生电感,接地面和除了寄生电感有关之外,还和信号的环路噪声有关,信号在远端发出,到达终端后通过接地平面返回,高速信号的返回路径就在发射路径下方的接地面上,如果返回路径的接地面不完整,则返回信号就会绕道,那么发射信号与返回信号环绕的面积就会增大,所产生的噪声也就会增大,同时也更易受外界的干扰。所以在本设计中所有的关键信号布线尽可能走PCB顶层,这样尽可能的保证PCB底层接地覆铜完整。在本设计中所有的关键信号路径下的接地面都是完整的,为的就是尽可能做到最佳的接地平面设计。

6 结束语

20MHz模拟通道的具体硬件电路图以及PCB的实物图都已经制作好,并通过仿真软件MULTISIM、PSPICE以及ALTIUM DESIGNER仿真验证设计的正确性,并成功应用在“基于FPGA和3GUSB的高速数据采集系统的设计[11]”项目中,而且也为以后进行更宽带宽的模拟通道的设计奠定了坚实的理论基础。

[1]林长青,孙胜利.基于FPGA的多路高速数据采集系统[J].电测与仪表学报,2005,42(2):52-54.

[2]徐海军,叶卫东.FPGA在高性能数据采集系统中的应用[M].北京:机械工业出版社,2005.

[3]宋勇,李清宝,白燕等.高精度实时数据采集系统的实用设计[J].微计算机信息,2005,21(6):66-68.

[4]Brad Brannon&Rob Reeder.高速 ADC 测试和评估[M].美国模拟器件公司(ADI),2008.

[5]Sergio.Franco,基于运算放大器和模拟集成电路的电路设计[M].西安交通大学出版社,2004:46-76.

[6]吴大正.信号与线性系统分析[M].北京:高等教育出版社,2006:32-48.

[7]市川裕一.高频电路设计与制作[M].北京:科学出版社,2004:67-82.

[8]Walt.Jung,运算放大器应用技术手册[M].北京:人民邮电出版社,2008:42-53.

[9]Eric.Bogatin.信号完整性分析[M].北京:电子工业出版社,2003:68-74.

[10]John Ardizzoni.高速PCB布线指南[M].北京:美国模拟器件公司(ADI),2008.

[11]Michael D.Ciletti.Verilog HDL 高级数字设计[M].北京:电子工业出版社,2003:68-81.