基于FPGA的多通道SSI通信控制器设计

2011-07-03张鹏飞

张鹏飞,王 玮,赵 哲

(西北机电工程研究所,陕西 咸阳712099)

在嵌入式系统应用领域中,需要完成的任务越来越复杂,应用环境也越来越恶劣,要求嵌入式计算机在体积不断减小的情况下,具有更强的处理功能和较低的功耗。本文采用FPGA[1]设计技术,利用VHDL硬件描述语言[2],将4个同步串行接口协议SSI IP核[3]模块组成一个功能可扩展的SoPC架构的从通信控制器,从而使主从控制器协同工作,保证了整个嵌入式系统在通信速度达到技术要求的前提下,能更有效地降低系统功耗与体积。

1 SoPC设计方法

可编程片上系统SoPC(System on Programmable Chip)(或称基于大规模FPGA的单片系统)是一种灵活、高效的SoC解决方案,将处理器、存储器、I/O口等系统需要的功能模块集成到一个PLD器件上,构成了一个可编程片上系统,具有灵活的设计方式(可裁减、可扩充、可升级),并具备软硬件在系统可编程功能。

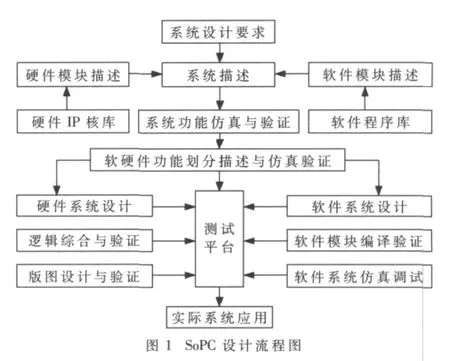

图1为典型的基于IP核库的SoPC设计流程,主要是利用软硬件协同方法完成整个系统设计。

2 通信控制器架构模块组成

本文采用了一种全新的SoPC体系结构,整个嵌入式系统主要由主控制器和FPGA(从控制器)两大功能单元组成,其结构如图2所示。主控制器选用TI公司的TMS320C6713 DSP,虚框内的电路单元则为所设计的多通道同步通信控制器(也即从控制器)。通过TMS320C6713处理器芯片自带的EMIF模块与基于FPGA实现的多通道同步通信控制器进行数据交换。基于FPGA实现的从处理器内部选用MC8051 IP软核来控制和管理4路SSI协议通信控制器,TMS320C6713与MC8051之间通过双端口RAM共享数据和交换信息,整个系统采用中断控制方式,实现主/从控制器协同处理任务。

由图2可知,该SoPC架构控制器内部可划分为4大模块:从处理器MC8051 IP核、4路SSI协议通信控制器、双端口RAM和中断逻辑单元。下面分别对4个主要组成模块进行介绍。

2.1 从处理器

为了提高同步通信控制器的自主性与灵活性,在FPGA内部嵌入一个微控制器80C51 IP核作为同步通信控制器的核心控制单元。MC8051 IP软核的特点主要有:指令集与工业标准的8051控制器兼容;新的体系结构使单片机处理速度提高了10倍;无多路复用I/O端口,实行输入和输出接口完全隔离;256 B的内部RAM;最高可达64 KB的内部ROM和最高可达64 KB的外部RAM;容易调整或改变VHDL源代码实现相关的核扩展功能;可通过VHDL常量进行参数化设置。

图3是MC8051 IP核的内部功能结构图。从图中可以看到,该IP核包括的子模块有:算术逻辑单元MC8051_ALU、串行接口单元 MC8051_SIU、定时器/计数器单元MC8051_TMRCTR、核心控制单元MC8051_CONTROL、内部数据存储单元MC8051_RAM、内部程序存储单元MC8051_ROM和外部数据存储单元MC8051_RAMX。其中,N表示MC8051_SIU和MC8051_TMRCTR两个单元根据实际需要可灵活制定的个数,其范围值为1~256,可在VHDL代码中改变参数C_IMPL_N_TMR的值进行设置。

2.2 SSI协议控制器

同步串行接口SSI(Synchronous Serial Interface)[4]通信协议是同步串行通信协议的一种类型,该协议主要包含帧同步信号GATE、时钟信号CLK和串行数据DATA三类信号,其时序关系如图4所示。

在图4中,帧同步信号GATE有方式1和方式2两种可选择方式协调控制时钟信号CLK和串行数据DATA。方式1用虚曲线①表示,在该方式下,整个系统空闲时,GATE一直处于高电平状态,当触发一个瞬态低电平脉冲后,DATA在GATE信号的上升沿根据系统配置要求进行传输,同时GATE保持高电平。方式2用实曲线②表示,该方式下当系统空闲时,GATE一直处于低电平状态,当触发一个瞬态高电平脉冲后,DATA在GATE信号的下降沿进行传输,同时GATE保持低电平。在上述两种方式中,DATA可在CLK的上升沿或者下降沿保持稳定并进行采集。

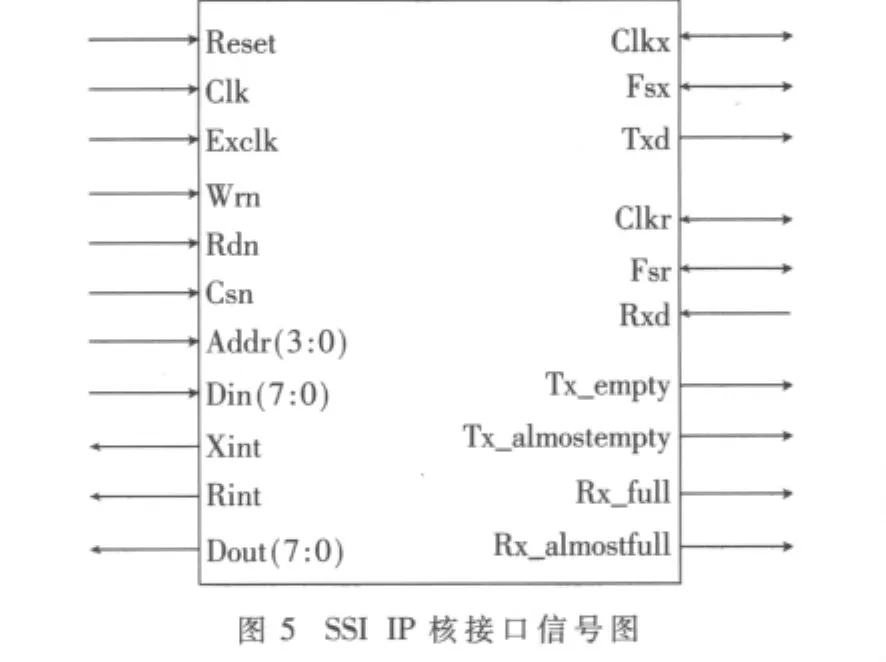

SSI IP核接口信号图如图5所示。

本文中共定义了4路(A~D)相同结构的SSI IP核,MC8051通过中断和查询方式对4路通信协议控制器进行数据的收/发操作控制。

2.3 双端口RAM

MC8051中的外部数据存储器MC8051_XRAM存储空间最高可达到64 KB,本设计用VHDL语言生成一个32 KB的外部数据扩展双端口存储器MC8051_XRAM,一端供MC8051 IP核操作,另一端供DSP操作,通过地址线译码,从而为MC8051_XRAM和4路SSI协议控制器提供cs_x和 cs_a~cs_d等片选信号。输入 MC8051_XRAM模块的地址线为addra(15:0),实际使用到的地址线空间为addra(14:0),支持 32 KB寻址空间。

2.4 中断逻辑单元

中断逻辑单元的操作地址为FFD3H,当DSP向该地址进行写操作时,中断逻辑单元将向多通道同步通信控制器发出低有效的中断信号;当多通道同步通信控制器中的MC8051向该地址进行写操作时,中断逻辑单元将清除中断。该中断逻辑单元的信号接口信息如表1所示。

表1 中断逻辑单元接口信息表

中断逻辑模块单元的功能仿真如图6所示。由图6可知,中断逻辑模块单元功能仿真正确。

3 功能仿真

利用Xilinx ISE和ModelSim SE工具对多通道同步通信控制器进行综合,得到相关的资源占用情况和最大运行速度如表2所示。

表2 多通道同步通信控制器综合报告

选中A路通道对并行数据的发送进行仿真测试,其测试仿真如图7所示。从图可以看出,并行数据Data在MC8051工作时钟Wr_clk和外部分频时钟Exclk作用下,通过设置A通道内的寄存器组合达到最终串行数据的发送。从而可以验证,数据发送仿真功能正确。

选中B路通道对外围串行数据的接收进行仿真测试,其测试仿真如图8所示。从图可以看出,串行数据Rxd在MC8051工作时钟Clk和外部分频时钟Exclk作用下,通过配置B通道内的寄存器组合得到并行数据的接收。从而可以验证,数据接收仿真功能正确。

本文以Xilinx公司的FPGA器件为设计平台,采用VHDL硬件描述语言,设计了一种SoPC架构的从通信控制器,并对设计方案进行了仿真与验证,得出了设计方案的正确性,并已成功用于某遥测数据工程实践中,因其兼具较高的数据传输率、IP核的可移植性和灵活扩展性而容易推广使用。

[1]任晓东.CPLD/FPGA高级应用开发指南[M].北京:电子工业出版社,2003.

[2]侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,2001.

[3]冯春阳,张遂南.三线制同步串行通信控制器接口设计[J].现代电子技术,2009,306(19):80-82.