基于EnDat协议的解码及VHDL设计※*

2011-06-25彭建新盛德军王宏峰熊益群

彭建新,盛德军,王宏峰,熊益群

(1.衡阳北方光电信息技术有限公司,衡阳 421001;2.国防科技大学;3.中国人民解放军总装驻衡阳地区军事代表室)

彭建新(工程师),从事光电稳定平台、DSP及嵌入式系统设计及研究。

引 言

通过位置编码器获取位置值的数字驱动系统和反馈环,需要编码器快速传输数据和高可靠性地传输,而且还必须提供一些附加信息,例如驱动系统相关参数、补偿表等。为使系统具有更高可靠性,编码器还必须具有错误检测和诊断功能。EnDat2.2可传输绝对式或增量式编码器的位置值,也能传输或更新保存在编码器中的信息或保存新信息。由于采用串行数据传输方式,它只需要4条线。数据传输保持与后续电子设备时钟信号同步。传输的数据类型(位置值、参数或诊断信息等)通过后续电子设备发至编码器的模式指令选择。纯串行的EnDat2.2接口也适用于高安全性应用[1]。高安全性位置测量系统可被用作单编码器系统,与安全控制系统一起用于控制类别SIL-2级(IEC61508标准)或性能级别“d”级(ISO13849标准)的应用[2]。

电气驱动使用的旋转编码器必须满足高标准要求。它必须工作可靠,能提供可靠的测量数据,包括用在恶劣环境中。高质量扫描系列编码的绝对位置刻轨能满足这些要求。在海德汉公司编码器内进行细分和生成位置值可以进行高可靠的纯数字数据传输,降低后续信号处理电子单元的性能要求。基于EnDat2.2协议的海德汉编码器的工作原理是光电扫描结构化刻线的光栅尺[3]。采用光学扫描原理的测量系统在精度、运行平稳度及减少驱动系统发热现象等方面拥有优势[4]。

基于EnDat2.2协议的位置编码器的上述优势,在数控机床、机械制造、电梯、军用运动控制伺服系统中获得了广泛的应用。

[5]给出了基于NiosII软核绝对式编码器的解码硬件的实现框图,未给出EnDat编码器解码的具体实现过程。参考文献[6]给出了EnDat接口的粗略介绍、后续电子设备的方案介绍、FPGA+宏的介绍,对于CPU而言只是对FPGA虚拟映射到CPU寄存器的调用,但未给出EnDat编码器的解码实现方法。

本文针对海德汉公司基于EnDat2.2协议的ROC425绝对式光电编码器的控制及读取涉及的接口电路设计、相关VHDL程序的设计、DSP程序的联合设计等的解码全过程实现进行了详细的分析。

1 EnDat接口特性

1.1 接口特点

① 高性能低成本。通用的接口适用于所有的增量和绝对式编码器,具有更经济的电能消耗、小尺寸、紧凑的连接方式、快速的系统配置,零点可根据偏置值浮动。

② 更好的信号质量。编码器内部特别的优化提高了系统的精度,为数控系统提供更好的轮廓精度。

③ 更好的实用性。自动系统配置功能、数字信号提高了系统的可靠性,监控与诊断信息有利于系统的安全,冗余码校验有利于可靠的信号传输。

④ 提高了系统的安全性。两个独立的位置信息及错误信息位,数据的校验和及应答。

⑤ 适用于先进的技术发展。高分辨率、短控制周期、最高16MHz时钟频率,安全设计理念适用于直接驱动技术。

1.2 接口定义

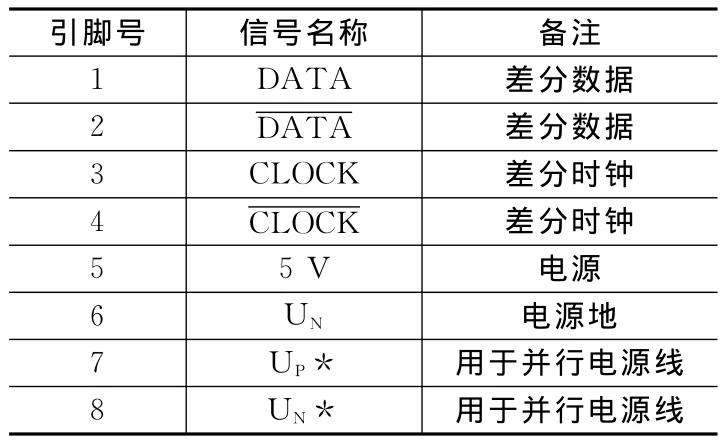

微型M12,8针连接件。连接技术简单,8芯单屏蔽电缆。信号接口定义如表1所列。

表1 信号接口定义

1.3 接口时序特性

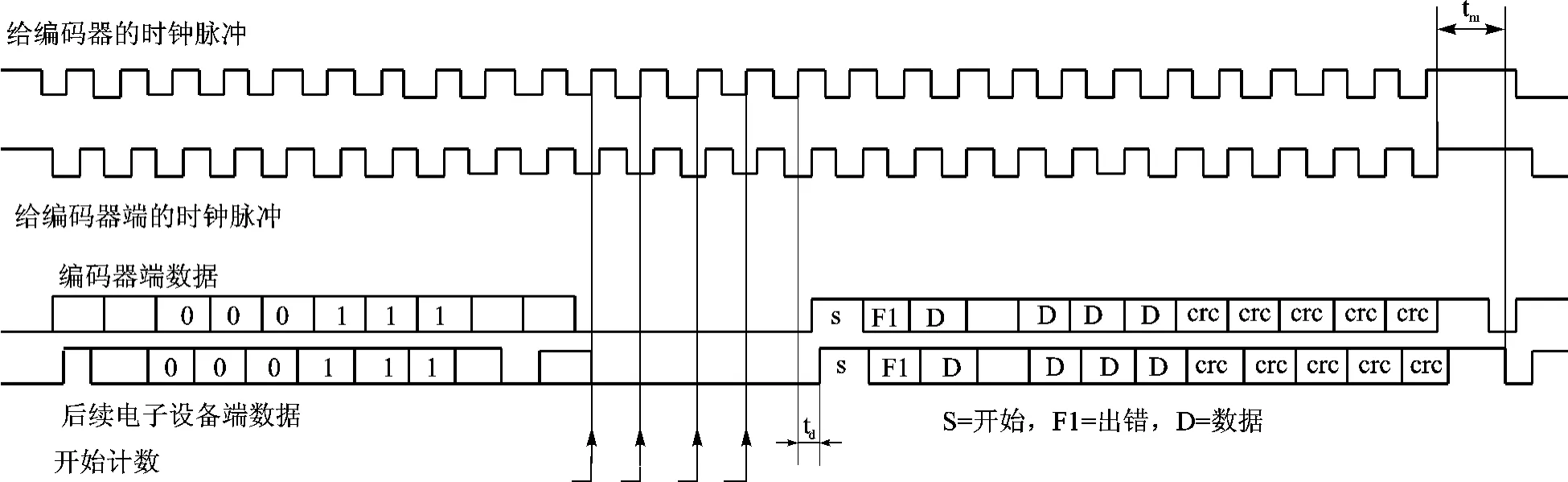

EnDat2.2编码器典型接口时序如图1所示。后续电子设备提供给编码器的时钟脉冲用于同步数据传输。不传输数据时,时钟信号为高电平。从图1可以看出,给编码器端的时钟脉冲相对于给编码器的时钟脉冲存在电路传输延时。

图中下半部分以编码器发送位置值指令模式000111示意,模式指令伴随时钟的上升沿发出。数据包发送与数据传输同步。传输周期从第一个时钟下降沿开始。编码器保存测量值并计算位置值。2个时钟脉冲后,后续电子设备发送模式指令。模式指令发送后,经过若干(图中以4个上升沿加箭头示意)时钟,从启动信号开始到前一个时钟的上升沿用td表示,编码器回送数据以启动信号开始,接着是错误位,然后是数据位,数据位低位在前,高位在后,数据位长度取决于所采用的编码器,以循环冗余校验位结束。数据字结尾处,时钟信号必须置为高电平。10~30μs后或1.25~3.75μs(EnDat2.2可用参数调整的恢复时间tm)后,数据线返回低电平。然后,时钟信号启动新的数据传输。

2 接口电路设计及编码器解码总构

2.1 采用RS485转换芯片与编码器进行接口

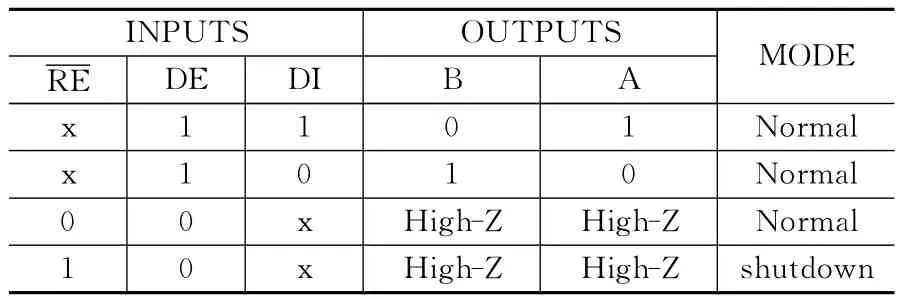

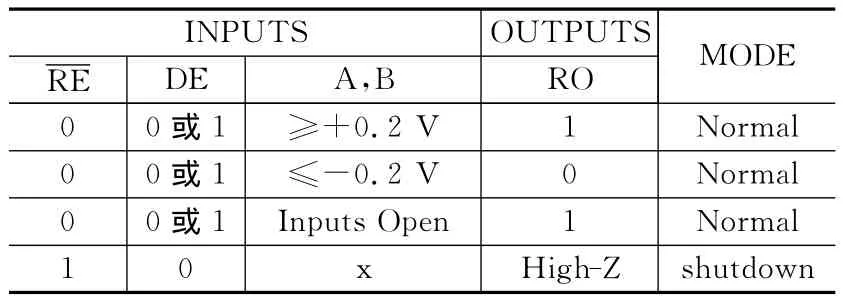

MAX3485功能表如表2、表3所列。其中表2为后端电子设备向RS485芯片发送数据状态表。表3为编码器端向RS485芯片发送数据状态表。

表2 后端电子设备向RS485芯片发送数据状态表

后端电子设备向RS485芯片发送数据时,RE为任意电平,DE为固定高电平,由DI发起,通过B、A差分传输出去。传输过程中存在一定的传输延迟。在编码器端进行差分接收。

图1 编码器典型接口时序

表3 编码器向RS485芯片发送数据状态表

编码器向RS485芯片发送数据时,RE为低电平,DE为任意电平,通过编码器A、B端接收来自编码器的数据,在RO端输出,后端电子设备在RO端接收来自编码器的数据进行接收解码。

RS485芯片与编码器接口图如图2所示。图2(a)一方面接收后端电子设备向编码器发起的模式指令,另一方面接收来自编码器应答的位置值及校验码,通过VHDL程序及根据EnDat协议特性切换收发的时机。图2(b)为后端电子设备向编码器发出的时钟,通过芯片的DI引脚输入,图2(a)的所有收、发数据均伴随此时钟建立。

图2 RS485芯片与编码器接口图

2.2 基于EnDat编码器接口解码总构

在DSP端定时中断程序中产生一相对固定周期的方波信号,控制时钟分频器分频输出的时钟。该时钟作为FPGA内部硬件的全局时钟,同时作为编码器的时钟信号。方波周期的低电平期间时钟分频器进行减计数分频,高电平期间时钟分频器输出恒置为高。64位计数器根据锁相环flag标志(为0)进行加计数或对输出清0(flag标志为0),在第11个时钟脉冲后输出控制标志c=0,否则c=1。64位译码器前10个时钟周期输出DE信号为1,表明后端电子电路向RS485发送数据,否则DE信号为0,进而打开RS485的接收通道,移位寄存器传输模式指令。标志c为1时,且判断到RS485之RO端是否发生上升沿事件,由该事件触发a信号提供给串并转换,标志着FPGA后续电子电路接收编码器回送位置值的开始。串并转换在标志信号a为1时完成串行数据往数据寄存器的传递。数据转换完后,给出锁相环标志flag=1,表明本轮数据传输结束。串并转换后的数据高字节直接送往三态缓冲选择器,低字节经锁存后送往三态缓冲选择器,在DSP端读取虚拟映射的内存,通过内存地址的译码控制串并转后数据的提取。FPGA构建的结果是在DSP端形成了若干个寄存器,在DSP端操作的只是寄存器层面,非常方便。编者注:基于EnDat编码器接口解码结构框图略。

3 VHDL程序设计

3.1 VHDL程序设计内容

VHDL程序涵盖时钟分频器、计数器、译码器、移位寄存器、接收事件触发器、串并转换、锁存器、三态缓冲选择器、虚拟内存地址译码控制等。

3.2 部分VHDL程序设计

3.2.1 时钟分频器VHDL程序

构建进程,在锁相环标志flag为1及clr为1时,否则分频器分频,实际应用选择q5输出实现32分频。

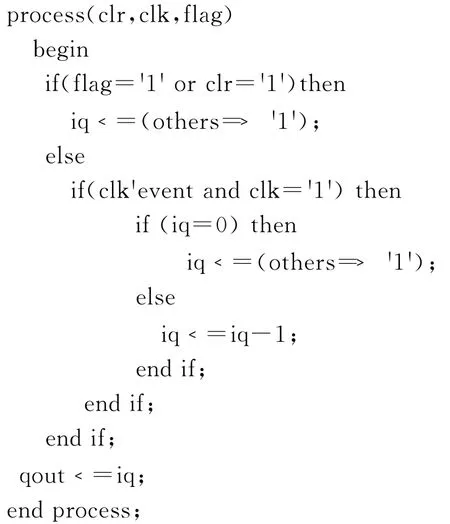

3.2.2 计数器及模式指令发送VHDL程序

构建进程,在第11个时钟周期输出控制标志,用于控制是向编码器发送数据还是从编码器接收数据。

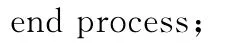

3.2.3 接收事件触发VHDL程序

构建进程,接收编码器传输开始设定标志a=1。

4 实验结果

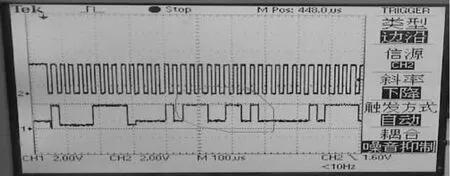

实际调试效果如图3所示。示波器的上半部分为后续电子电路向编码器发起的时钟脉冲,下半部分为向编码器发送的模式指令与编码器回送的位置值在数据线上的合成。整体效果完全符合EnDat编码器的时序特征。

图3 实际调试效果

结 语

基于EnDat协议的编码器接口电路简单,但要实现解码存在一定的难度。本文创造性地提出了后端电子电路对该协议解码的全过程,后端处理器对数据的提取只是虚拟内存层面的操作。给出了相关部分VHDL程序设计,通过所有的编译、仿真、在线调试及器件封装后,在某光电侦察项目中获得了成功的应用。在FPGA资源充足的情况下,针对该编码器的特点同时可以构建与微处理器级相对应的所有模式指令(如故障、状态等)的寄存器。

编者注:本文为期刊缩略版,全文见本刊网站www.mesnet.com.cn。

参考文献

[1]HEIDENHAIN.EnDat2.2——位置编码器的双向数字接口,2008.

[2]HEIDENHAIN.高安全性位置测量系统,2011.

[3]HEIDENHAIN.绝对式旋转编码器的高质量扫描方法,2008.

[4]HEIDENHAIN.针对直接驱动系统的光栅/编码器,2008.

[5]孙士尉,陈秀才,王风瑞.ENDat接口的绝对式编码器值的读出方法研究[J].江苏电器,2008(10).

[6]HEIDENHAIN.EnDat接口编码器数据采集设计方案,2008.

[7]侯伯亨,刘凯,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学,1999.

[8]TI DSP系列中文手册:TMS320C28X系列DSP的CPU与外设[M].张卫宁,译.北京:清华大学出版社,2004.