新型的嵌入式存储器测试算法

2011-06-22官枫林习友宝

官枫林,习友宝

(电子科技大学 电子工程学院,成都610000)

引 言

随着微电子产业日新月异的发展,ⅠC设计的规模与集成度越来越大。SoC是现阶段ⅠC设计的标准结构之一,通常由CPU核、存储器、逻辑电路、各种外设及接口组成,而存储器通常占据芯片的绝大部分。常用的嵌入式存储器有ROM、Flash、SRAM、DRAM等。典型的存储器的基本结构如图1所示,存储器主要由地址线、数据线、控制线、地址译码器、存储单元阵列、输入/输出电路、读出放大器、写驱动电路等部分组成。

图1 存储器的基本结构

嵌入式存储器的测试主要分为3类[1]:

① 直流参数测试(DC Parameter Testing)——校验工作电流、电平、功率、扇出能力、漏电流等参数特性。

② 交流参数测试(AC Parameter Testing)——检测建立时间、保持时间、访问时间等时间参数特性。

③ 功能测试(Functional Testing)——测试存储器件的逻辑功能是否正常,对存储单元、读出放大器、写驱动等产生的物理故障进行检测。

本文主要讨论第3类中嵌入式存储器的功能测试。

1 采用的方法

现有的嵌入式存储器测试算法都是直接对存储器内部单元直接测试[2],所用的算法在测试复杂度和故障覆盖率之间难以找到一个平衡点。本文介绍的方法采用外围互连线测试和内部单元结合的测试算法,摒弃了以往只是测试内部单元的算法,提高了测试效率,故障覆盖率也有所提升。

外围互连线测试:假设存储器本身功能正常,控制线也总是可控的,故障只是由于器件装配引起的,需要对存储器的地址线和数据线可能的短路和开路故障进行测试。

内部单元测试:对存储器的译码、读写等功能进行测试。

两种测试的目的不一样。内部单元测试的目的在于判断内存单元的好坏,所以在程序设计中只要发现故障就可以终止退出,同时报告发生故障的内存单元;外围互连测试的目的不仅仅在于发现故障,而且还要求能对故障进行精确定位。所以在算法设计中需要将这两步测试过程按顺序执行完毕。

2 嵌入式存储器测试的故障模型

对故障机理进行分析,建立相应的故障模型是产生算法的前提。

2.1 外围互连线测试的故障模型

对于外围互连线,本文采用的是固定故障模型,固定故障也是存储器外围互连线的主要故障。固定故障模型包括固定逻辑故障、固定开路故障和桥接短路故障。固定逻辑故障是指由于物理缺陷,数据线或者地址线的状态不受输入的控制,绑定到逻辑0或者1状态,包括 S-A-1(Stuck-at-1)和 S-A-0(Stuck-at-0)故 障。而在外围互连线测试中,固定开路故障和桥接短路故障往往可以等价于S-A-0或S-A-1的固定逻辑故障,在此不作赘述。

2.2 内部单元测试的故障模型

对于内部单元,除了上文提到的类似的固定逻辑故障和固定开路故障模型,还有状态转换故障(transition fault)、数据保持故障(data-maintaining fault)、状态耦合故障(coupling fault)和多重写入故障(multiple access fault)等[4-5]。

状态转换故障:0→1或1→0的状态转换至少有一个不被正确执行。

数据保持故障:存储单元无法保持一个逻辑值持续一定的时间。

状态耦合故障:当且仅当单元j处于某一个特定状态y(y∈{0,1})时,单元i总是为某一个确定值x(x∈{0,1}),则称单元i耦合于单元j。耦合关系不一定具有对称性,也就是说单元i耦合于单元j,并不一定单元j也耦合于单元i。

多重写入故障:对单元i写入x(x∈{0,1})导致单元j也写入了x,则称单元i有多重写入故障。多重写入故障不一定具有对称性。

3 存储器的测试算法

目前存储器的测试算法中比较著名的有March算法及其各种变种算法、Gallop算法,这些算法太过复杂,测试效率不高[5]。本文所提出的算法不仅故障覆盖率能够达到实际应用标准,而且测试效率有明显提高。

3.1 外围互连线的测试算法

存储器外围互连线包括控制线、数据线和地址线。对于控制线的测试没有比较规范的测试方法,但是如果控制线存在故障,存储器基本无法正常工作。一般而言,控制线的故障在对数据线和地址线的简单测试中就能被发现,所以不作专门测试。

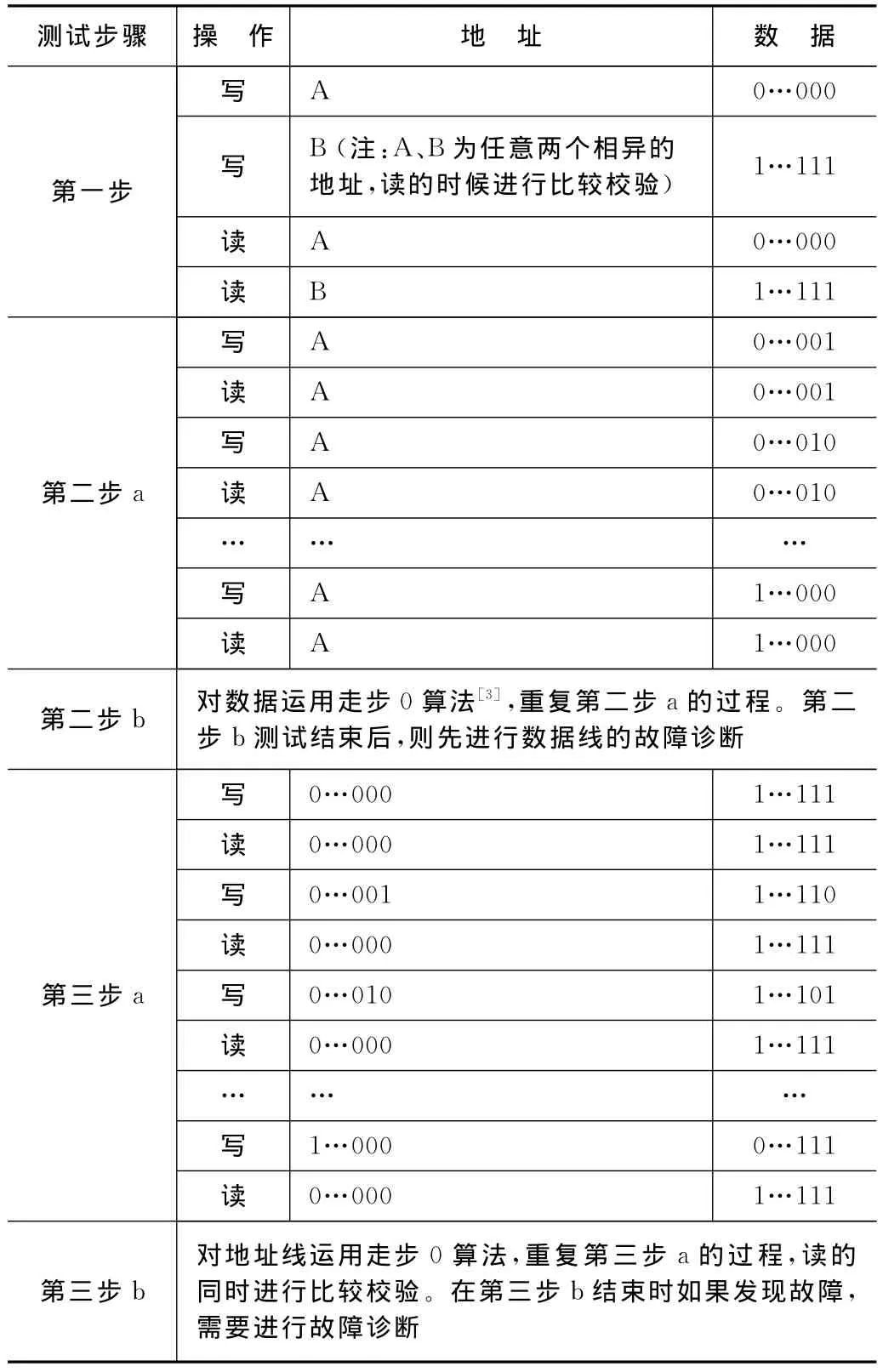

数据线和地址线的测试的目的不只是发现故障,更主要的是精确定位故障以便很容易地进行修复或更换。采用“三步法”,该算法不仅能够精确地定位故障,而且还能区分固定逻辑故障和桥接短路故障这两种不同类型,具体算法如表1所列。

表1 外围互连线测试“三步法”

第一步测试数据线是否存在开路故障和固定逻辑故障,第二步测试数据线是否存在短路故障,第三步测试地址线是否存在开路或短路故障。在第二步测试结束时进行数据线故障诊断,在第三步测试结束时进行地址线故障诊断。

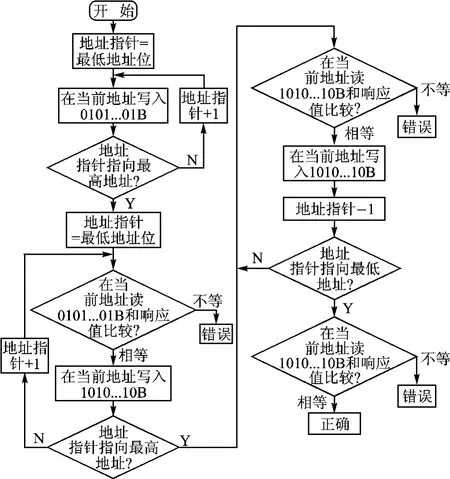

3.2 内部存储单元测试算法

内部单元的测试算法[2]有Checkboard测试、MSCAN算法、March算法、GALPAT、跨步法等算法,本文对内部存储器单元进行测试,采用如图2所示的棋盘和跨步相结合的算法,在检测数据单元时采用棋盘图形,在检测地址译码时采用跨步图形,将棋盘测试法和跨步法各自的优点合二为一。

图2 棋盘跨步相结合算法

4 测试结果

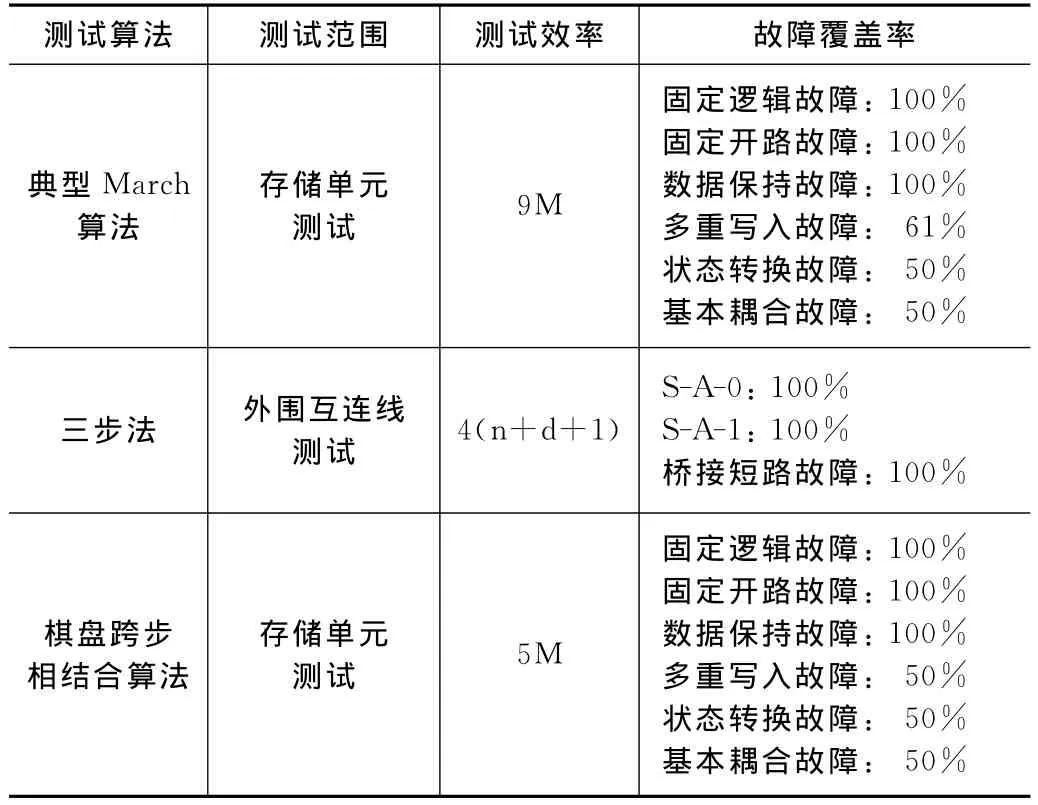

将本文所涉及的算法进行测试效率与故障覆盖率的分析,并将结果进行比较,如表2所列。其中d为地址线数目,n为数据线数目,M为待测存储器空间大小,一般M=2d。从表中可以看出这些算法的测试效率比典型的March算法效率高很多,三步法的测试复杂度只有4(n+d+1),棋盘跨步相结合的算法的测试复杂度也有5M,在故障覆盖率也满足应用要求,完全可以为实际项目所采用。

表2 各种测试算法比较

[1]高成,张栋,王香芬.最新集成电路测试技术[M].北京:国防工业出版社,2009:66-67.

[2]雷绍聪,邵志标,梁峰.超大规模集成电路测试[M].北京:电子工业出版社,2008:285-291.

[3]范志翔.存储器内建自测试及内核功能测试研究[D].南京:东南大学,2006.

[4]李吉.确定性逻辑内建自测试技术研究[D].北京:中国科学院研究生院计算技术研究所),2005.

[5]张曦,朱一杰,俞军.一种优化的Flash存储器测试算法[J].微电子学与计算机,2004(5).

[6]VAN de G.Using march test to test SRAMs[J].ⅠEEE Design & Test of Computers,1993,10(1):8214.