工程爆破的FPGA多路同步数据采集控制器

2011-06-22张晶威

张晶威

(中北大学电子测试技术国家重点实验室,太原030051)

引 言

工程爆破中,药包爆炸后能量的释放、传递、做功中必然有一部分能量转化为地震波[1-2]。由地震波而引起的地表物体颠簸摇晃的现象和后果是地震效应,是影响最大的工程爆破危害[1-4]。

目前对地震波的振动测量是监测与评估爆破地震效应的重要途径。地震波在空间中的方向并不确定,但是矢量在三维空间可以分解,因此测量三维空间的地震波矢量分量是必要的。测量三维的地震波矢量分量需要时间上同步,保证叠加后的矢量和是实际地震波矢量。

在振动观测点,传感器信号采集到的多路模拟信号是时间同步的。模拟信号经过量化,在数字信号处理和存储后,识别的数字信号也需同步以便后期处理。传统上的方法多为模拟信号经过多路模拟开关,模数转换器件分时处理[5-7]。事实上,这并没有实现严格意义上的时间同步。

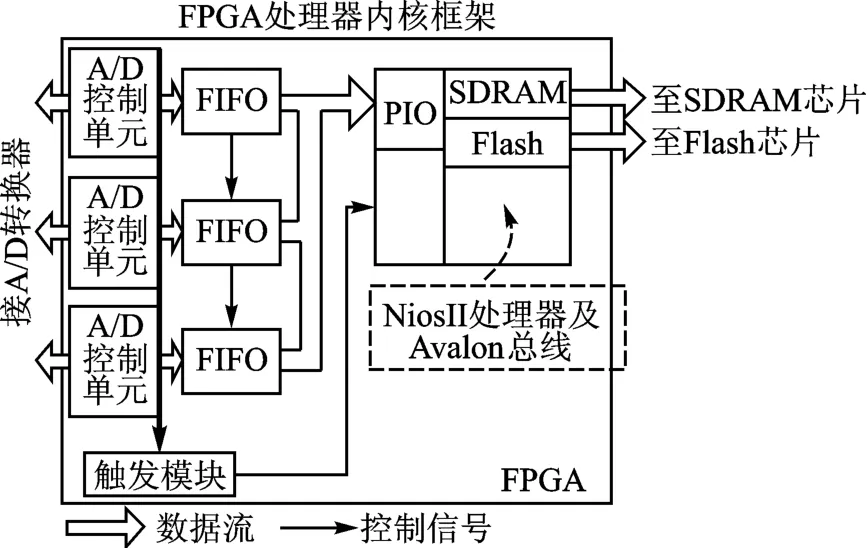

本文介绍了一种利用现场可编程逻辑器件FPGA作为爆破振动数据记录仪的设计方案,同时结合FPGA的嵌入式处理器内核,构建了逻辑控制与CPU一体的SoC架构。

1 系统方案

本设计方案整体思路是对3路独立的A/D转换器分别设置双时钟FIFO存储单元,保持采样同步一致性。在3路A/D转换器采样的同一个模数转换周期,将FIFO存储数据顺序读出并顺序写入SDRAM。

FPGA芯片为主控制器,主要包含如下逻辑结构:A/D控制单元、FIFO、嵌入式软核处理器、存储触发控制单元。

本系统使用的是Altera公司的CycloneII系列芯片。3路A/D转换控制单元分别控制串行A/D转换器,控制单元共用同一个系统时钟分频后的时钟和系统复位。控制单元还包含A/D转换器的控制时钟,数据串/并转换,FIFO写时钟和FIFO的写使能信号。使用FPGA中的双时钟FIFO宏模块,写入时钟由A/D控制模块驱动,读时钟和SDRAM存储器共同使用系统时钟。嵌入式NiosII软核处理器中添加了PIO接口模块、SDRAM接口、Flash接口。

基于FPGA芯片的系统框架如图1所示。

图1 控制器系统框架

2 系统的工作原理与硬件实现

2.1 A/D转换器与A/D控制单元

A/D控制单元是FPGA中的逻辑功能模块,3路A/D控制单元由同一时钟驱动,并共用系统复位,保证工作时序同步。

该系统的目标采样信号频率在10~103Hz范围,采用Burr Brown公司一款串行A/D转换器ADS1286。该A/D转换器为12位精度,连续采样状态为16个A/D驱动时钟完成一次采样—数据输出。其时序工作图如图2所示[8]。

图2 ADS1286基本工作时序

在A/D转换器的信号采样段,即一个采样过程的前两个时钟周期执行对目标信号的采集;在数据转换段执行12位数据由高位至低位的串行输出。片选使能信号置高后完成一次数据采集过程,此时处理输出的数据是完整的一个采样点数据。

该A/D控制单元包含以下5个模块:

①通过系统时钟分频模块得到A/D转换器的驱动时钟。

②片选使能信号模块控制连续的数据采样,经过15个A/D驱动时钟生成一个片选使能信号的高电平,此高电平占A/D驱动时钟一个周期,即16个A/D驱动时钟完成一次采样。

③串行—并行数据转换。考虑芯片I/O引脚限制,并且系统的采样频率不高,采用串行输出的A/D转换器比较合适,但系统内部的数据总线为并行,因此A/D控制模块需要将串行数据转换成同总线同位宽的并行格式[9-10]。该模块工作过程是,首先在FPGA中构建一个12位的存储空间,在A/D采样输出串行数据开始,每个A/D驱动时钟传输至相应的12位存储空间位置,最低位数据在AD驱动时钟的上升沿采样完成,片选使能信号在时钟的下降沿变化,因此在片选使能信号的上升沿处理的数据是完整的一次采样数据。

④输出写FIFO的时钟。FIFO具有双时钟,其中写时钟频率较低。16个A/D驱动的时钟周期完成一次完整的数据采样,因此将A/D驱动时钟8分频得到写FIFO驱动时钟。

⑤触发SDRAM存储信号。该信号同FIFO写满信号输入或门,输出至NiosII软核的一个PIO输入接口,提供一个中断标志,触发SDRAM存储。

结合Modelsim仿真波形和A/D控制单元的波形图,可知A/D控制单元的控制时序逻辑。另外A/D控制单元的边沿控制稳定,确保了采集数据可靠。

2.2 NiosⅠ嵌入式处理器的数据输入

同步采集的3路信号在FIFO中存储,FIFO完成了数据的缓冲,然后将FIFO中的数据顺序转移至外部存储器。

FIFO存储数据向SDRAM转移的由一个PIO中断触发,该中断标志由A/D控制单元设定FIFO存储数据量,计数器记满后产生一个出发标志,计数器参数可调。另外FIFO深度是有限的,存满后产生FIFO满信号,将二信号输入或门,输出为SDRAM的存储触发标志。一路FIFO读空以后,下一路FIFO数据读出。3路FIFO数据由FIFO读出转移至SDRAM的过程要在下一次FIFO写入数据之前,也就是由15个A/D驱动时钟的时间完成此工作,而读FIFO和写SDRAM都是由系统时钟(是A/D驱动时钟的103倍)驱动的,故单路FIFO存储数据可以由此来确定。

2.3 SDRAM控制

SDRAM存储器的优点是存储空间大、价格低,适合做数据的缓冲区;缺点是控制相对复杂,使用NiosII软核控制器可以降低SDRAM控制的难度。NiosII提供了SDRAM 的控制接口,硬件结构搭建完成后,在NiosII IDE集成开发环境中编写C语言程序控制SDRAM。当总线访问SDRAM接口时,通过写操作函数IOWR和读操作函数IORD即可进行SDRAM存储器的读写[11-12]。

2.4 FPGA的配置与Flash数据存储

基于SRAM原理的FPGA芯片掉电后程序丢失,另外暂存在SDRAM芯片中的数据也会掉电丢失。利用Flash芯片的掉电程序保持特性实现对FPGA的初始化配置和大量采集数据的保持。需要注意的是,写入Flash的偏移地址大于程序代码在Flash存储空间的地址,否则系统程序被覆盖,无法对FPGA正确配置。

3 工程案例

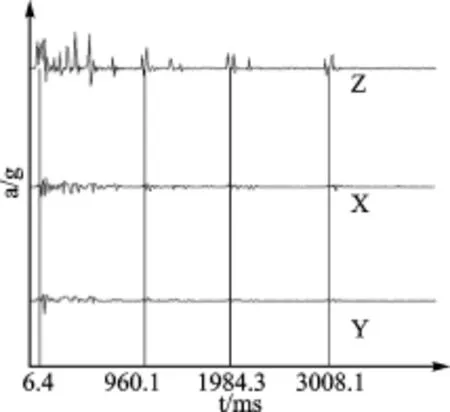

图3为系统在某工程采集的爆破振动加速度波形。工程上采用了高精度的电子雷管,设置段间延期为1 s。从图中采集波形可以看出,段与段之间的数据采集严格分开。另外从图中Z轴(垂直地面方向)对应X、Y轴的波形,可见3路数据采集波形的一致性好。

图3 某工程3路采集加速度波形

结 语

本文提出的基于FPGA的多路数据同步采集系统实现了多路数据采集的时间同步,为工程爆破振动分析提供更有价值的数据,是爆破振动分析监测的得力工具。另外,嵌入式软核与逻辑模块结合成片上系统,设计的电路系统更为简单可靠。此外本系统还可以多台组网,通过安置方式的不同来灵活设计监测方案,此方面尚需进一步研究。

[1]张雪亮,黄树堂.爆破地震效应[M].北京:地震出版社,1981.

[2]孟吉复,惠新斌.爆破测试技术[M].北京:冶金工业出版社,1992.

[3]张立.爆破器材性能与爆炸效应测试[M].合肥:中国科学技术大学出版社,2006.

[4]言志信,等.爆破地震测试及建筑结构安全标准研究[J].岩石力学与工程学报,2003,22(11):1907-1911.

[5]周朝阳,等.基于FPGA的多通道串行A/D转换器的控制器设计[J].现代电子技术,2008(20):55-58.

[6]Kirianaki N V.Data acquisition and signal processing for smart sensors[M].John Wiley&Sons,2001:51-58.

[7]张东升,等.基于FPGA的高速采集系统设计与实现[J].电子技术应用,2006(5):76-77.

[8]Texas Instruments.12-Bit Micro Power Sampling Analog-To-Digital Converter,2000.

[9]Peter Wilson.FPGA 设计实战[M].杜生海,译.北京:人民邮电出版社,2009.

[10]EDA先锋工作室.Altera FPGA/CPLD设计[M].北京:人民邮电出版社,2011.

[11]Altera Corporation.NiosII Software Developer's Handbook,2009.

[12]Altera Corporation.Embeded Design Handbook,2011.