基于AD9910的通用雷达信号产生器

2011-06-22饶睿楠任亚欣

李 辉 饶睿楠 任亚欣

(西安电子工程研究所 西安 710100)

1 引言

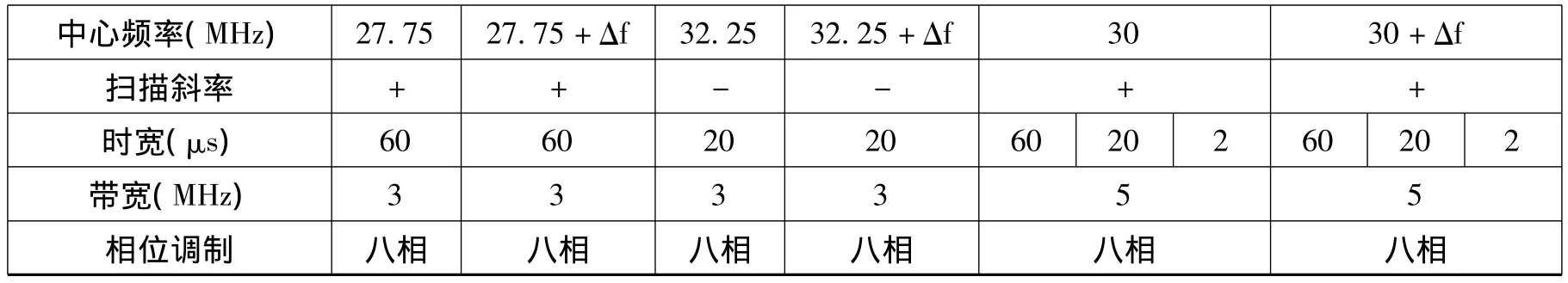

现代雷达中,通常要求雷达发射信号具有多种形式,如工作时采用的不同带宽不同时宽的线性调频信号、非线性调频信号、单频信号、相位编码信号,以及为进行系统调试、校正而使用幅度调制的上述信号等。这就给雷达信号产生器提出了具有多种工作模式的要求[1]。应用于某雷达系统的信号波形要求如表1所示,表1中的f为多普勒频移。尽管本系统中对信号模式要求不是很多,但是为了实现通用化这就要求在设计的开始就以模块化和通用化的思想从软件和硬件方面进行构思设计。本文将MATLAB工具软件和Quartus软件联合使用,通过MATLAB以参数化的方法产生mif格式的信号波形数据和DDS寄存器配置数据,这些数据作为FPGA中RAM对应的数据在FPGA开发中直接使用。在FPGA设计中采用多层状态机的方法来实现对AD9910的多模式动态配置[1]。由于采用了参数化方法使得当信号参数改变时,只需在MATLAB中修改信号相应参数产生对应的数据替换原来的数据就可以实现新参数的信号,从而实现了信号产生器的通用化,节省了软、硬件开发成本。

表1 某雷达信号产生器的工作模式

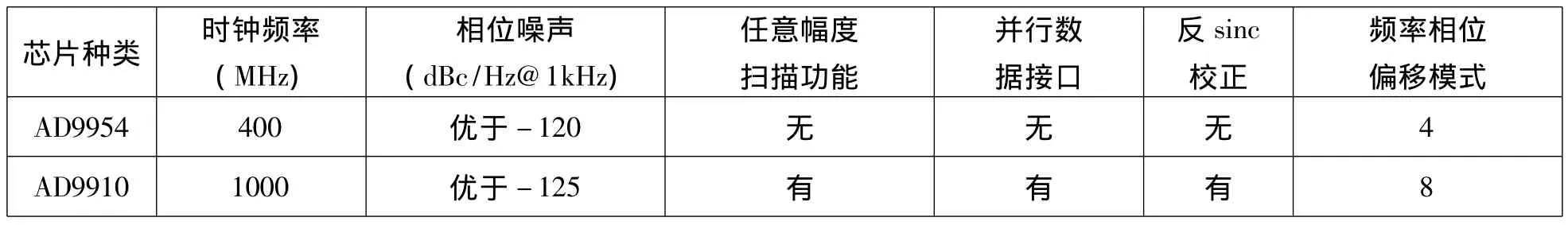

2 AD9910的结构和特点

AD9910是ADI公司近年来推出的一款性价比很高的DDS芯片,它与AD9954的功能比较如表2所示,可以认为它是AD9954的升级版,其内部结构图如图1所示,由图1可以看出:它主要由DDS核、14位DAC、线性斜坡发生器、1024 X 32 bit RAM、时钟倍频电路、时序控制逻辑、串行控制接口和高速并行数据接口等8部分组成。它支持的最高时钟频率达到1000MHz。其内部集成的静态RAM从逻辑上划分为八个区,分别由外部引脚Profile0~2进行选择,这八个区分别由寄存器 Profilei(i=0,1,2,3,4,5,6,7)控制。该RAM中的数据可以作为频率控制字、也可以作为相位偏移字,还可以作为幅度与相位偏移字用于角度调制,RAM主要用于预先定义好的调制。AD9910主要有4种工作模式:单频模式、RAM调制模式、DRG调制模式和并口调制模式。在单频模式下,AD9910输出连续波信号。AD9910共有8个64位单频信号寄存器,可以存储8个单一频率控制字,每个寄存器中包含了频率控制参数、相位控制参数和幅度控制参数。利用芯片管脚Profile0~2可以选择使用哪个Profile寄存器。在RAM调制模式下,用户可以任意改变DDS信号控制参数来产生各种信号,典型应用如FSK、PSK、ASK以及用户可自定义的非线性扫描信号。这种模式下的RAM寄存器和单点调制模式下的单频信号寄存器复用同一地址,通过芯片的功能控制寄存器CFR1、CFR2来控制选用哪种模式。DRG调制模式与RAM调制模式实现功能相类似,不同点是该模式利用累加器对DDS所需的信号参数进行调制。在这种模式下,可以产生较好的线性调频信号。并口调制模式主要应用于需要频率或者相位极快变化的场合,例如跳频合成器、高速波形发生器等。因为AD9910提供了更新速率可达250MHz的l6bit快速编程的并行接口,每隔8ns即可更新一次32bit的频率控制字。在各个工作模式下对芯片的操作只需要选择相应的模式,并写入相应的控制字即可。根据AD9910的功能特点及设计要求,在本文中选择使用的是RAM调制模式。

表2 AD9910与AD9954主要功能对比

图1 AD9910的结构框图

3 系统实现方案

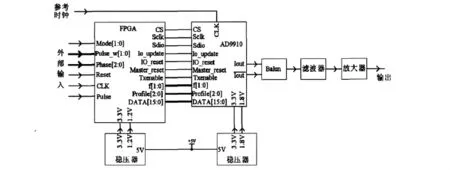

系统采用FPGA作为控制电路的核心,通过AD9910的串口对其进行动态配置来实现通用雷达信号产生器,其系统框图如图2所示。图2中稳压器对+5V的电压进行稳压处理,产生+3.3V、+1.2V、+1.8V电压分别为FPGA和AD9910供电;FPGA根据外部输入信号的变化对AD9910进行动态配置,在配置完成后根据外部的输入脉冲触发AD9910输出一定参数的复杂信号;AD9910输出的信号通过Balun实现差分到单端信号的转换,再经滤波器滤波后由放大器对信号进行放大后输出。

3.1 硬件设计

在进行硬件设计时,为了实现通用化需要考虑以下几个问题:一是AD9910的输入参考时钟,采用外部直接输入时钟还是通过内置的PLL对输入的频率较低的时钟进行倍频而得到最终的频率较高的时钟信号;二是系统中的关键信号如串口配置时钟Sclk、配置数据Sdio和同步时钟信号等要按照高速信号来处理;三是信号输出电路部分的Balun、滤波器和放大器的选择要考虑到输出信号中心频率、带宽变化的影响。在本方案中对输入的频率较低的时钟信号通过内置的PLL进行倍频,考虑到不同倍频次数和环路参数对最终输出相位噪声的影响,需要特别注意外接环路滤波器的设计,在印制板设计时对外接的电容和电阻按照并联和串联方式多布置几个封装位置以便于调整环路参数、优化输出信号的相位噪声。对于系统中的关键信号按照高速信号设计规则进行布线,以保证信号的完整性。对于输出Balun和放大器采用频响满足AD9910最大Nyquist带宽的型号,而对于滤波器则选用标准封装的成品滤波器,当输出信号中心频率和带宽变化时,直接更换即可。

图2 系统框图

3.2 软件设计

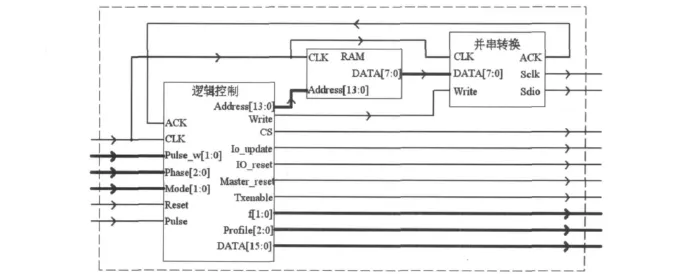

软件的设计涉及三个方面,一是波形和配置数据的产生,二个是根据外部输入信号的变化对AD9910进行动态配置;三是配置完成以后的运行控制。本方案中,波形和配置数据利用MATLAB工具以参数化的方法产生Quartus软件能够直接使用的mif格式的数据文件,当信号参数改变时,只要在MATLAB中对参数进行修改生成新的数据文件来代替旧的数据文件就可以完成新参数信号的产生。动态配置的问题可以采用多层次状态机[1]来解决。配置完成后的控制运行要依据雷达工作的特点,以Prf脉冲的前沿作为触发,根据脉宽等参数的变化来改变Profile0~2信号,从而使AD9910输出一定参数的复杂信号。图3为FPGA内部的框图,主要由三部分组成:逻辑控制模块、RAM和并串转换模块,逻辑控制模块负责整个系统的逻辑产生包括对RAM的读控制、并串转换模块的启动和与AD9910连接的信号的逻辑控制。在FPGA设计时要保证关键信号的建立时间和保持时间满足AD9910数据手册的要求。

图3 FPGA内部框图

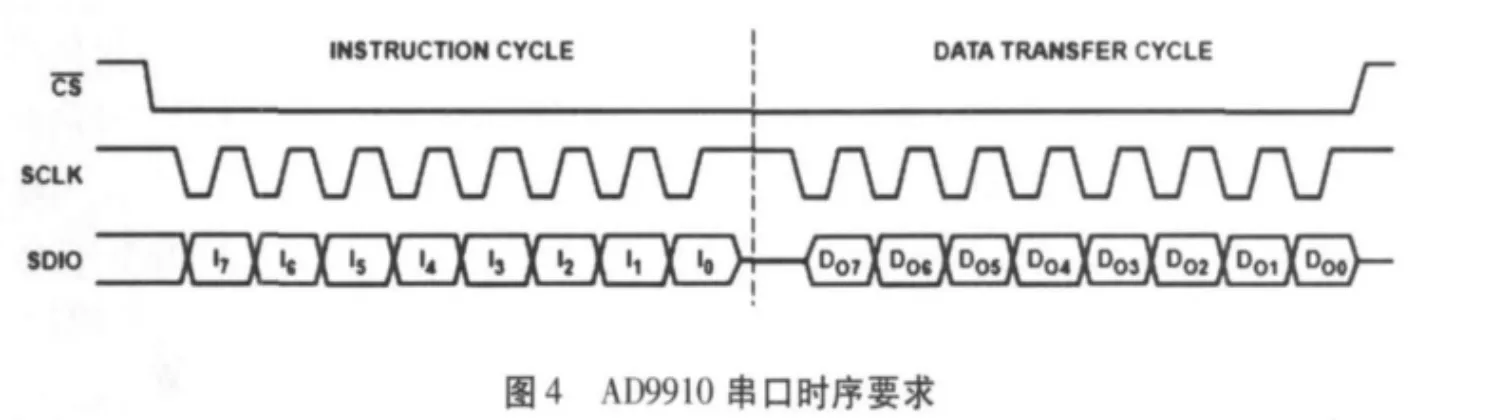

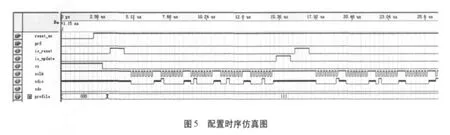

图4为AD9910串口配置的时序要求。串口的操作要在CS信号为低电平的情况下先写入一个命令字节,通过命令字节指明是进行读操作还是写操作,同时指明操作寄存器的地址。接下来的字节是数据字节也就是写入寄存器的数据或者从寄存器中读出的数据。图5是用Quartus软件进行FPGA设计,仿真出的时序图。从仿真图可以看出,在进行串口写操作前先在io-reset端口形成一个脉冲来进行串口的同步操作,在写完一个寄存器后在io-update端口上形成一个脉冲使写入的数据从缓存区转移到寄存器中,从而完成一个寄存器的写操作。

4 测试结果

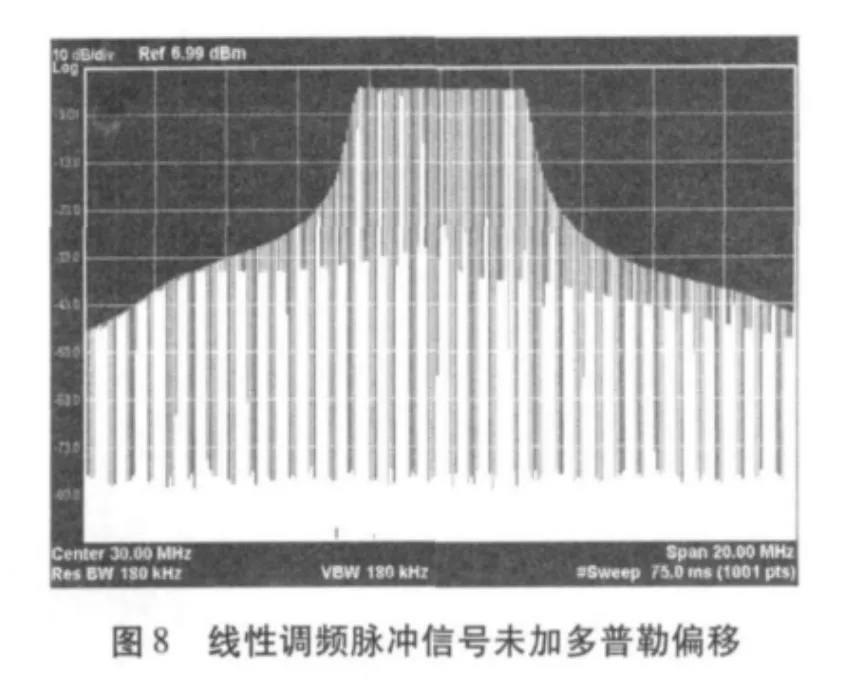

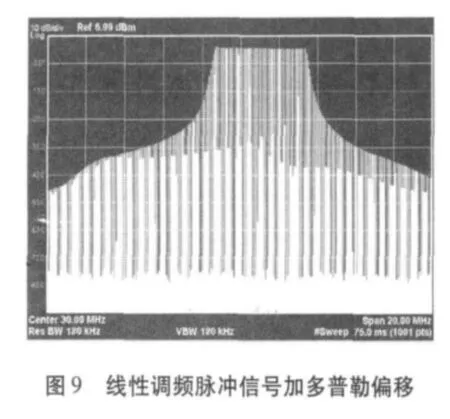

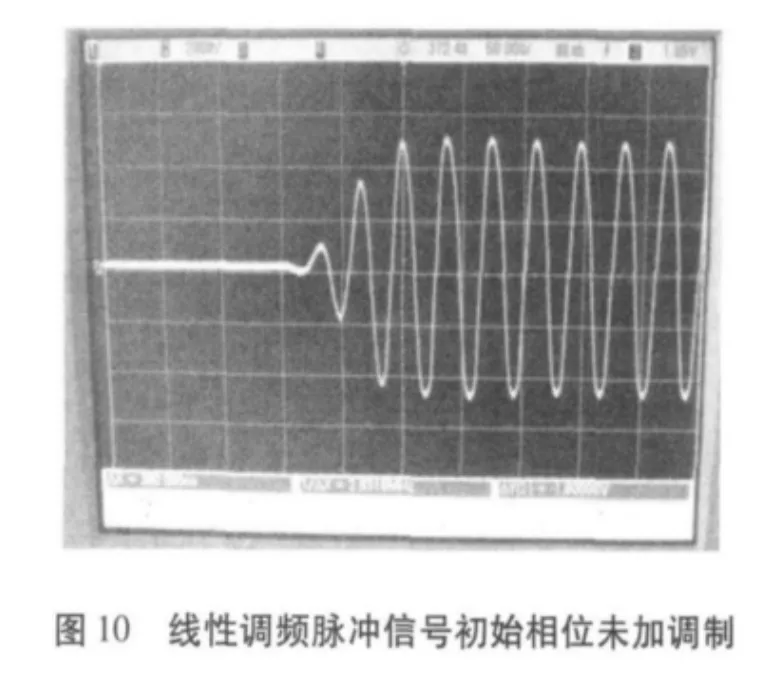

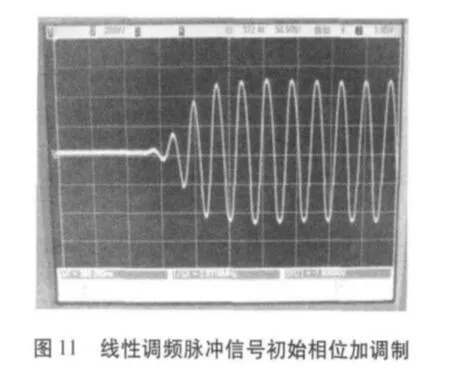

图6~9是测试不同模式下的信号频谱图,图10~11是测试不同初始相位情况下的信号时域图。其中,图6为脉内跳频的线性调频脉冲信号的频谱图,图8为线性调频脉冲信号的频谱图,图7和图9分别为图6和图8对应信号加多普勒偏移后的信号频谱图,为了便于观测,将多普勒频率设置为1MHz。

图6 脉内跳频线性调频信号未加多普勒偏移

5 结束语

本文根据AD9910的性能特点,通过FPGA对其进行动态配置形成通用雷达信号产生器。对实现该方案应注意的问题和解决方法进行了具体的介绍。最后利用频谱仪测试了输出信号的频谱,利用示波器测试了线性调频脉冲信号的时域图,符合设计要求。需要指出的是:由于受AD9910最高参考时钟频率以及其内部集成RAM容量的限制,该方案在产生大时宽、大带宽的线性调频脉冲信号或非线性调频脉冲信号时受到了限制。

[1]李辉.基于AD9954的多模式雷达信号产生器[J].火控雷达技术,2008,(4).

[2]AD9910 DATA SHEET.Analog Devices,Inc.2007.

[3]夏宇闻.VERILOG数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[4]田广锟,范如东.高速电路PCB设计与EMC技术分析[M].北京:电子工业出版社,2008.