基于CPLD的PIC32单片机大容量存储系统设计

2011-06-07杨晓明李永红晋玉剑王恩怀

杨晓明,李永红,晋玉剑,王恩怀

(中北大学 信息与通信工程学院,山西 太原 030051)

0 引言

美国微芯(Microchip)公司推出的32位单片机PIC32具有256~512 kbyte的闪存和64~128 kbyte的SRAM存储器。由于其端口数目、内部定时器和中断源数目有限,单独使用PIC32作为存储系统的主控部分,会占用较多芯片资源,所以要实现大容量数据实时存储的目的,就需要进行Flash存储扩展。系统选用CPLD作为Flash存储扩展部分的控制核心,利用CPLD控制电路时序逻辑,并由单片机发出读、写及擦除指令,这样不仅可以使单片机和CPLD的功能得到充分发挥,还可以提高系统的稳定性以及整体性能并简化系统设计。试验结果表明,基于CPLD设计的PIC32单片机大容量存储扩展系统可以实现数据实时、准确的存储,具有传输速度快、使用方便的特点,在数据存储、采集、传输等领域具有广泛的应用前景。

1 总体设计思路

1.1 系统组成

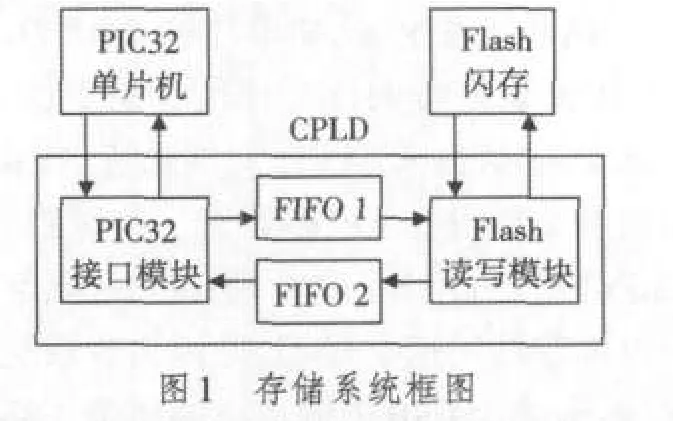

存储系统由PIC32单片机、CPLD芯片和Flash闪存3部分组成。系统所要实现的功能是:数据采集部分将实时得到的数据信号传输到PIC32单片机,单片机向CPLD发出数据存储命令、地址和数据,再由CPLD控制将地址、数据实时存储于Flash闪存中。试验结束后,单片机发出读取指令,再经由CPLD控制部分从Flash中将数据读出并传输到单片机,通过计算机串口上传至计算机作进一步的分析处理。图1所示为系统组成框图。

CPLD内部采用模块化设计原则,分别建立PIC32接口模块、FIFO模块和Flash读写模块。FIFO由CPLD片内配置编写,这样既可以最大化地利用CPLD内部资源以实现系统微型化,又可以节省使用外部FIFO芯片的成本。CPLD选用Altera公司MAXII器件系列中的EPM240T100C5芯片,MAXII系列是一种非易失性、即用性可编程逻辑系列,具有CPLD中单个I/O管脚最低成本及最小功耗。Flash存储器选用三星公司的K9K8G08U0A。

1.2 闪存K9K8G08U0A介绍

Flash存储器具有非易失性、体积小、重量轻、抗震动、低功耗、高性能等特点[1]。目前,Flash的生产厂商主要有三星,Hynix,Micron,ST,东芝等[2]。本文选用的是三星公司的K9K8G08U0A芯片,它采用2.7~3.6 V供电,容量为1 Gbyte,硬件接口比较简单,命令、数据和地址经统一的I/O端口传输,可在25 ns内读出其数据寄存器中的单字节数据。图2为K9K8G08U0A阵列组织,存储区被分为8 192个相对独立的块,每块分为64页,每页2 112 byte,CPLD通过列地址和行地址对每一个字节进行访问。K9K8G08U0A内有一个1页(容量2 112 byte)的数据寄存器,向Flash写入数据先是向数据寄存器写入。K9K8G08U0A页编程(写)操作流程为:首先写入命令80H和地址,再写入数据,页编程结束需确认10H命令后再将寄存器中的数据写入存储区,待完成写入后,需读取寄存器以判断写入操作是否成功。若写入失败则为坏块。读操作流程:先写入命令00H以及要读取页的地址,再写命令30H,将行地址所指定的页中的数据传输至数据寄存器,进行ECC校验,校验成功后,则在写信号作用下从指定的列地址开始读至此页末尾,否则进行错误检查[3]。

2 硬件接口设计

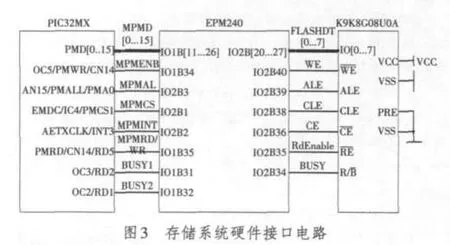

存储控制系统硬件接口设计如图3所示。

各管脚功能如下:

1)MPMD[0...15]为数据、地址、命令输入输出总线;

2)MPMRD/WR为读写信号,读写选通合并为一根控制线;

3)MPMENB为读写控制线,负责决定何时执行读/写操作;

4)MPMAL为地址锁存使能,负责锁存数据的地址;

5)MPMCS为片选信号线,高电平有效;

6)MPMINT为外部中断源控制,在允许中断的情况下,将在每完成一个读或写周期时产生中断;

7)BUSY1和BUSY2为设备运行“忙”状态指示,在进行任何读或写操作时,除了操作的最后一个周期,BUSY位都被置高;

8)FLASHDT[0...15]为数据、地址和命令复用的8位输入输出总线;

9)WE为写使能信号,将命令、地址、数据锁存到芯片内部;

10)ALE为地址锁存使能信号,用于控制外部地址锁存到芯片内部;

11)CLE为命令锁存使能信号,用于控制外部命令锁存到芯片内部;

12)CE为片选信号,若没有检测到CE信号,则芯片保持待机模式;

13)RdEnable为读使能信号,允许输出数据至缓冲器,下降沿有效;

14)BUSY指示芯片工作状态,如果芯片忙,则信号变低。

3 存储系统仿真分析

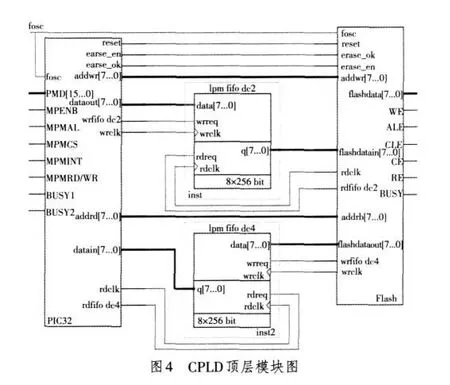

CPLD程序在QuartusII 9.0软件环境下调试,使用VHDL语言编写(由于篇幅限制,本文不给出程序部分,想参考程序者可向作者索取)。图4所示为QuartusII 9.0编程的顶层模块图。fosc为系统时钟,由片外时钟产生电路提供,频率为40 MHz,负责提供系统所需的时钟发生信号;reset为重置信号;earse_en为擦写使能信号,负责使能Flash的擦写功能;earse_ok为擦写完成信号;ad⁃dwr负责向Flash写入地址,只有写入地址成功后数据写入才有效。

1)写操作过程。PIC32单片机在接收到测试数据后,先通过wrfifo dc2向lpm fifo dc2发出写地址信号,此写地址信号由rdfifo dc2传输至Flash,写入的地址信息由addwr传输。待地址写入完成后,单片机再向fifo dc2发送写数据命令,Flash收到命令后,数据由dataout输出并在flashdatain口写入Flash。

2)读操作过程。PIC32单片机在发出读取地址命令后,经所要读取的地址由addrd传输给Flash,具体地址上的数据在发出读取命令后,由flashdataout口输出并在da⁃tain输入单片机。

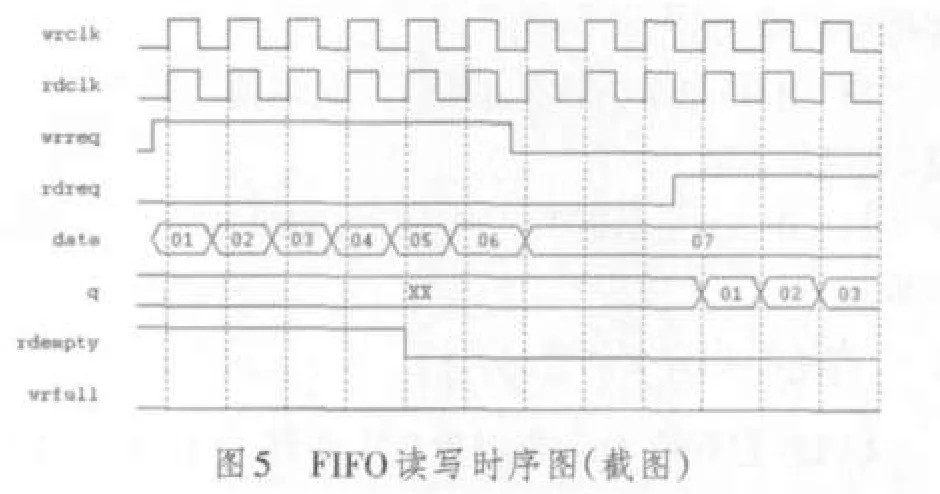

在这里要注意,对FIFO的读写是在发出读写信号wrreq和rdreq后由时钟信号wrclk和rdclk控制,并严格按照lpm fifo的读写时序进行,图5为FIFO读写时序图。

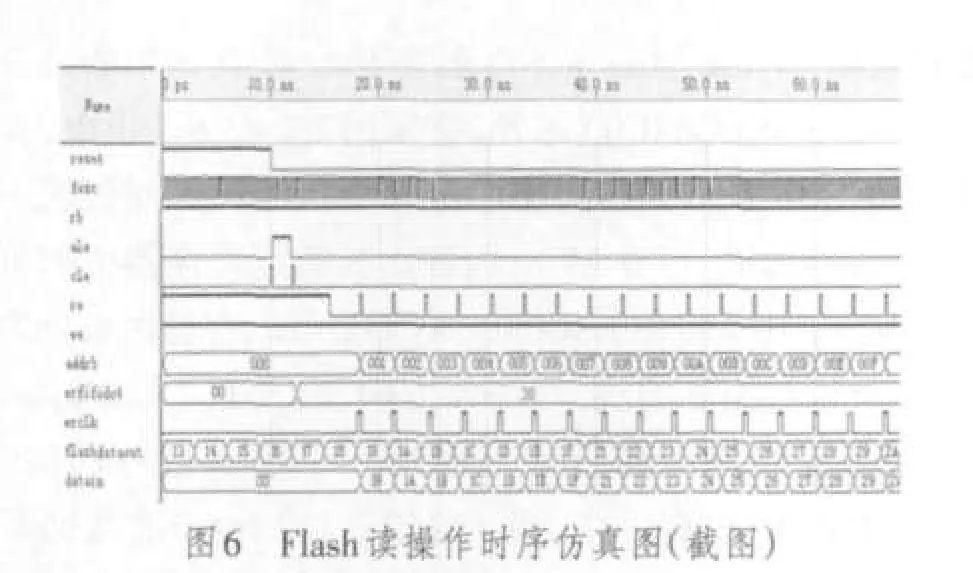

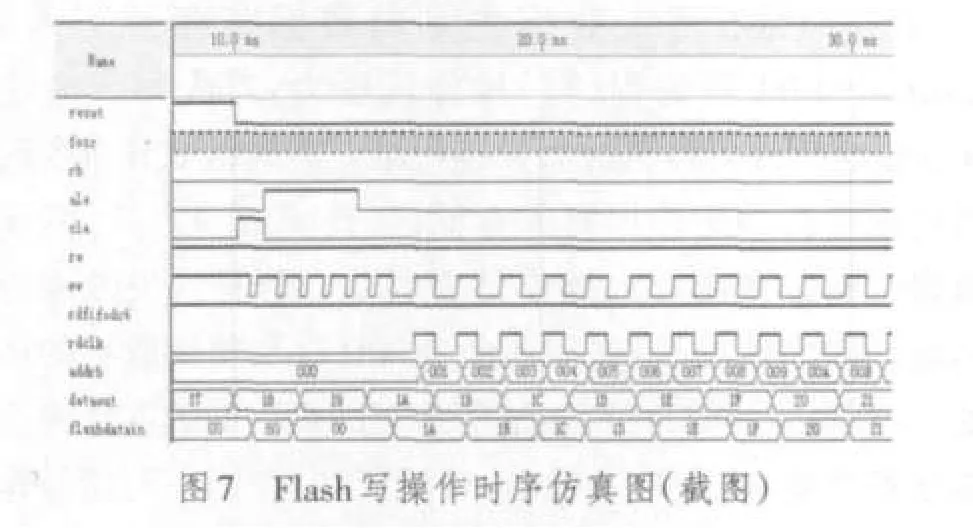

由QuartusII 9.0软件进行仿真,得到Flash的读、写操作时序波形图,如图6和图7所示。将得到的时序波形图与三星公司K9K8G08U0A数据手册上读写时序图对照,可以看到读写仿真波形满足设计要求,可以实现读、写逻辑功能,系统设计方案切实可行。

4 小结

本文介绍了基于CPLD的PIC32单片机大容量存储系统的设计方法,详细阐述了CPLD模块化系统设计方案,通过得到的读写时序仿真图验证了系统设计的正确性与可行性。该系统在实践中成功应用在某项目的系统测试适配器设计中,并成功实现数据的存储与读取。试验结果证明,合理应用CPLD技术和Flash大容量存储器,可以大大提高系统设计的灵活性与可靠性,并很好解决大容量测量数据存储容量的问题。

[1]郑文静,李明强,舒继武.Flash存储技术[J].计算机研究与发展,2010(4):716-726.

[2]钟颐华,王兴东,余松煜.基于NAND Flash的超高速视频存储技术研究[J].电视技术,2007,31(7):33-36.

[3]于文峰.大容量存储器K9K8G08U0A在海洋内波测量系统中的应用[J].水雷战与舰船防护,2009(4):26-29.