基于ARM9+FPGA方案的电视拼接墙主控系统设计

2011-06-06刘晓春胡东平

刘晓春,胡东平,张 颖

(1.长安大学信息工程学院,陕西 西安 710061;2.陕西省道路交通智能检测与装备工程技术研究中心,陕西 西安 710061;3.中兴通讯西安研究所,陕西 西安 710065)

0 引言

多媒体大屏幕电视墙在信息化工程中有很广泛的应用,它广泛应用于电力系统信息管理、大型交通指挥系统监控、银行及税务系统信息发布、卫星发射中心实时监控等[1]。作为系统核心的显示单元,其电视拼接墙单元主控系统(没有特别说明,下文中的主控系统指电视拼接墙单元主控系统)显得特别重要,不但需要实现单元系统的高清视频信号的处理,还需要控制与管理单元子系统的工作,以及单元子系统与集成大系统之间的协调与控制。本文针对上述问题研究了一种超高分辨力大屏幕数字电视拼接墙单元主控系统的设计方案,详细论述了系统硬件平台的设计与实现,嵌入式系统软件技术方案,以及基于FPGA技术的视频信号处理的设计与实现。

1 系统总体架构的研究

系统整机结构采用“背板+业务单板”的设计方案,增强系统业务配置的灵活性。电路与信号系统的结构如图1所示,多路不同标准的视频信号通过业务单板进行诸如视频缩放、视频叠加、视频格式转换等形式的信号处理后,通过业务背板总线传送给主控板的FPGA信号处理系统,FPGA系统将用户管理桌面信号与被显示的业务信号,进行视频图像局部补偿,γ校正等信号综合处理后,输出给光学显示系统。有必要考虑系统对不同的显示光学系统的兼容性设计,FPGA处理后的视频输出信号接口需要兼容多种标准的接口形式。其中,ARM9系统主要实现对主控FPGA配置,通过UART、TCP/IP接口实现与上位PC机通信,实现系统用户与主控系统的数据交互;通过UART实现对显示业务单板监控与管理;通过I2C接口与显示光学系统通信,实现对显示机芯系统的控制、监控。电源系统将对AC输入100~240 V换成5 V通过背板给系统供电,针对DLP显示则需要额外电路产生高强供电。

2 系统硬件平台设计与实现

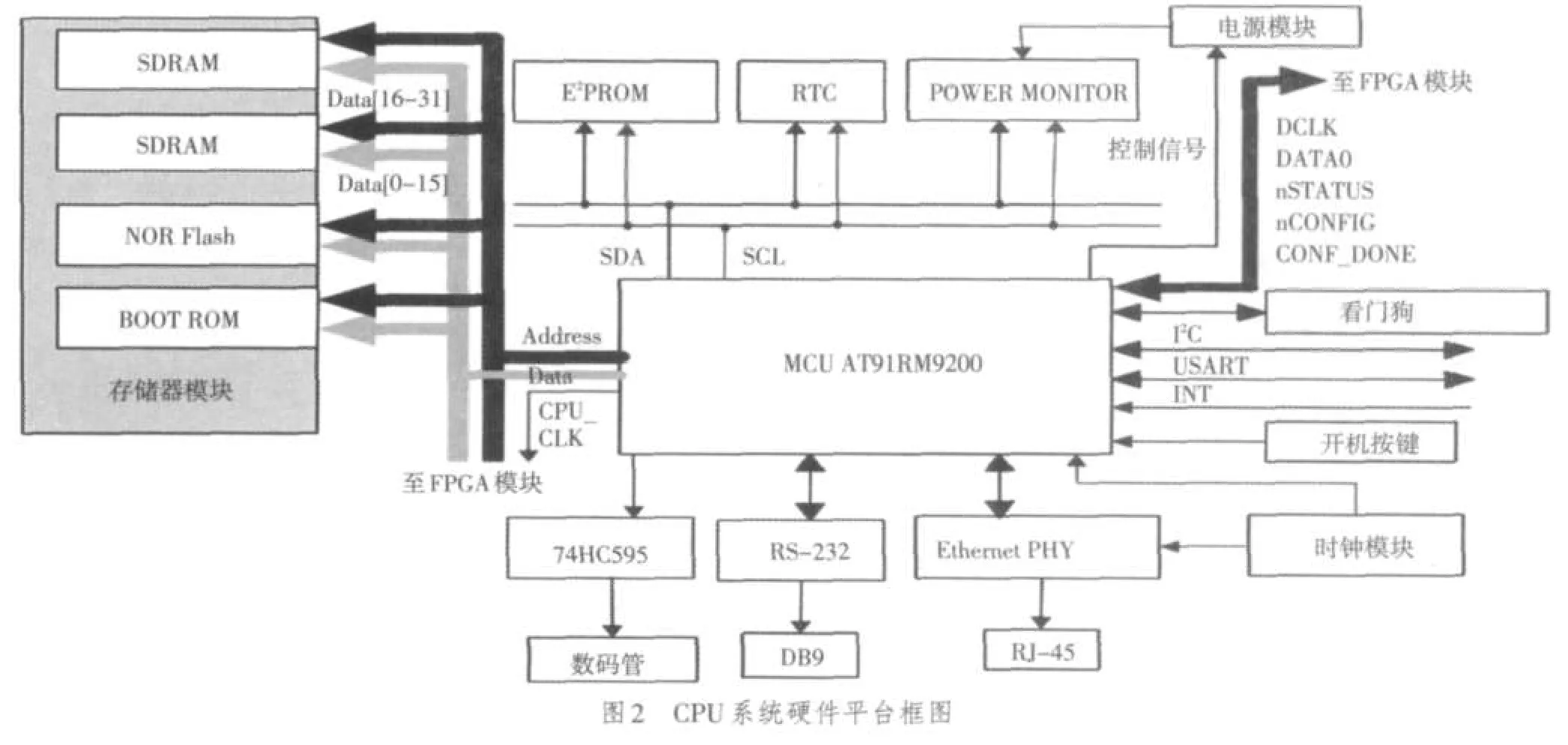

2.1 CPU小系统硬件平台

如图2所示,选用T91ARM9200作为系统主控制器,运行VxWorks操作系统,完成与上位机、下位机的通信以及系统控制和监控功能。10/100(Mbit/s)的以太网来接收上位机PC软件命令,ARM9对这些命令进行处理后发送给对应的各功能模块。ARM9通过数据地址总线与存储器、FPGA进行通信;通过内部I2C总线与E2PROM,RTC,POWER MONITOR和PLL进行通信;通过外部I2C与光学系统进行通信;通过USART与业务信号处理板进行通信,实现系统的集中管理与控制。

在T91ARM9200硬件平台运行VxWorks操作系统,有必要对存储器进行扩展。基于系统可靠性考虑,设计上将系统文件存储器与业务程序存储器分开。系统设计1片1 M×16 bit的NOR-Flash器件SST39VF1601存储BSP和最小系统程序;设计1片8 M×16 bit的Nand-FLosH器件S29GL128存储业务软件和FPGA程序[2]。设计2片16 M×16 bit的SDRAM器件EM63A165TS-8G扩展为16 M×32 bit模式作为程序运行中的缓存单位。

系统通过内部I2C总线管理RTC专用时钟芯片PCF8563TS来实现对系统时钟的管理,通过I2C总线管理电源监控芯片POWR1014A进行监控。预留一个RS-232的串行接口用于调试。为增强系统设计的可靠性,采用硬件看门狗监控ARM运行状态,此外系统设置开机键,LED数码管显示,系统从开机状态到工作正常状态,乃至机器故障状态等系统状态。

2.2 FPGA系统硬件平台

FPGA器件选型考虑:选用Altera公司推出的Cy⁃clone III系列EP3C16F484C6N,封装为FBGA-484。逻辑单元数达到15 000个,56个存储器模块,存储器总数量0.5 Mbit,56 MHz的乘法器,全局时钟总数量达到20个,I/O引脚数多达346个,支持高速外部存储接口[3]。

一路从显示业务处理板输入的RGB信号,通过背板输入FPGA。一路从外部DVI-D接口输入的桌面信号通过解码芯片SiI7171进行格式转换(TMDS/iT⁃MDS-RGB)和均衡处理,输出RGB信号至FPGA。两路RGB信号经过FPGA处理后输出到编码芯片SiI7170进行格式转换(RGB-TMDS/iTMDS)后,通过输出接口输出至光学引擎进行图像显示。其同步时钟可以是由内部输入的像素时钟产生,也可以是由外部提供。

基于系统与其他系统进行大系统集成时,各个子系统的显示图像的同步考虑,FPGA信号处理模块还需提供行、场同步时钟信号和像素时钟信号,确保各图像信号的时序保持一致。同时FPGA还需要输出开窗控制信号给显示业务板,SCI同步信号给机芯控制板。

FPGA图像处理模块除了要将外部输入的图像信号输出至光学引擎显示,还要根据不同机芯输出不同分辨率的信号,在没有外部图像输入信号时还要能输出至少10种内置测试图,以及OSD选单,用户大系统集中的安装与调试与故障诊断显示画面。FPGA模块选用2 Gbit的NAND Flash S29GL128P存储内置测试图,通过CPU控制进行加载,选用DDRⅡSDRAM进行内置测试图和OSD菜单的缓存。

此外,FPGA还必须具有中断管理功能,对于系统中各芯片的中断请求,均由FPGA统一处理后向CPU发出中断请求,CPU进入中断子程序后,读取FPGA中的中断寄存器,从而确定是哪个芯片发出中断请求信号,增强系统设计可靠性与灵活性。FPGA系统硬件平台框图如图3所示。

3 FPGA视频信号处理

FPGA采用类似于掩膜编程门阵列的通用结构,具有很高的集成度、很强的逻辑实现能力、很好的设计灵活性[4]。本系统中FPGA逻辑资源主要实现图4所示的逻辑功能。即显示视频信号必须经过FPGA进行各种显示增强,视频混合与图像覆盖,格式转换等视频信号处理,上述功能的实现从研发成本与产品化速度方面综合权衡的话,可以考虑使用商业用途的IP Core实现。

其次,DDRⅡ控制器的设计质量会对系统视频图像的处理性能产生重大影响。本方案主要从带宽需求和时序控制方面予以重点考虑。主控板的DDRⅡ接口时钟为165 MHz,数据宽度设计为64位。确保DDRⅡ访问效率为80%以上,则DDRⅡ带宽为165 MHz×2×64 bit×80%=16 896 Mbit/s,笔者通过实验已经证明可以满足性能要求。如果DDRⅡ访问效率不足80%,带宽无法满足最大需求,则无法支持1 920×1 200@60 Hz的输出图像格式。DDRⅡ控制器及DDRⅡ接口FIFO的读/写控制模块均工作在165 MHz。为了达到比较严格的时序要求,设计DDRⅡ控制器及DDRⅡ接口FIFO的读/写控制模块时应该做到如下的要求:1)控制逻辑尽可能简单,避免出现复杂的组合逻辑。2)模块的输出应使用寄存器输出。3)在进行系统集成之前,模块设计人员应确保本模块满足时序要求。

最后需要注意FPGA中寄存器的地址分配问题,CPU分配给FPGA寄存器可用地址为0x5xxx0000~0x5xxx03FF,其中0x5xxx0000~0x5xxx00FF为FPGA内置寄存器,0x5xxx0100~0x5xxx03FF为γ修正数据段,其中0x5为片选信号,表示FPGA被选中。FPGA与CPU交互的可用地址范围为0x000~0x2FF,位宽16 bit。需要注意γ修正数据的地址分配。

图4 FPGA逻辑功能框图

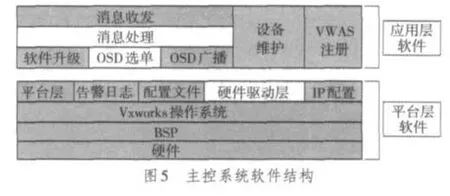

4 嵌入式软件结构

如图5所示,主控系统的软件采用如图4所示的结构。主要完成了VWAS消息收发,消息处理,OSD选单,设备维护,告警日志,软件升级,DHCP动态IP配置,参数采集与调整,文件压缩与解压等功能。

其中,平台层主要提供以太网通信,任务间通信的消息邮箱,跟踪功能和定时器。配置文件提供文本方式的INI文件配置方式。IP配置,提供TCP/IP网络上的IP动态配置。告警日志,提供告警上传,本地记录和记录查询功能。软件升级,提供软件升级功能。硬件驱动层提供对各单板上硬件的驱动,包括各种参数的采集和调整,例如版本号、温度、亮度等。VWAS注册即通知VWAS自身的IP地址和在线状态。消息处理对外部控制软件发送的消息进行处理,并分发命令到下属模块。设备维护通过参数的采集,对设备进行维护。OSD选单对红外遥控器发送的消息进行界面显示,并分发消息到消息处理模块和广播消息模块。OSD广播模块负责对OSD控制命令的广播和接收。

5 小结

系统方案的设计是电子信息产品研发与制造、产品与市场成功的关键环节。系统方案的优劣不仅表现在技术实现的难易程度上,还会影响到系统的性能指标、可靠性要求、研发与制造成本,以及从研发到产品化的速度等诸多因素。本文所设计的基于ARM9+FPGA的高清电视墙的主控系统方案,从系统整体需求出发,将性能指标、可靠性、研发与制造成本等诸多因素,进行了充分考虑,综合权衡。实践证明该方案具有很好的可行性能,已经成功进行了产品化。

[1]查理.大屏幕电视墙视频缓冲放大器设计[J].通信与广播电视,2003(3):37.

[2] 刘晓春,胡东平,简毅彬.基于多模组3G视频传输终端的硬件设计与仿真 [J].电视技术,2011,35(11):62.

[3] 吴继华,王城.Altera FPGA/CPLD设计[M].北京:人民邮电出版社,2005.

[4] 武玉华,周威,李艳俊,等.电视墙控制系统的FPGA设计[J].现代电子技术,2007(6):53.