基于DSP的SVC高速数据采集系统设计

2011-06-05程增艳朱秀林

程增艳,朱秀林,王 军

(中船重工七二二研究所 湖北 武汉 430079)

随着现代工业的发展,变流装置的应用越来越普遍,这些装置的运行,会造成系统功率因数低、电压波形严重畸变等问题,直接影响电网供电质量和其它用电设备的运行安全。静止无功补偿器(SVC)可以就地提供动态无功补偿,是解决这些问题经济有效的办法。数据采集处理是无功补偿的关键步骤,它需要采集电力系统中电压、电流等物理量,由数据处理程序根据这些物理量计算出控制所需的信号,由控制算法软件计算出控制信号,并将TSC的投切指令输出给TSC的触发执行单元,所以,SVC数据采集系统上除了控制芯片和足够的存储器外还要具备足够的A/D输入、开关量输出通道等外围电路[1]。

DSP芯片以其简单方便的外部接口连接,高速、精确、稳定的数据处理功能,集成方便等特点,越来越多的应用于自动控制,仪器仪表,通信等高科技领域。文中设计的基于DSP的SVC数据采集系统,具有采集时间快、转换精度高、控制方法简单、硬件电路少、运行安全可靠等特点[2]。

1 DSP数据采集系统组成结构

数据采集系统主要由隔离放大器电路、A/D模拟信号采样电路、CPLD逻辑电路、DSP处理器电路等组成,组成框图如图1所示。

图1 基于DSP的数据采集系统组成框图Fig.1 System block diagram for data acquisition based on DSP

电力系统实时的三相电压、电流信号,经过电流和电压互感器电路后,通过隔离放大器隔离送到放大器,然后接入A/D模拟信号采样电路中。此时DSP处理器发出控制信号,通过CPLD来控制A/D转换器进行模/数转换,并在转换结束后,把转换的结果送到DSP中。DSP会根据当前的电压、电流数据计算出系统有功、无功情况并发出控制命令,调节系统无功。DSP通过CAN总线、网口、串口与上位机或其它控制系统设备进行通讯。

2 系统设计

2.1 主要芯片电路简介

DSP采用TI公司的TMS320F28335,它是TMS320C28X系列的一个成员,与同系列的定点DSP相比,该器件的精度高,性能好,外设集成度高,数据以及程序存储空间大。TMS320F28335的供电方式采用内核为1.8 V,外部为3.3 V,功耗较低。主频达150 MHz(时钟周期6.67 ns),高性能的32位CPU,16位或者32位的外部存储器扩展接口,多达256 k×l6位的Flash存储器,多达34 k×l6位的SRAM存储器,1 kxl6位的 OTP ROOM,8 k×16的 Boot ROM;2通道 CAN 模块,3通道SCI模块,2个多通道缓冲串口(McBSP),1个SPI模块,1个I2C模块;12位模数转换模块,转换速度为80 ns[3-6]。

2.2 系统硬件设计

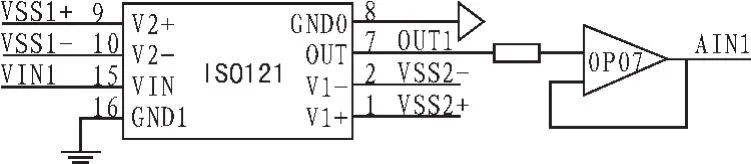

2.2.1 调理电路

电压互感器、电流互感器将一次侧强电信号变换成所需要的弱电信号,用互感器将系统的电压和电流变化为幅值为-12~+12 V的电压信号,经过前端放大电路将其变为0~3 V的单极性电压信号,然后送到如图2所示的调理电路,再输入到DSP的A/D采样通道,同时起隔离和抗干扰作用。其特点是具有较好的线性度和较小的角移。待测信号如果直接输入A/D转换器或滤波器可能会出现负载不匹配或高频串扰(A/D的采样引起)的情况,影响测量精度和稳定性,故在电路中加一级缓冲,以改善接口状况。信号的调理电路如图2所示。本采集系统设计有采集18路模拟信号,用到18片ISO121和18片OP07。

图2 调理电路Fig.2 Conditioning circuit

2.2.2 A/D转换电路

模拟/数字转换电路由3片16位高精度AD转换器组成,提供18路模拟信号输入,并且可以保证所有模拟输入信号被同步采样,减小不同通道信号被采样时造成的相位差,以提高三相不平衡度等参数测量的准确性。电路连接如图3所示。AD7656是一种16位6通道自同步模数转换器,使用了iCMOS工业制造技术,具有性价比高、精度高、能耗低、转换速度快等优点,尤其适合于电力系统中模拟量的测量。

图3 A/D转换电路Fig.3 A/D circuit

DSP的地址、控制信号经过CPLD译码输出3片AD7656的控制信号CS、RD、RESET。此时,三相电流、电压信号已经分别输入到两片AD7656中,只要控制信号发出启动A/D转换的命令,AD7656便开始进行模/数转换,并将转换后的数据送到TMS320F28335GF的D0~D15数据总线上。AD7656的6个采样通道的数据是通过6次连续的总线读取得到,而采样频率却只能统一设置成250 kHz,为了得到10 kHz的采样数据需要对已采集得到的数据做降采样处理。采用CPU降采样数据效率非常低,会严重影响系统效率,TMS320F28335GF提供的DMA控制器使用灵活可以实现降采样数据的功能,所以本系统采用DMA的方式实现数据降采样。而由于数据量庞大,将AD采集数据存放在SDRAM中,而处理时再将数据搬运到内部RAM中,搬运时仍然使用DMA操作。另外,AD7656的参考电压电路AD780的输入端接入5 V电压同时对地并联两个滤波电容,用来滤除5 V电源中的干扰电瓶信号,通过OUT引脚输出2.5 V的参考电压,并将该电平连接到 AD7656的 VREF脚[3]。

2.2.3 通讯接口

TMS320F28335有3个异步串口,本系统只用了两个串口,选用MAX3378驱动芯片进行电平转换。MAX3378功耗低,集成度高,可用3.3 V电源供电,是一款在UART通信中使用最多的接口芯片之一。TMS320F28335的SCI有如下特点:波特率可调,最高可达64 k;数据格式由一位起始位,8~16位的数据长度,可选的奇偶校验位和一至两位停止位组成;有4个错误检测标志和两种多处理器模式即空闲线和地址位;可以工作在半双工或者全双工模式;具有双缓冲接收和发送功能,支持发送中断使能和接收中断使能,支持NRZ格式;SCI还具有自动波特率检测的硬件逻辑和16级深度的FIFO功能,能够减少空头服务,加快数据传输速度。串口电路如图4所示。

图4 串口电路Fig.4 Serial interface circuit

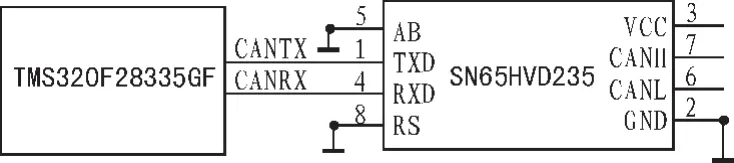

CAN总线是一种串行通信协议,具有较高的通信速率和较强的抗干扰能力,可以作为现场总线应用于电磁噪声较大的场合,CAN总线模块带有23个完全可配置邮箱,具有定时邮递功能,能够实现灵活稳定的串行通信接口。双电源供电系统应用环境电磁噪声大,选用CAN总线通信是一种很好的解决方案。本系统选用SN65HVD235为CAN总线的电平转换器件,实现不同电平节点的完全兼容。电路如图5所示。

图5 CAN总线通信接口电路Fig.5 CAN interface circuit

2.3 系统软件设计

在硬件系统搭建完成的基础上,系统的功能实现由软件系统来完成。本系统的软件设计主要由两部分组成:其一是逻辑控制部分;其二是数据采集与处理部分。逻辑控制部分是运行在CPLD上的程序,采用VHDL语言编写;数据采集与处理部分是运行在DSP上的程序,总体上采用汇编和C混合编写,即主程序和算法方面用C语言编写,运行速度要求高的接口程序代码采用汇编语言。

2.3.1 CPLD程序设计

本系统采用了一片Xilinx公司的XC95144对外部芯片和器件的控制。重点是A/D转换芯片的控制、两片SDRAM的读写、I/O扩展电路的使能和地址译码。它完全符合IEEE 1149.1 JTAG边界扫描标准,具有3.3 V ISP的功能,可通过JTAG接口实现在线编程。

本系统CPLD程序的开发是在集成开发环境ISE10.1下采用VHDL语言编写和调试,最后通过JTAG接口将程序下载到CPLD器件中。

2.3.2 DSP程序设计

主控制器TMS320F28335最先运行的程序是系统的初始化程序,主要包括:初始化系统控制,包括初始化看门狗,系统时钟的初始化,片内外设时钟的初始化;控制器内存初始化;清除所有的中断,初始化PIE向量表,禁止DSP中断等;初始化ADC模块,主要包括:AD启动、AD时钟频率的选择、采样模式的选择、采样通道的设定以及AD中断程序的设定等;初始化事件管理器,包括捕获单元的设定,通用定时器的设定,中断程序的设定;初始化外部接口寄存器[2]。

ADC模块的采样采用软件触发方式,在DSP定时器中断中启动采样,采用同步方式采样6个通道,并采用每次转换结束中断的方式来纪录采样结果,并用软件启动下一次ADC中断。

3 结束语

目前本数据采集系统已经安装在现场操作机柜中,实践证明,该数据采集系统各个通道高速数据流能够正确采集、存储,并与上位机进行通讯,运行稳定,完全满足SVC设备高速、高精度数据采集的要求。

[1]王兆安,刘进军.电力电子装置谐波抑制及无功补偿技术的进展[J].电力电子技术,1997(1):100-104.WANG Zhao-an,LIU Jin-jun.Advances ofharmonic suppression and reactive power compensation technique for power electronic equipment[J].Power Electronics Synopsis,1997(1):100-104.

[2]杨绿溪.现代数字信号处理[M].北京:科学出版社,2007.

[3]TMS320F28335/TMS320F28334/TMS320F28332 Digital Controllers Data Sheet[EB/OL]. (2007-07-21)[2011-01-16].http://www.ti.com/lit/ds/sprs439i/sprs439i.pdf.

[4]TMS320x2833x.2823xSystem Control and Interrupts Reference Guide[EB/OL].(2007-07-21)[2011-01-15].http://www.ti.com/lit/ug/sprufb0d/sprufb0d.pdf.

[5]TMS320x2833x Boot ROM Reference Guide[EB/OL].(2007-07-21)[2011-02-15].http://www.ti.com/lit/ug/spru963a/spru963a.pdf.

[6]TMS320x2833x DSC External Interface (XINTF)[EB/OL].(2007-07-21)[2011-02-15].http://www.ti.com/lit/ug/spru949d/spru949d.pdf.

[7]雷晓瑜,曹广忠.TMS320F28335及其最小应用系统设计[J].电子设计工程,2009(1):91-92.LEI Xiao-yu,CAO Guang-zhong.Design of TMS320F28335 and its minimum application system[J].Electronic Design Engineering, 2011(1):91-92.