基于FPGA的按键消抖电路设计方法的研究

2011-06-05杨晓慧

于 晶, 杨晓慧, 黄 勇

(1.长春理工大学 吉林 长春 130000;2.吉林博安消防设备有限公司 吉林 长春 130000)

通常所用的按键都为机械触点开关,由于机械触点存在弹性作用,当按下按键或松开按键时,都不可避免地要在触点闭合及断开的瞬间产生一连串的键抖动。其在按键闭合和断开时产生了多个边沿,如果不滤除抖动的话,则在读取信号的边沿,会引起按键被误读多次,这样就会导致电路的误动作。为了保证按键电路只有一次正确的响应,则按键消抖电路的使用是必不可少的。

1 按键消抖的方法分析

按键消抖一般采用硬件和软件消抖两种方法。硬件消抖是利用电路滤波的原理实现,可用RS触发器作为常用的消抖电路[1],但对于按键较多且从节省硬件资源和易于修改的角度考虑,常采用软件的方法来实现硬件电路[2]。文中利用Altera公司的可编程逻辑器件FPGA,通过VHDL语言编程实现按键消抖硬件电路的功能。采用软件延时和对按键信号进行处理的方法设计了3种性能可靠的按键消抖电路。

2 按键消抖电路的几种设计方法

一般人按键的时间大于100 ms,抖动时间一般为5~10 ms。按这种常规处理,一般认为接收到的按键信号持续时间如果小于40 ms则其为抖动信号,如果时间大于40 ms则为正确的按键信号。即让计数器的模值和计数时钟周期的乘积略大于40 ms即可。这样就可以把按下的时间小于40 ms的抖动信号滤掉[3]。文中的晶振频率采用80 MHz。

2.1 基于计数器的按键消抖电路

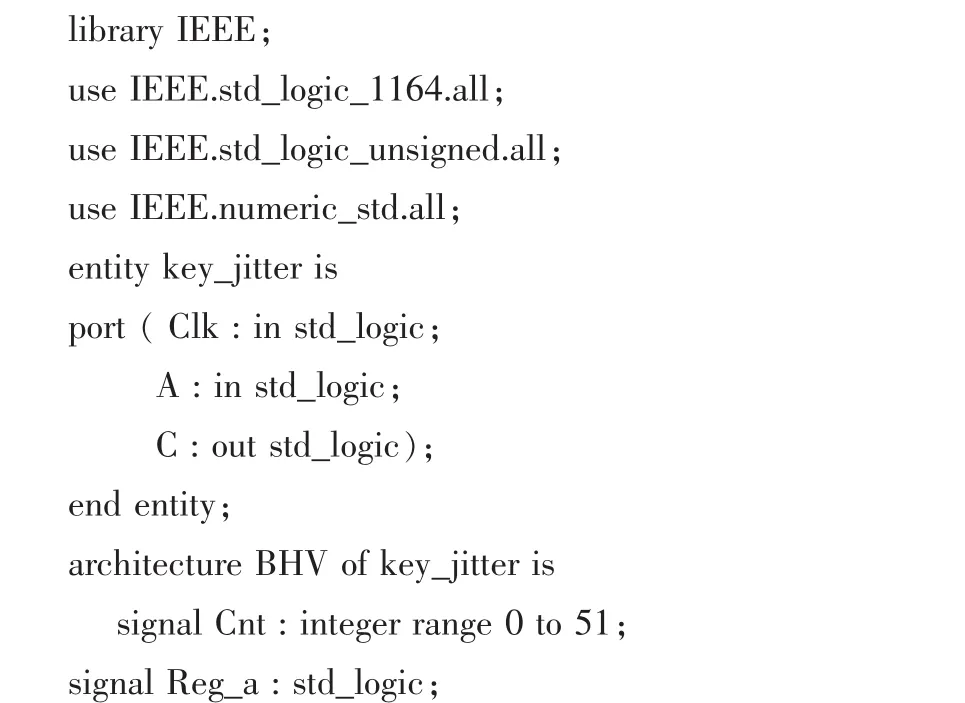

应用计数器实现,即采用延时的方法。先正确设定计数的时钟脉冲。当判断到有脉冲发生并且为上升沿时计数器开始计数,等计数器计满后将按键的状态输出。其VHDL代码如下,仿真波形如图1所示。

图1 基于计数器的按键消抖电路的仿真波形Fig.1 Simulation waveform of key-jitter circuit base on counter

2.2 基于RS触发器的按键消抖电路

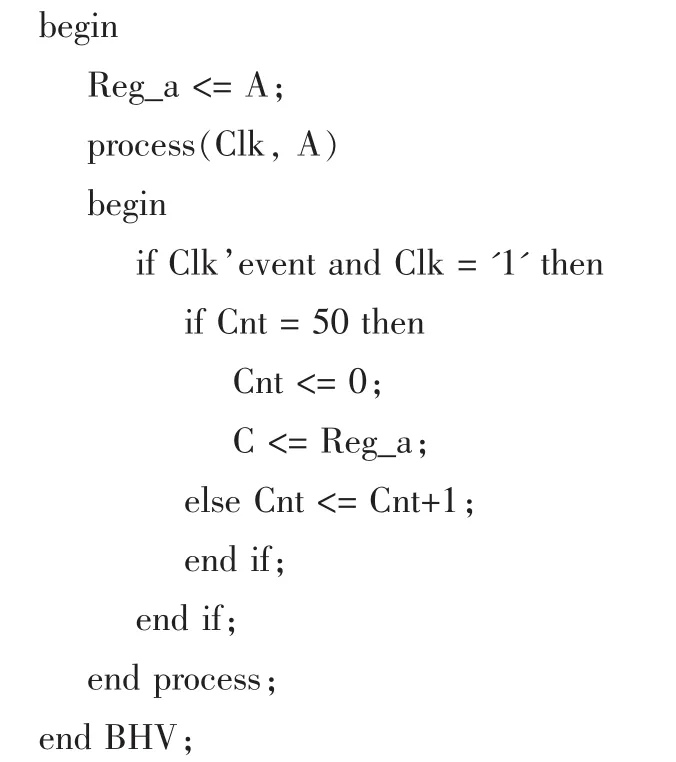

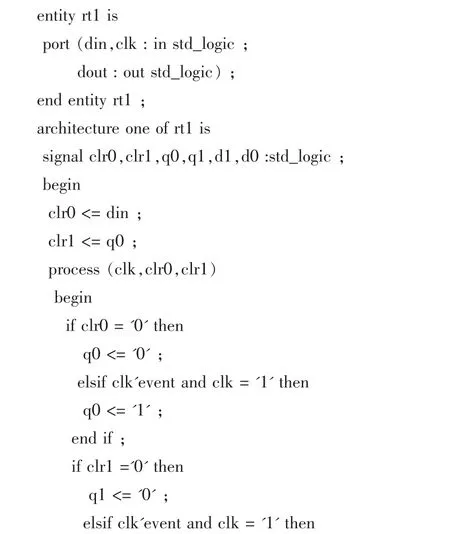

在设计中用时钟信号进行采样,对按键输入信号,当两次采样信号相同时,判定已经稳定的按下或放开了按键。触发器相应被置成0态或1态。如两次采样结果不相同,则触发器维持原输出信号不变。由于直接由触发器输出的信号时间宽度可能过长,所以在触发器后再接一级同步化电路,保证每次输出的信号只占有一个时钟周期的宽度。应用这种方法滤除抖动,关键是确定采样时钟的频率。保证两次采样的时间间隔能大于按键的抖动时间,且小于正常按键时的按键稳定闭合时间。其VHDL代码如下,仿真波形如图2所示。

图2 基于RS触发器的按键消抖电路的仿真波形Fig.2 Simulation waveform of key-jitter circuit base on RS flip-flop

2.3 基于状态机的按键消抖电路

电路的复位信号Rst_I有效时,电路[4-6]进入复位状态s0,在s0状态下时钟信号CLK以80 MHz的频率采样按键输入信号key_I,如果采样到 key_I=‘0’则停留在s0状态,并继续采样按键输入信号的状态,一旦采样到输入信号是高电平,即key_I=‘1’,则转入s1延时状态,进行消抖延时。当延时结束时,则转入s2状态,在此状态下时钟信号CLK以一定频率采样按键输入key_I的状态,如果采样到key_I为高电平,即key_I=‘1’表示经过消抖延时之后,按键仍然为按下状态,则停留在s2状态继续检测按键输入信号状态,等待按键释放,同时key_I=‘1’表示此次按键为有效按键,此时输出按键确认信号,即 key_confirm=‘1’;如果采样到 key_I为低电平即Key_in=‘0’表示按键已经释放,则转回状态s0,因为当按键释放时也会有抖动,所以当采样到输入信号为高电平,即key_I=‘1’时,再次转入s1进行消抖延时,当延时结束时,则转入s2状态判断此时按键的状态,当采样到输入信号为低电平时,回到s0状态,此时完成一次按键按下和释放的操作。其状态机的状态图和仿真波形如图3、4所示。

图3 状态机Fig.3 State machine

图4 基于状态机的按键消抖电路仿真波形Fig.4 Simulation waveform of key-jitter circuit based on state machine

为便于在仿真图中可以清晰的看出消抖延时的效果,程序中采用较短延时时间,在实际应用中,延时部分的计数值可以根据具体的时钟频率以及所需要延时的时间进行修改,VHDL程序如下:

3 结 论

仿真结果表明,以上3种按键消抖的方法都能很有效的起到消抖的作用,然而经过实际工程应用之后发现,基于有限状态机的方法最能有效的对按键进行消抖处理,并且性能稳定,确保每一次按键操作能够准确输出按键确认信号。

[1]曾旖,奚大顺,李向阳.按键开关的抖动与消除方法[J].电子世界,2005(9):55-56.ZENG Yi,XI Da-shun,LI Xiang-yang.Jitter of key switch and eliminate method[J].Electron World,2005(9):55-56.

[2]许德成.基于FPGA的按键消抖动设计[J].吉林师范大学学报:自然科学版,2009(4):154-156.XU De-cheng.Shaking release design on the keys of FPGA[J].Journal of Jilin Normal University:Natural Science Edition, 2009(4):154-156.

[3]谷长龙,李小英.基于FPGA器件的消除按键抖动方法研究[J].吉林化工学院学报,2006(3):53-55.GU Chang-long,LI Xiao-ying.Methods of eliminating the jitter of keys based on FPGA devices[J].Journal of Jilin Institure of Chemical Technology, 2006(3):53-55.

[4]侯继红.基于VHDL语言的按键消抖电路设计及仿真[J].现代电子技术,2009(23):201-205.HOU Ji-hong.Design and simulation of key-jitter elimination circuit based on VHDL[J].Modern Electron Technology,2009(23):201-205.

[5]鲁传明,瓮嘉民.基于VHDL的防抖型矩阵式键盘设计[J].河南工程学院学报:自然科学版,2009(1):58-62.LU Chuan-ming,WENG Jia-min.Design of eliminate bounce and matrix keyboard based on VHDL[J].Journal of Henan Nature of Engineer NG:Natural Science Edition,2009 (1):58-62.

[6]邢自茹,史明健.FPGA开发中按键消抖与单脉冲发生器电路[J].现代电子技术,2009(21):171-172.XING Zi-ru,SHI Ming-jian.Elimination buffeting of keystroke and single pulse generator circuit in FPGA development process[J].Modern Electron Technology,2009(21):171-172.