H.264视频解码器中帧内预测模块的硬件设计

2011-06-03王祖强

宋 健,王祖强,秦 盼

(山东大学 信息科学与工程学院,山东 济南250100)

H.264/AVC是由国际电信联盟(ITU)和国际标准化组织(ISO)共同提出的最新一代数字视频压缩标准,它吸取了以往压缩技术的精华,又引进了其他压缩技术无法比拟的许多新技术,因此,H.264在通信领域得到了广泛应用。H.264/AVC压缩效率很高,但算法的复杂度和运算量同时也大大增加,为了满足视频解码实时性的要求,寻求更有效的解码技术成为重要的研究课题。

帧内预测是视频编解码中重要的一部分,其主要功能是降低图像的空间冗余。本文根据H.264/AVC帧内预测的特点并结合对其算法的分析,提出了一种帧内预测硬件电路结构,有效地减少了硬件电路面积,提高了解码的性能。

1 H.264帧内预测算法介绍

H.264视频解码器中,对于I和SI宏块类型采用帧内预测来解码。帧内预测模块的输入是当前宏块相邻左边块和上边块环路滤波前的像素值及参考预测模式,输出是当前宏块的预测值。预测值与反变换反量化得到的残差值重构,得到宏块的像素值。完成后,当前宏块的部分像素值和预测模式要进行存储,为后面宏块解码提供参考值。

H.264中亮度预测分两类,一类是针对图像中含有大量细节的部分采用 4×4块的预测模式(有9种预测模式);另一类是对图像中比较平缓的区域采用16×16块的预测模式(有4种预测模式)。色度预测是 8×8块的预测模式,有4种预测模式,这4种预测模式与亮度16×16的预测模式相似,也有竖直、水平、DC和平面模式。所有的预测模式都是根据左边块和上边块的参考值,计算当前宏块的预测值。

2 硬件实现

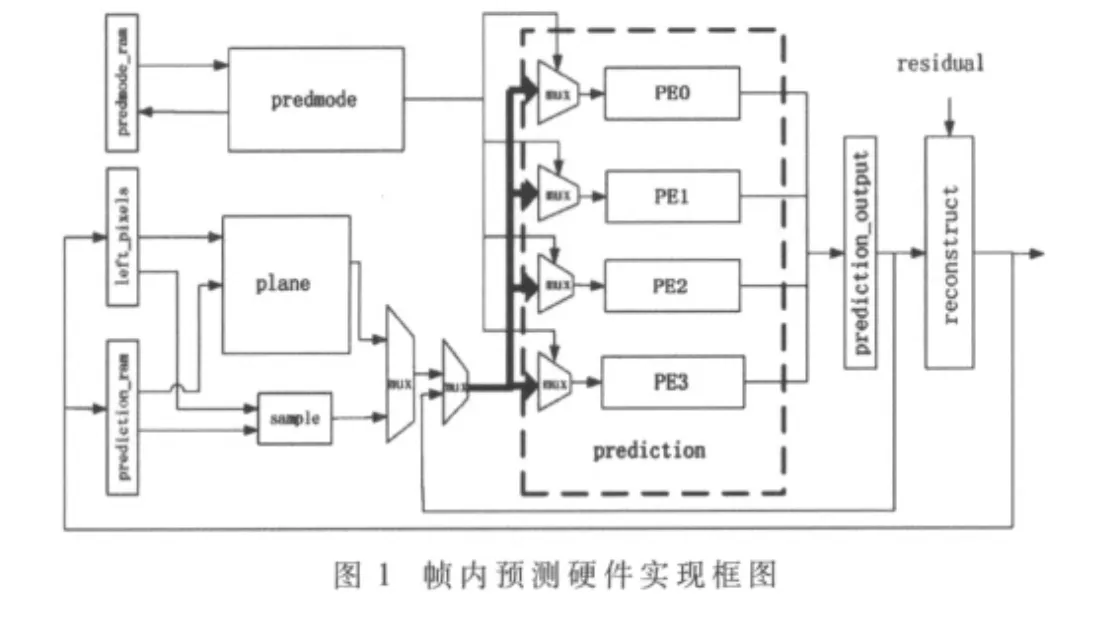

根据帧内预测算法,硬件结构划分为predmode模块、plane模块、prediction 模块、reconstruct模块、left_pixels模块、predmode_ram、prediction_ram、sample和 prediction_output模块。如图1所示,其中 left_pixels、prediction_ram、predmode_ram、sample和 prediction_output模块都是存储单元,分别存储的是当前宏块左边块的参考值、当前宏块上边块参考值、当前宏块上边块的参考预测模式、提取的参考像素值和当前宏块预测值输出;predmode模块预测计算出当前块的预测模式;plane模块是对plane预测模式的预处理;prediction模块是帧内预测的核心计算单元,4个PE单元并行运算,一个时钟周期解码出一个4×4的一列 4个预测值;reconstruct模块的功能是实现重构。

2.1 predmode模块设计

Intra_16×16和Intra_Chroma的预测模式可通过语法元素解析直接获得,所以本模块的主要任务是解析Intra_4×4的预测模式。

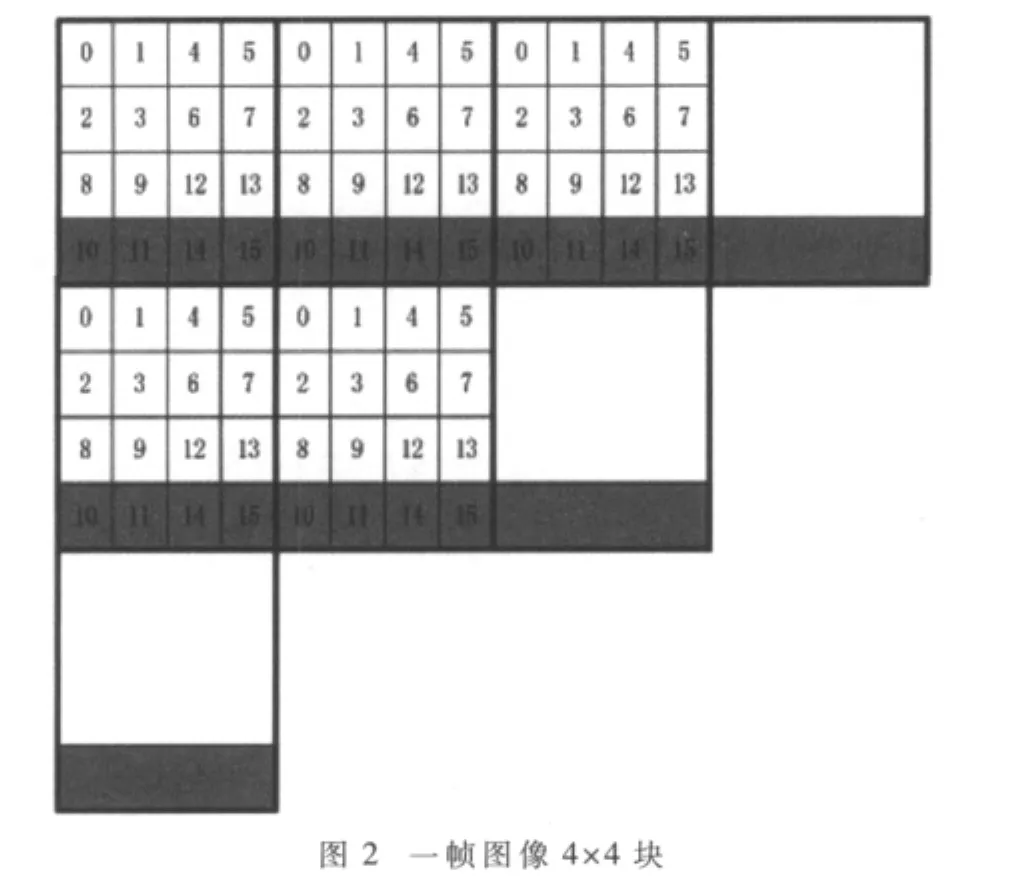

本模式预测器的输入是当前 4×4亮度块的luma_4×4BlkIdx(块索引)、解析的语法元素和当前宏块的信息。输出是当前宏块的16个子块的预测模式mb_predmode。predmode_ram中存储的是当前宏块上边一行4×4块的预测模式,如图2阴影部分所示。左边块的预测模式存储在predmode模块内。对于高清图像(分辨率为1 920×1 080)来说,predmode_ram需要的存储空间为1 080 bit。

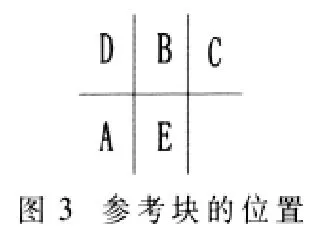

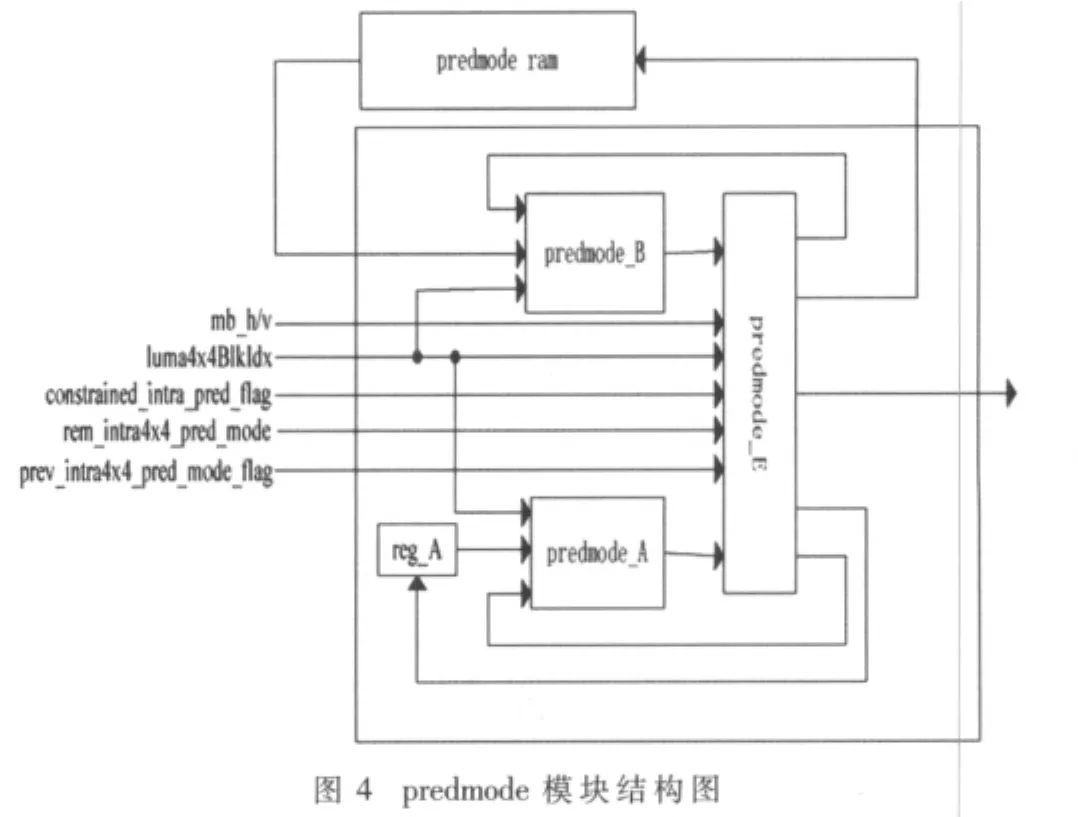

如图3所示,E是当前块,A是左边块,B是上边块,D是左上边块,C是右上边块。predmode模块的结构如图4所示,图中predmode_B模块的作用是获得当前宏块E的上边块B的预测模式,预测当前宏块 E的子块 0、1、4、5,需要从 predmode_ram中读取上边块的参考预测模式,其他子块的上边块参考预测模式是当前块已解码子块的预测模式。predmode_A模块的作用是获得当前宏块E的左边块A的预测模式,预测当前块 E的子块 0、2、8、10时,左边块预测模式从reg_A里读取。当宏块E的16个子块预测完成时,把5、7、13、15子块的预测模式存储到reg_A中,为下个宏块模式预测提供左边块参考值。

2.2 prediction模块设计

prediction模块是整个帧内预测的核心计算模块。prediction模块的功能是根据获得的参考像素,在不同预测模式下采用不同的预测公式计算当前块的预测值。帧内预测共有17种预测模式,通常若对每种预测模式都设计预测器,当求解一个预算值时,其他16个模式处于空闲,这就造成了很大的资源浪费。通过分析各个模式所对应的运算法则,可以发现这些运算法则的共同特点是:(1)计算每个位置预测值最多需要4个参考样本像素;(2)计算公式都可由加法和移位操作完成计算。根据各个预测模式的相似点,把17种预测模式集合到一个运算单元中,可大大节约硬件资源。

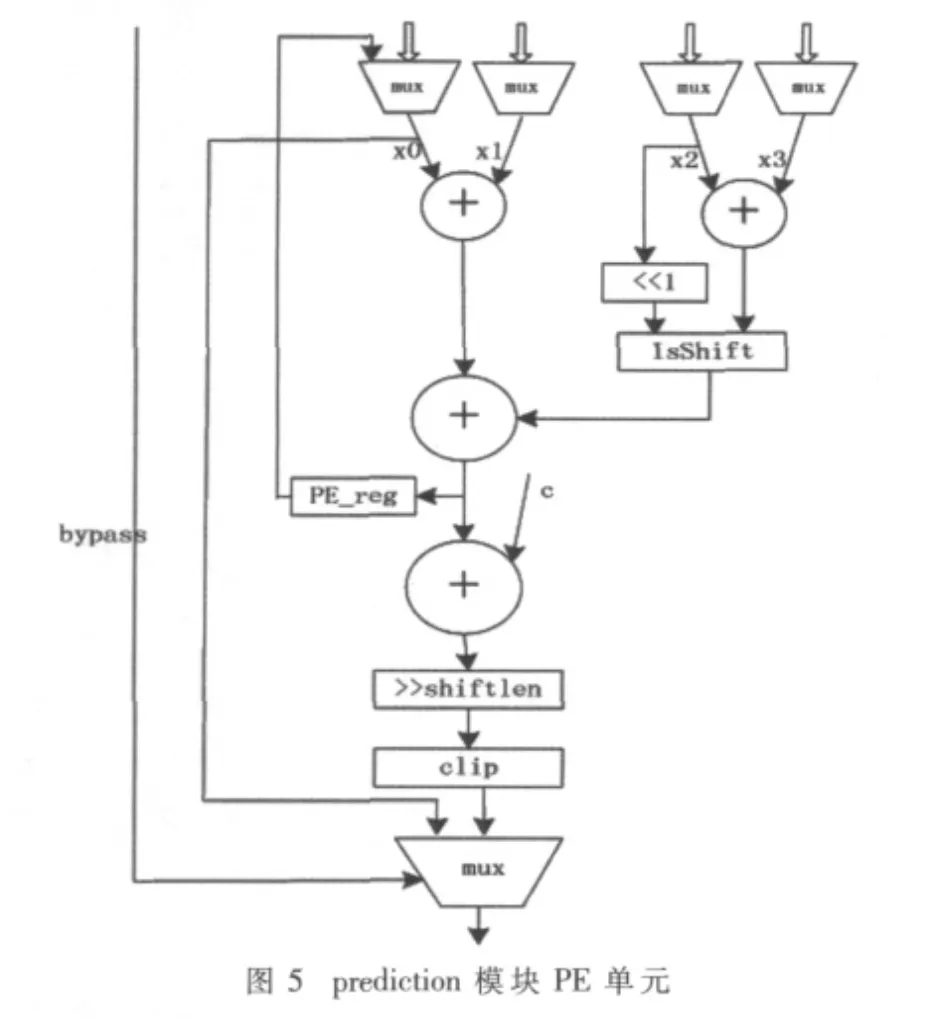

图5给出了PE的设计,该 PE的特点是:(1)Horizontal或Vertical预测模式中在获得参考值 x0后,在bypass控制下不需要经过运算单元直接获得预测值;(2)DC模式,该模式的预测值是一个平均值。对于Intra_4×4_DC模式,用 2个 PE单元(PE0和 PE1)在 1个时钟周期就可解得预测值。Intra_16x16_DC模式需要4个时钟周期,假设左边和上边的参考像素值分别命名为L0~L15和 U0~U15,前 3个时钟周期,PE0的输入分别为(L0,L1,L2,L3)、((L0+L1+L2+L3),U0,U1,U2)、((L0+L1+L2+L3+U0+U1+U2),U3,0,0), 输出存储在 PE_reg中作为下个时钟周期的输入,PE1、FE2、PE3的输入类同,最后一个时钟周期把 PE0、PE1、PE2、PE3作为 PE0的输入求出 DC模式的预测值;(3)其他预测模式,如(A+2B+C+2)>>2和 plane预处理单元的输出都能经过此运算单元完成预测值的计算。

为了提高解码速度,满足视频解码实时性的要求,采用 4个运算单元 PE0、PE1、PE2和 PE3同时运行,4个运算单元4个时钟周期可以解码出一个4×4块,提高了解码速度。

2.3 plane模块设计

2.3.1 简化 plane预测模式

Intra_16×16_Plane模式和色度块Intra_chroma_Plane模式是帧内预测中最复杂的预算模式,为了满足系统实时处理的要求,可提前预算plane模式需要的一些参数。本文以Intra_16×16_Plane为例介绍如何简化plane模式,Intra_chroma_Plane方法类同。

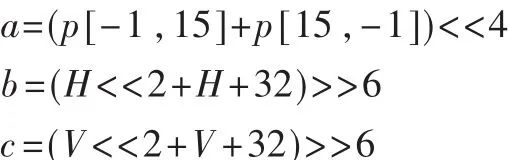

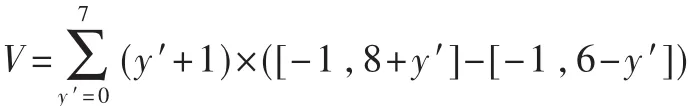

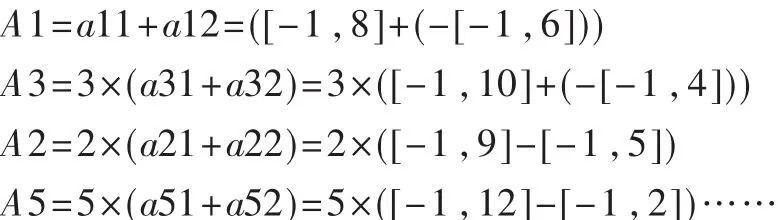

在plane模式运算中要用到乘法,为了节约硬件资源,采用移位来实现乘法,其中参数 a、b、c的计算公式为:

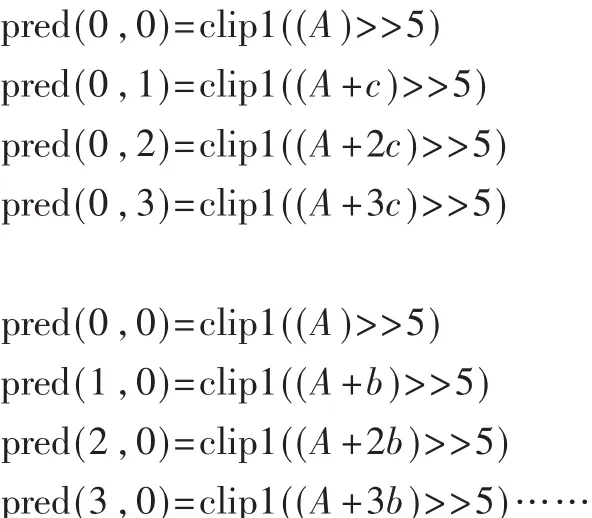

在H和 V已知的情况下,a、b、c均可求得。当设A=a+b×(-7)+c×(-7)+16,预测值为:

上述公式,首先求得 A 后,pred(0,1)、pred(0,2)、pred(0,3)的值是在 A 的基础上加上 c、2c、3c,然后再进行移位和 clip。pred(1,0)、pred(2,0)、pred(3,0)的值只是在 A的基础上加上 b、2b、3b,然后再进行移位和clip。所以提前求得A、b、c,预算值是在A的基础上加上b或者c的倍数,本方法可大大优化plane模式。

2.3.2 plane模式硬件设计

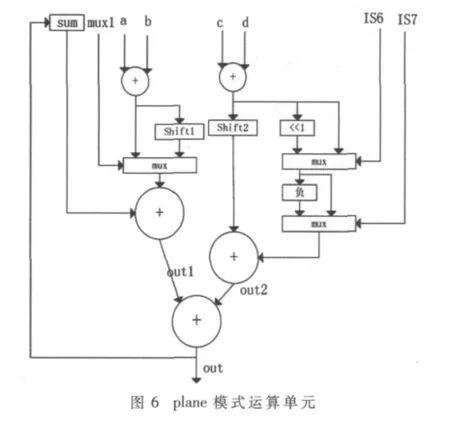

plane模式的关键是求得参数H和V,其硬件设计如图6所示。以V为例介绍本电路。

其中设:

举例说明本运算单元如何计算出参数H:

当 a=a11、b=a12、c=a3、d=a3、sum=0、mux1=0、IS6=0、IS7=0、shift1=0、shift2=1 时,就可以求得 A1+A3。 a=a21、b=a22、c=a51、d=a52、sum=0、mux1=0、IS6=0、IS7=0、shift1=1、shift2=2时,就可以求得 A2+A5,并依照这个运算单元可求出A4+A6和A8+A7。

本电路4个时钟周期就可以求得H或V,所以共需要8个时钟周期求H和V。本方法与通常方法相比,只计算一次A、b、c的值,其他位置的预测值只需要在A的基础上加上b或者c的倍数,降低了复杂度。

3 实验结果

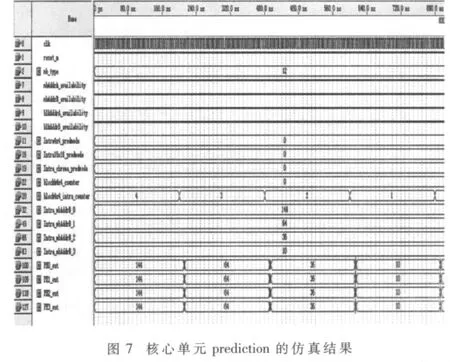

本设计使用Verilog HDL完成硬件代码的编写,并用Altera公司的Quartus II 8.0进行代码的仿真和综合。图7为核心单元prediction模块的仿真结果,PE0_out、PE1_out、PE2_out、PE3_out9为 4个并行单元的输出。 采用Altera公司的Cyclone II进行本设计FPGA验证,本设计占用的逻辑资源数量较少,节约了硬件资源。

本文根据H.264帧内预测的特点,提出了一种并行处理的硬件实现方法。该方法能够提高帧内预测的处理速度,节约了硬件资源,满足了高清视频的解码要求。

[1]ISO/IEC 14496-10.draft ITU-T recommendation and final international standard of joint video specification(ITU-T Rec.H.264/AVC)[S].2003.

[2]SAHIN E,HAMZAOGLU I.An efficient intra prediction hardware architecture for H.264 Video Decoding[M].IEEE,2009.

[3]Wang Xi.A parallel intra prediction architecture for H.264 video decoding[M].IEEE,2007.

[4]毕厚杰.新一代视频压缩编码标准-H.264/AVC(第二版).2009.