通用视频输出控制器IP核的低功耗设计

2011-05-22徐永钊范丽仙曾志峰李洪涛

徐永钊, 范丽仙, 曾志峰, 李洪涛

(东莞理工学院,广东 东莞 523808)

0 引言

作为用户获取信息以及人机交互的最佳渠道,视频输出是大多数电子设备必不可少的功能。而随着电子技术的不断发展,芯片制造工艺的不断升级,芯片的集成度越来越高,视频处理专用芯片或 SoC基本都集成了视频输出控制单元,用于直接驱动各种显示屏。例如在手持式多媒体播放器中驱动小尺寸液晶屏,在液晶电视中驱动大尺寸显示屏,或者以VESA标准通过VGA接口连接其他独立的显示设备。虽然上述几种视频输出接口各不相同,输出信号的分辨率也可能差别很大,但是其输出控制功能基本都是一样的。一是输出信号的时序控制,包括数据、时钟、使能信号和同步信号。另外是色彩空间转换功能,这是因为一些设备的输入图像数据属于YUV空间,例如数字电视中输入的TS流解码后得到的视频数据等,需要转换为RGB格式后再输出。

在芯片设计过程中,除了考虑面积和工作频率,芯片的功耗成为越来越重要的参数。因为芯片的集成度越高,单位面积所容纳的逻辑门越多,单位面积所产生的热功率也越大。为了保证芯片的正常工作温度,低功耗设计成为了芯片设计流程中重要步骤之一[2-3]。另一方面,很多芯片应用于移动手持设备,需要低功耗设计来降低能耗,增强设备续航能力[4-5]。降低功耗的设计技术有:门控时钟(Clock Gating)、多阈值电压(Multi Threshold)、门控电源(Power Gating)、多工作电压、动态频率调整、动态电压调整等[6]。

本文提出的通用视频输出控制器IP核实现了兼容多种视频输出时序的时序控制逻辑,实现了YUV转RGB模块,转换标准包括ITU-R BT.601[7]、ITU-R BT.709[8]等。模块的实现结构在第1节中详细说明。然后在第2节对整个IP核进行了低功耗优化。在 RTL设计中进行多时钟域划分,手动加入模块门控时钟;在DC综合过程中设置自动插入门控时钟,加入功耗优化步骤。第3节给出了IP核的功耗分析和仿真结果。最后给出本设计的结论。

1 IP核模块设计

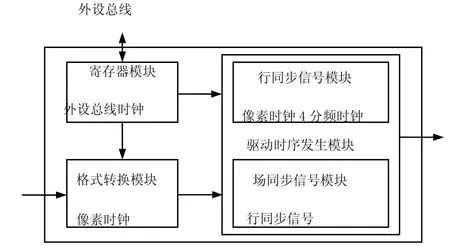

总体模块结构如图1所示,整个IP核主要分为3部分。寄存器模块(Register)用于存储IP核的配置数据,包括YUV转 RGB的系数,输出图像的宽度和高度,同步信号持续长度,消隐期宽度等。寄存器的外部访问接口为AMBA总线的APB接口。色彩空间转换模块(YUV2RGB)根据寄存器模块给出的转换系数完成色彩空间转换。驱动时序发生模块(DTG)主要是根据寄存器模块的时序标准产生输出控制时序,同时输出YUV2RGB模块的产生的数据。

图1 IP核模块结构

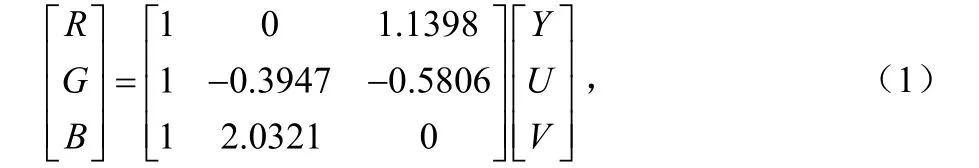

色彩空间转换模块本质是 3维数据的线性变换,线性变换矩阵是可配置的,由寄存器模块给出,因此模块可以支持多种标准的色彩空间转换。模块默认配置支持的是ITU-R BT.601标准,转换矩阵由下式给出:

如果要支持ITU-R BT.709标准,则系数矩阵为:

如果输入数据已经是 RGB空间数据,则需要将变换矩阵配置为3阶单位阵。

根据YUV到RGB空间变换矩阵的形式,模块采用4个整数乘法器实现,结构上采用4级流水线设计,使得模块数据吞吐速率达到工作时钟频率。

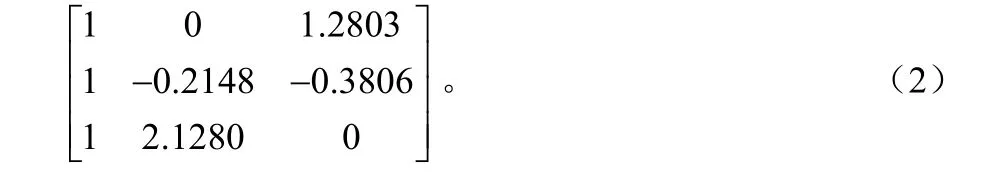

驱动时序发生模块需要产生图 2所示的各个信号,用以支持VGA输出、LVDS输出等。图中PCLK是像素时钟,和模块工作时钟相同。Video表示输出视频数据。Blank/EN信号在VESA标准中表示消隐信号,低电平有效;在LVDS输出时表示数据有效信号,高电平有效。虽然此信号在不同的标准有不同的含义,但时序是相同的,即高电平时对应输出视频数据有效,低电平时对应输出视频数据无效。HSync和VSync分别是行同步和场同步信号,这2个信号在VESA[9]标准中定义,这里不再详述。由图 2可知,各控制信号的产生可以通过计数器对PCLK或HSync计数实现。驱动时序发生器主要由一个像素计数器和一个行计数器实现。各信号的状态由计数器值与寄存器模块中的预设值进行比较得出。

图2 驱动时序发生器输出的各信号的时序

2 低功耗优化

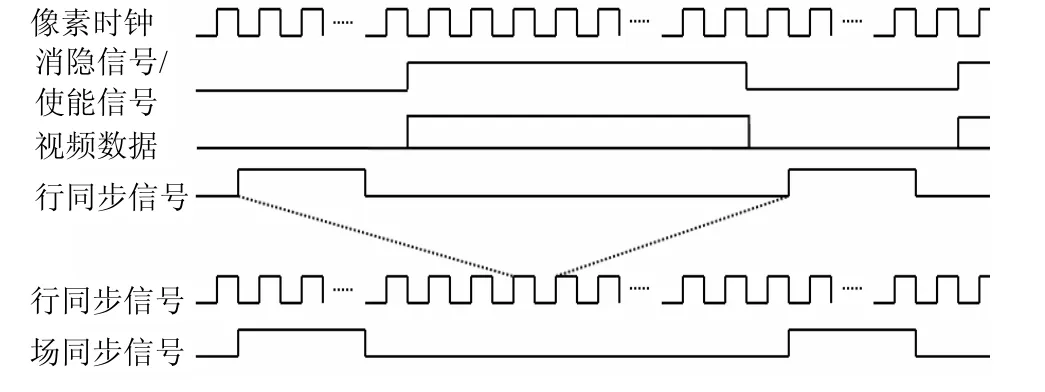

芯片的功耗主要由静态功耗和动态功耗组成。其中静态功耗又称为漏电流功耗,是 CMOS电路的稳定态功耗。降低静态功耗的方法主要是工艺相关的方法,因此在 IP软核的设计中意义不大[10]。动态功耗包括内部功耗和开关功耗,由下式给出:

式中第一项是内部功耗,表示电路单元输入发生变化而输出不变时消耗的功率。第二项是开关功耗,表示电路单元发生变化而输出也变化时消耗的功率。其中sct表示短路电流持续时间;perkI 是内部开关电流;effC 为有效充电电容;Vdd为电源电压; fclk是工作时钟频率。

由动态功耗的表达式可知,减小上述任一参数都可以实现降低动态功耗的目的。由于其中电源电压、充电电容、开关电流这3个参数都和芯片所采用的制造工艺有关,因此本设计主要通过降低工作频率来降低功耗。

首先我们分析 IP核的整体结构,将其划分多个工作时钟域,慢速工作模块采用慢速时钟。图 3是重新划分时钟域后的系统结构图。色彩空间转换模块YUV2RGB工作在像素时钟域,时钟信号为 pclk,是整个模块频率最高的时钟域。寄存器模块则工作在APB总线的时钟域,APB总线是AMBA总线协议中定义的低速总线。驱动时序发生器(DTG)中由于行同步信号和场同步信号的工作速度相差太大,因此分开为2个时钟域来设计。其中行同步信号产生模块(HS)的工作时钟由像素时钟四分频得到,场同步信号产生模块(VS)则使用行同步信号HSync作为工作时钟。这样整个IP核就分为4个时钟域,其中pclk、pclk_div4、HSync是相关时钟。驱动时序发生器的工作时钟被大大降低了。

图3 IP核时钟域划分

划分上述时钟域之后,系统工作频率已经有所降低。但是在寄存器电路设计中,就算寄存器数据输入端不发生变化,时钟信号的翻转也会产生动态功耗。因此如果某个模块在某种条件下不需要输出,或者某寄存器的输入在某种条件下等于输出时,可以禁止输入时钟的翻转,也就相当于式(1)中的频率参数被设置为0,从而降低系统动态功耗。

模块的时钟门控可以通过手动添加[11]。对于设计的视频输出控制器,其中的色彩空间转换模块只需要在输出视频数据有效的时候工作,也就是在Blank信号为高电平的时候正常工作,其余时间YUV转RGB的数据是无效的。因此选择Blank信号作为YUV2RGB模块的时钟门控使能信号,门控时钟的Verilog代码如下:

assign yuv2rgb_clk = blank & pclk;

针对设计中的单个寄存器,由于 IP核中使用的寄存器非常多,手动添加门控时钟电路将会是复杂而繁琐的工作,因此可以使用综合工具检测电路功能,自动添加门控时钟电路。

使用综合工具自动添加门控时钟电路第1步要指定使用的门控时钟单元。门控时钟单元可以是离散的也可以是集成的。离散时钟单元由综合工具用工艺库提供的逻辑门或者锁存器组合而成,里面包含了多个工艺库单元。集成的门控时钟单元则是工艺库提供商设计好并集成在工艺库中的一个独立单元。Design Compiler[1]中指定门控时钟单元的命令为 set_clock_gating_style,例如指定使用工艺库中的锁存器的命令如下:

set_clock_gating_style -sequential_cell latch

指定门控时钟单元后,第2步分析整个IP核的所有寄存器,在可以添加门控的寄存器输入时钟上添加门控时钟单元。插入门控时钟的命令为:

insert_clock_gating -global

global参数指示综合工具添加门控时钟时可以穿越层次结构,尽可能多的复用门控时钟单元,减小芯片的面积和功耗。因为我们在前面手动添加了一个与门作为门控时钟单元,为了避免与门逻辑的潜在毛刺的产生,可以通过以下命令取代手工门控时钟,这是自动添加门控时钟单元的第3步。

replace_clock_gates

第 4步使用 uniquify命令,完成设计的实例唯一化操作,方便后续的布局布线工作。最后是报告插入门控时钟电路的结果report_clock_gating。

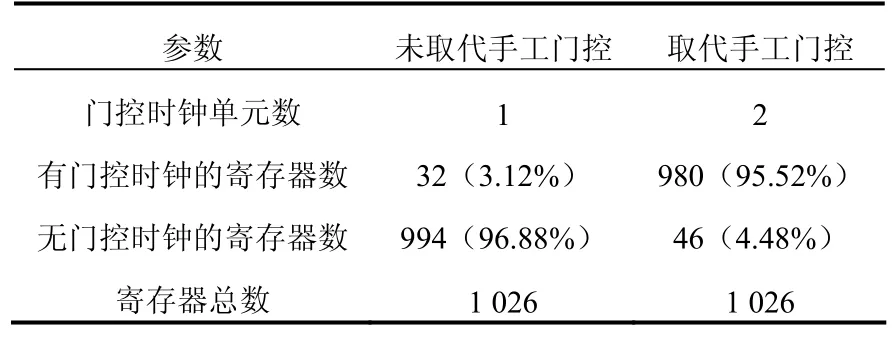

完成上述 5步设置之后,后面就只需要执行普通的综合工作,综合过程中 EDA工具会自动识别门控信号,在合适的位置加入门控时钟逻辑。表一给出了 Design Compiler自动插入门控时钟电路的报告。

表1 门控时钟综合结果

3 功耗分析

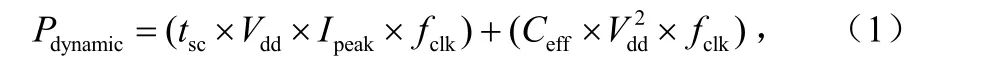

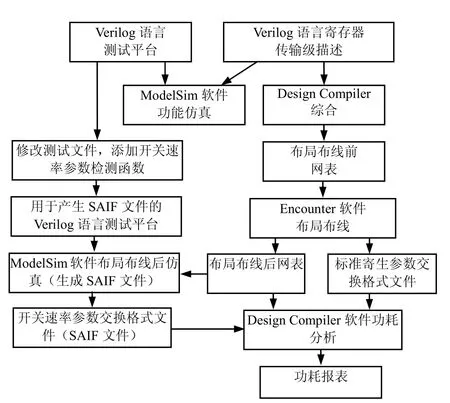

低功耗设计的具体流程如图 4所示。设计流程使用Mentor公司的 ModelSim进行仿真,用 Synopsys公司的Design Compiler进行综合和最终的功耗分析,用Cadence公司的Encounter完成综合网表的布局布线。

IP核的设计从RTL设计开始,这一步还需要进行时钟域划分以及手动添加门控时钟电路。然后对设计好的RTL代码进行功能仿真,修改其不符合功能描述的部分。功能仿真正确之后,将RTL代码综合成门级网表,即布局布线前网表。布局布线前网表再输入到 Encounter中完成布局布线,生成布局布线后网表和SPEF (Standard Parasitic Exchange Format)文件。SPEF文件中包含了工程中所有线网的电容电阻参数。

得到的布局布线后网表之后,通过对此网表进行仿真,我们可以得到SAIF (Switching Activity Interchange Format)文件。SAIF文件包含了网表中各线网状态转换率的统计结果。这里仿真使用的testbench文件可由功能仿真的testbench修改而来,只要在文件中加入统计状态转换率的 Verilog系统任务,包括$read_lib_saif(),$set_toggle_region(),$toggle_start(),$toggle_stop(),$toggle_report()。

最后,将前面生成的SAIF文件,SPEF文件,布局布线后网表,一起输入到Design Compiler中进行功耗分析,得出整个设计的功耗分析报表。

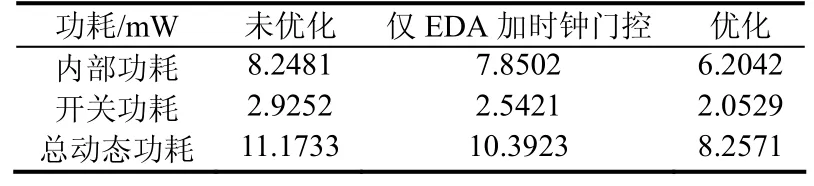

本设计采用的工艺库是SMIC 0.18微米工艺库。为了使生成的SAIF文件所记录的信号状态转换率更为准确,仿真使用的 testbench将视频输出控制器配置成 VESA标准的800x600@72Hz格式,像素时钟为50 MHz。整个仿真过程输出3帧视频图像。为了便于比较,我们还分析了没有进行任何功耗优化的设计的功耗,也分析了不手动添加门控,只使用EDA工具自动添加门控的设计的功耗。表2给出了所有的功耗分析结果。

图4 功耗分析流程

表2 功耗分析结果

由上表的结果可知,功耗优化后的设计比没有任何功耗优化的设计降低了26.1%的功耗。而如果不对色彩空间转换模块手动加门控时钟电路,仅使用DC进行自动添加门控时钟单元,功耗的优化只有7.0%。这从表一中自动添加门控时钟的寄存器数只占3.12%也可以得到侧面验证。上表还说明不能忽视手动优化代码的作用,特别是根据模块功能来对整个模块进行门控的时候。EDA工具只是机械地检查每一行代码,给单个寄存器添加时钟门控。

4 结语

本文设计了一种通用视频输出控制器IP核。针对控制器的功耗,考虑到时钟频率是动态功耗的重要因子,本文通过合理划分时钟域以降低部分模块的工作频率,并采用门控时钟技术对IP核进行功耗优化。最后的功耗分析结果表明,针对时钟频率进行前端功耗优化可以降低功耗20%以上。此控制器支持VESA标准视频输出,支持电视面板LVDS接口,可集成在各种视频处理专用芯片或SoC中,基于其良好的低功耗特性,尤其适用于移动手持设备的显示控制。除了针对时钟频率进行功耗优化,在后端设计时还可以根据工艺库给整个IP核添加门控电源,当系统待机或不需要视频输出时关闭整个模块的电源,从而达到最大限度降低模块的功耗。

[1]Synopsys Inc. Synopsys Design Compiler User Guide[M]. Version Z. Mountain View:Synopsys Inc., 2007:307-312.

[2]FLYNN David, AITKEN Robert, GIBBONS Alan, SHI KaiJian. Low Power Methodology Manual For System on Chip Design[M]. 1st Edition. New York: Springer. 2007:304-310.

[3]徐永钊,田祖伟,阳若宁,等. SoC门级功耗分析方法[J].通信技术,2011,44(02):146-148.

[4]刘成安,孙涛,王银玲.基于nRF24Z1的短距离无线音频传输系统设计[J].通信技术,2008,41(11):50-53.

[5]孟惠霞,吕书勇.基于 ARM的 SD卡文件系统设计[J].通信技术,2009,42(07):135-150.

[6]CILETTI M D. Advanced Digital Design with the Verilog HDL [M].1st Edition. New York: Prentice Hall, 2002:1008-1015.

[7]ITU-R BT.601-6—2007. Studio Encoding Parameters of Digital Television for Standard 4:3 and Wide-screen 16:9 Aspect Ratios[S].

[8]ITU-R BT.709-5—2002. Parameter Values for HDTV Standards for Production and International Programme Exchange[S].

[9]VESA Standard DMT 1.0—2007. Industry Standards and Guidelines for Computer Display Monitor Timing (DMT)Standard[S].

[10]HUANG Zhijun, ERCEGOVAC M D. High-performace low-power left-to-right array multipiler design[C]. IEEE Transaction on Computers. IEEE Computer Society, 2005: 272-283.

[11]罗旻, 杨波, 高德远, 等. 寄存器传输级低功耗设计方法[J]. 小型微型计算机系统, 2004, 25(07):1207-1211.