用AVR单片机实现MMSE位同步捕捉算法

2011-05-17夏继媛胡启龙

夏继媛,胡启龙

(深圳职业技术学院 电子与信息工程学院,广东 深圳518055)

同步是通信系统中收发双方之间相互协调的一个关键环节,同步系统的性能优劣直接决定着通信质量的好坏。没有一个良好的同步系统,则收发之间的通信就无法进行。尤其是数字通信,除了载波同步外,还要求有位同步、帧同步,在扩谱通信中还有扩谱码的同步,对于数字通信网则还有网同步的问题[1-2]。对于帧同步、扩谱码同步和网同步而言,位同步则是前提和基础。位同步又称为码元同步,也有称之为比特同步和时钟同步的[3],是指要求通信接收端必须产生与所接收的码元重复频率和相位相一致的比特定时脉冲序列,以保证接收方能够正确地对数字通信的基带信号进行比特级信息的抽样判决。

本文提出一种基于最小均方误差原理的码元同步捕捉算法,该算法在收发双方时钟不一致的前提下能够快速对比特流数据的起始点做出估计,为后续码元恢复和同步跟踪的顺利完成打下坚实基础。该算法通用性强,利用有限的运算资源能够快速有效地实现基带数字信号的码元初始同步,易于高速单片机及DSP实现,具有良好的抗噪性能。同时用算法取代部分硬件电路,使电路小型化,并以ATMEL公司的ATMEGA16L芯片为例,给出了算法在实现过程中的程序优化策略及注意事项。

1 基本原理

1.1 基带信号处理流程

接收方先对发送方发出的含有噪声的比特数据流进行解调,然后取观察长度为L的比特数据进行采样,要求观察长度L至少包含3个码元数据信息,每个码元采样 M个样点,利用该(L×M)个样点进行位同步捕捉计算,得出比特数据流的起始点,然后利用码元判决算法对含有噪声的数据进行恢复,同时根据计算出来的判决误差实现对码元同步进行跟踪调整。在获得初始位同步的前提下,基带信号的处理流程框图如图1所示。

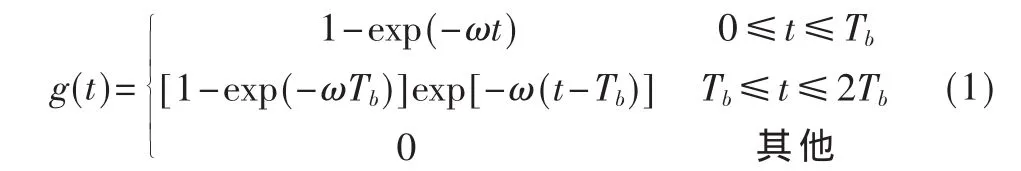

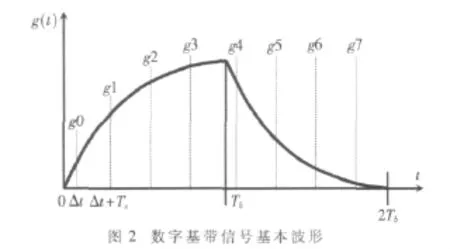

1.2 码元脉冲

无论采用什么波形和码型,数字基带信号都可以用统一的数学式表示,设构成数字基带信号的基本波形g(t)如图2所示,其数学表达式如式(1)所示。

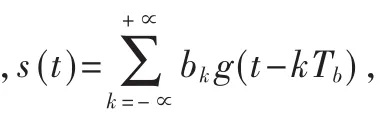

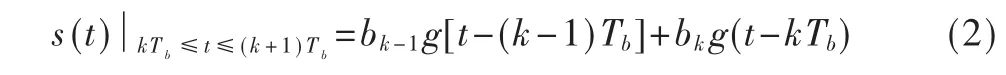

1.3 处理接收信号

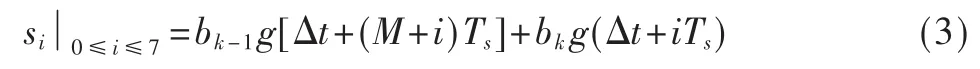

再将gi=g(Δt+iTs)带入式(3)可得:si=bk-1gM+i+bkgi,在同步的条件下,接收信号序列被划分为码元段,每段 M个样点。第 k码元的第 i个样点记为r˜ki,其中含有的有用信号为Aski=A(bk-1g(M+i)+bkgi),式中,A为接收信号幅度。

1.4 快速位同步算法

快速位同步的任务是进行同步点的初值估计,计算出时间偏移的采样点数(即同步点的位置)。基本方法是利用最优化技术,使得接收序列与参考序列的均方误差最小。

建立定时中断时隙周期,0时隙开始采样信号,共KM 个样点,记为 r(n),n=0,1,…,KM-1,去直流后的样点记为 r˜(n),n=0,1,…,KM-1。 在位同步的前提下,一段码元波形对应M个样点,但在未同步时,KM个样点跨越(K+1)段码元段,将其分别编号为0,1,…,K。若最后一段包含m个样点,则首段(第0段)包含M-m个样点,m=0,1,…,M-1。 对应一个 m,假设 Hm,认为这种样点分段与发射信号码元同步,初始定时的算法即检验哪种假设成立;对每种假设,恢复出(K+2)bit数据,以此计算出对应的均方距离Dm,最小者对应合理假设,得出合理的m值后,调整采样时隙,使调整之后的采样时刻为码元的理论采样时刻。

2 算法实现

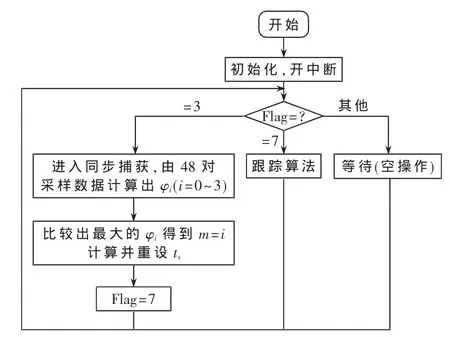

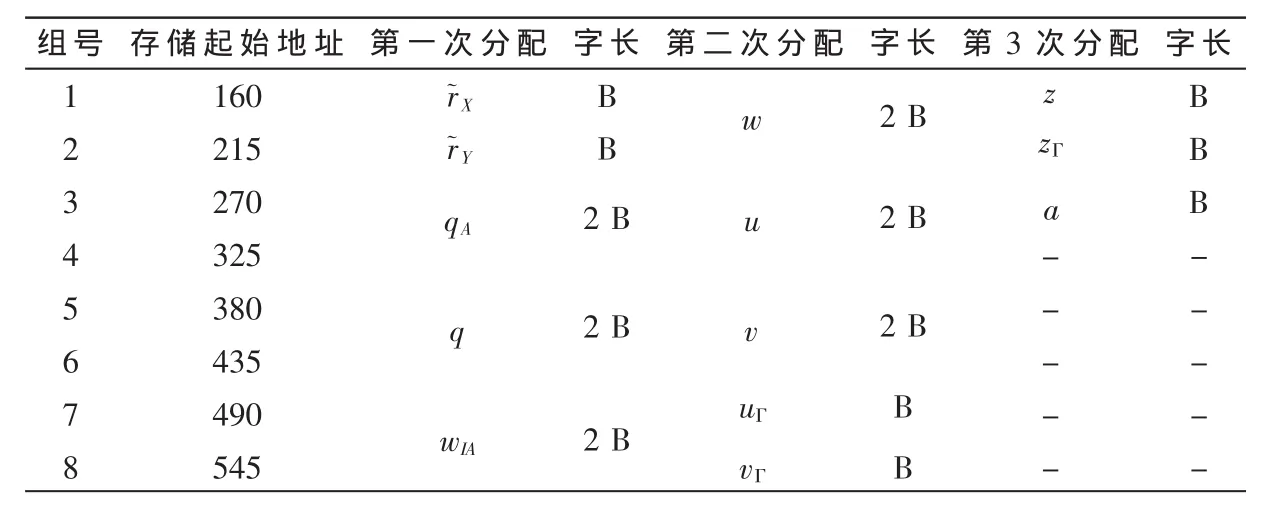

同步捕获的任务是进行同步点的初值估计,系统采样 12 bit数据,即 48对 rX、rY,按照同步捕获算法公式,最终得到时间偏移的采样点数,进而修改采样时隙ts。编程使用的算法公式中间涉及多个序列,根据其使用周期和字长,合理分配内存,对已使用完毕的序列进行覆盖,预防SRAM空间的资源紧缺和分配混乱,降低程序出现不明错误的概率。现以ATMEL公司的ATmega16L单片机为例,程序流程图如图3所示,SRAM具体分配如表1所示,程序从地址为160的内存单元开始,每55个内存单元为一组,共分出8组,进行各个序列的存放,依据运算顺序,可依表格从上到下,从左到右进行三次复用。

图3 程序流程图

表1 同步捕获程序内存分配

在规定了各个运算序列的内存地址之后,即可依据公式进行编程,最终得到同步偏移采样点数m。在实际调试过程中,为了测试程序运算的正确性,在完成48对样点采集之后,将定时中断关闭,用串口将样点传出并在仿真程序中进行理论运算,可得到中间所有序列的理论值和最终的m值。在捕获算法运算过程中,可通过添加简单的串口传数程序传出实际运算出的序列,与理论值进行对比即可方便地检查程序的正确性。

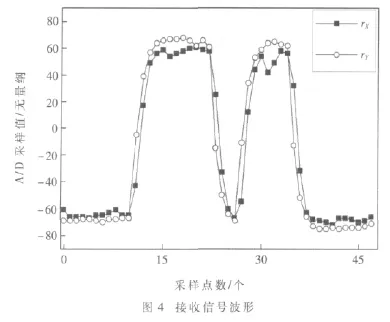

对于m值,亦可通过采样点绘制的波形图判断正误,如图4所示,为某次采集的样点,程序计算出的m值为1,意味着最后一段包含1个样点,则在图中,从右侧去除一个样点,每4个样点一组,恰好能对波形进行合理的采样,此m值正确。

通过测试,同步捕获模块的运算时间为2.245 ms,捕获之后,仍然保持83.3 μs的定时采样时间,平均能保持153 bit的正确接收,这就给同步跟踪的实现创造了很充裕的时间。

综合上述分析,在信噪比SNR很低的情况下,观察长度满足一定条件时,该初始位同步捕捉算法能对比特数据流的起始点做出正确估计,具有较强的抗噪性能。该算法与载波相位、频偏无关,说明此算法具有良好的稳定性。算法结构简单,易于在DSP和高速单片机上实现。笔者已经将该算法在AVR单片机上实现并成功应用于某军事无线电数字通信系统中。

[1]樊昌信,张甫翊,徐炳祥,等.通信原理(第 5版)[M].北京:国防工业出版社,2001.

[2]张应中,张德民,温启荣,等.数字通信工程[M].北京:人民邮电出版社,1996.

[3]谭雪霏.数字通信系统中同步技术的研究[D].南京:南京理工大学,2007.

[4]乔俊杰.QAM解调芯片中码元同步电路的设计与实现[D].南京:东南大学,2006.