一种CMOS电流饥饿型环形压控振荡器

2011-05-11闫琳静

闫琳静,杨 健

(贵州大学 电子科学系 贵州省微纳电子技术重点实验室,贵州 贵阳 550025)

振荡器具有广泛的用途,在通信、电子、航海、航空航天及医学等领域扮演重要的角色,尤其在通信系统电路中,压控振荡器(VCO)是关键部件,特别是在锁相环电路、时钟恢复电路和频率综合器电路中等更是重中之重,VCO几乎与电流源和运放具有同等重要地位。锁相环是一个使输出信号 (由振荡器产生的)与参考信号或者输入信号在频率和相位上同步的电路。在同步(通常称为锁定)状态,振荡器输出信号和输入信号之间的相位差为零,或者保持常数。如果出现相位误差,可采用一种控制机理作用到振荡器上,使得相位误差再次减小到最小。在这样的控制系统中,实际输出信号的相位锁定到参考信号的相位,因而称为锁相环PLL(Phase Locked Loop)[1]。PLL模块如图1所示。

图1 PLL模块图

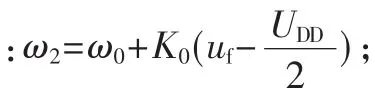

压控振荡器 VCO(Voltage Controlled Oscillator)输出信号的弧度(角)频率 ω2正比于控制信号 uf。 ω2=ω0+K0uf。其中,ω0为 VCO的中心(角)频率,K0为 VCO的增益 (单位 :rad·s-1·V-1)。

图2 VCO的理想特性曲线图

1 反相器环形振荡器设计

由反相器组成的压控振荡器电路实现有多种,其核心电路由数个反相器单元构成,反相器单元如图3所示。振荡频率由每个反相器的延迟时间和级联成VCO的反相器单元个数决定。每个单元的延迟时间由通过的电流、输入负载电容和施密特触发阈值电压决定。为补偿电子空穴迁移率的不同,P、N管的宽长比为 2:1,以保证P、N管有相同的上升和下降时间[2]。

下面分析环形振荡器的频率调节原理[2]。图4是三个非门首尾相连构成的简单环形振荡器,从图中可推导出振荡频率表达式。

图3 反相器单元

图4 非门构成的环形振荡器

2 电流饥饿型振荡器

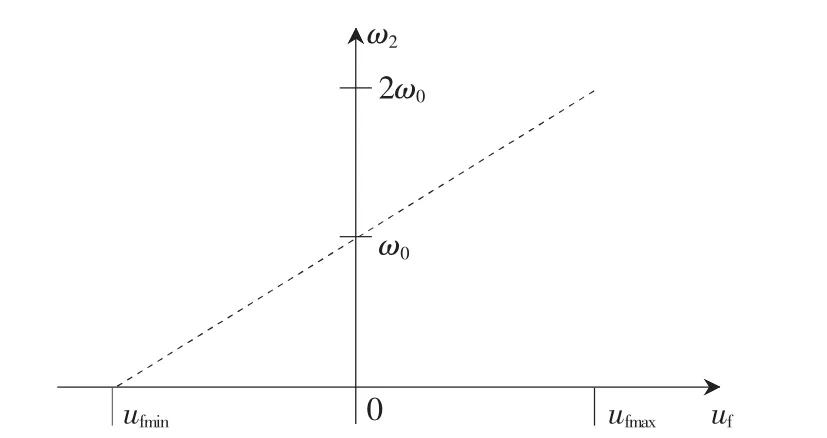

图5 电流饥饿型VCO中单级的简化电路图

电流饥饿型的振荡器是一种传统的振荡器结构,不但结构简单,而且控制电路可以控制反相器偏置电流的大小,同时还可以控制负载电容的充放电电流大小。这种结构可以灵活地控制振荡频率[3]。

电流饥饿型VCO中单级简化电路如图5所示,其工作原理如下:M2管和M3管用作反相器与电流源/沉,共同构成环形振荡器的一级。电流源/沉控制着流过M2管、M3管的电流,即由M2管和M3管构成的反相器处于电流饥饿状态。输入管的漏端电流相等,大小由输入控制电压设定。流过输入管的电流被镜像到环路振荡器的每一级中[4]。

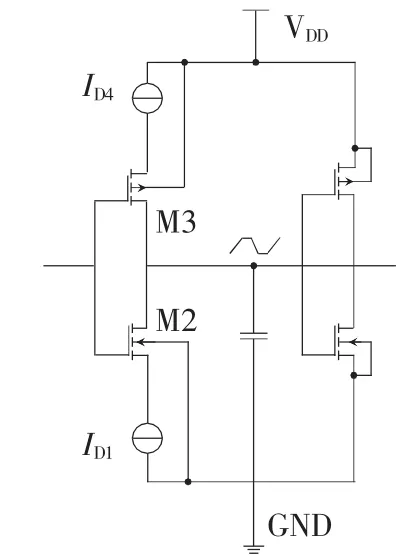

电流饥饿型VCO在CMOS反相器延迟单元两端加上电流源和电流漏结构,利用恒定电流对节点电容进行充放电。设延迟单元偏置电流为ID4和ID1。为了推导出电流饥饿型VCO的设计方程[4-5],考虑了VCO中每一级的简化电路图。M2管和M3管漏端的总电容Ctot为:

式中,Cout、Cin为反相器的输出和输入电容,Ln、Lp为M2、M3 管的栅长,Wp、Wn为栅宽,C′ox为单位面积栅极电容。

M2管和M3管漏端的总电容Ctot可进一步整理为:

用一个恒定电流ID4将从0充电到VSP所需要的时间t1可表示为:

用一个恒定电流ID1将Ctot从 VSP放电到 0所需的时间t2可以表示为:

若 ID4=ID1=ID,则 t1与 t2之和为:

N级电流饥饿型VCO的振荡频率为(N≥5的奇数):

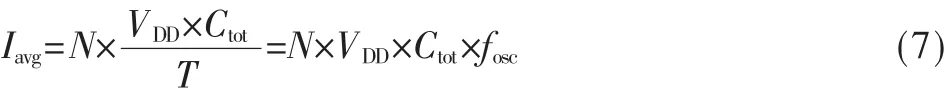

VCO抽取的平均电流为:

VCO的平均功率为:

通常,电流饥饿型VCO的输出都要经过1~2级反相器缓冲后再输出。在VCO的输出端接一个大电容负载会显著影响振荡频率或者会将增益降低到足够小而导致振荡器不再振荡。

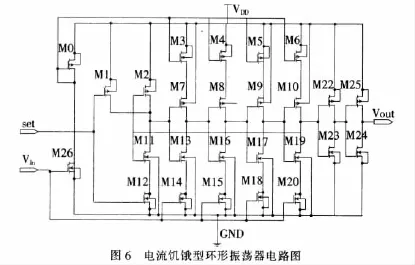

3 压控振荡器实现

电流饥饿型环形振荡器的实现电路图如图6所示,主要包括CMOS反相器延迟单元、自偏置电路、复位电路、输出级电路。电路除了设计带电流源和电流漏结构的CMOS反相器延迟单元以及自偏置电路外,还设计了电路的复位端,当复位信号set为低电平时,与复位端set连接的NMOS管关断,使流过这一级的电流变为0,从而使振荡频率变为0,即振荡器不振荡。当复位信号set为高电平时,与其连接的NMOS管导通,使流过此级的电流不为0,而使环行振荡器开始振荡。

振荡器输出端连接了两个反相器作为输出级电路。输出级可起到对输出波形整形的作用,如果振荡器后端连接分频器等电路,可以适当增大反相器尺寸,以增大电路的驱动能力[4]。

如果考虑由M5管和M6管构成的电流镜的功耗,并假设ID=ID5+ID6,则功耗为式(8)给出的功耗的二倍。为了降低功耗,必须降低ID的值,也就是说,要降低功耗就必须采用较低的振荡频率。

4 仿真及其分析

图7和图8分别为不带输出级电路VCO和带输出级电路VCO的仿真波形,由图可知,输出级对输出波形起到了很好的整形作用。

图7 不带输出级电路VCO仿真波形

图8 带输出级电路VCO仿真整形后波形

由图9可以看出,当控制电压为4.5 V时,电路基本进入稳定振荡状态,振荡频率基本维持在550 MHz左右。

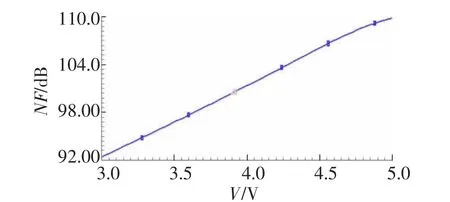

噪声系数 (NF)反映了输出端的信噪比与输入端信噪比的比值,与振荡器噪声水平密切相关。NF不是越大越好,其值越大,说明在传输过程中掺入的噪声也就越大。从图10噪声系数和控制电压之间的变化关系可知,控制电压越大噪声系数也越大,所以控制电压的选择应该根据各项参数折中选择。当电路进入基本稳定振荡状态时,其控制电压为4.5 V,此时的噪声系数为105 dB。

图10 噪声系数随控制电压的变化

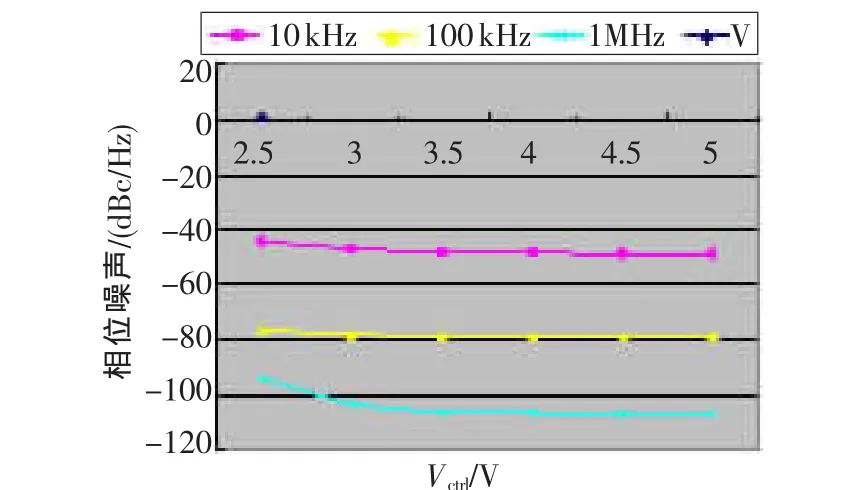

图11为本压控振荡器在100 MHz的参考频率下的相位噪声。相位噪声是对信号变化的一种测量方式,其结果在频率域内显示。如果没有相位噪声,则振荡器的整个功率都应集中在频率f=f0处。但相位噪声的出现将振荡器的一部分功率扩展到相邻的频率中去了,并产生了边带(sideband)。振荡器在某一偏移频率处的相位噪声定义为:在该频率处,1 Hz带宽内的信号功率与信号的总功率比值。

图11 振荡器相位噪声

图12是控制电压从2.5 V~5 V之间变化时,压控振荡器在参考频率为100 MHz、给定偏移频率分别为1 MHz、100 kHz和10 kHz条件下的相位噪声。从图12可以看出,控制电压为4.5 V时,振荡器在给定偏移频率为 1 MHz、100 kHz和 10 kHz条件下的相位噪声分别是-105.432 dBc/Hz、-80 dBc/Hz和-50 dBc/Hz。

图12 相位噪声在不同频偏下的相位噪声

锁相环的相位噪声主要由VCO决定,因此对振荡器的仿真观察和抑制尤为重要。环形振荡器具有易于集成、调谐范围大、占用面积小等优点,主要用在低频的时钟发生器中。电流饥饿型的振荡器是一种传统的振荡器结构,其结构简单,控制电路可以控制反相器偏置电流的大小,同时可以控制负载电容的充放电电流的大小。可见,这种结构可以更灵活地控制振荡频率。本文的锁相环的设计是基于csmc的0.5 μm工艺,仿真工具采用Cadence Spectre。仿真结果表明,本振荡器在给定偏移频率1 MHz条件下的相位噪声达到了-105.432 dBc/Hz,设计结果基本实现了设计要求。

[1]BEST R E.Phase-locked loops design,simulation and application[M].Fifthedition McGraw-will,2003.

[2]王晓娟.CMOS集成电荷泵锁相环的设计与研究 [D].合肥:合肥工业大学,2007.

[3]罗芳杰.电荷泵锁相环的压控振荡器设计[D].合肥:合肥工业大学,2009.

[4]沈少武,程仕意,徐斌富.一种用于电子标签的低功耗高精度时钟电路设计[J].现代电子技术,2008,31(2).

[5]RAZAVI B.模拟CMOS集成电路设计 [M].陈贵灿,程军,等译.西安:西安交通大学出版社,2002.