一种基于FPGA的多DSP数据交换方法

2011-04-24吕卫国沈发江

吕卫国,沈发江,徐 伟

(江苏自动化研究所,江苏 连云港 222006)

随着数字化时代的来临,DSP的应用几乎遍及整个电子领域,在很多需要实时数据处理的场合,即使采用目前最先进的DSP芯片,单片处理器也无法满足大量数据实时处理的需求,往往需要多只DSP并行工作才能完成任务。例如在某水声信号处理系统中,由于前端有48通道的模拟信号采集数据,要完成信号的频率检测及方位计算,单片DSP是无法实现的。根据估算,单片DSP(TMS320C6713)只能实时计算6路信号的频率检测(FFT),那么48路信号做频率检测至少就需要8片DSP,再加上其他的一些运算,必须构建多于8片DSP的处理系统才能完成系统的需求,针对以上需求,本文建立了具有11片DSP的多DSP并行处理系统。

TMS320C6713作为一款高性能的 32-位浮点DSP,具有较强的数据处理能力,并具有低功耗、低成本的优点,适用于精度要求较高且成本控制较严的信号处理场合。其主频可达300MHz,指令周期3.3ns。为了加快处理速度,其内核采用4KB的一级程序缓存(Cache)、4KB的一级数据缓存、256KB的内部存储器,可动态分配64KB作为程序和数据共享的二级缓存。凭借二级高速缓存及VLIW架构,最高运算速度可达 2400MIPS/1800MFLOPS。同时,其内部的 2个同步缓冲串口(McBsp)作为芯片对外接口,能够配合芯片内部的EDMA通道,大大提高其数据处理的吞吐速度。虽然该芯片具有以上的优点,但也存在着外设端口单一,多芯片之间通信方式不够灵活等缺点,这样不利于多 DSP系统建立后数据处理任务的分配和协作。为了解决这一问题,就必须研究多DSP并行数据处理过程中数据在不同DSP之间的交换技术,以便实现多DSP并行处理系统中的运算负载平衡,进一步提高效率。

在本文讨论的多DSP系统中,由于需要对外部输入的数据进行并行处理,并且处理的流程也不固定。因此,各处理器之间必然会存在较多的数据交换,这就需要处理器之间具有较灵活的数据交换能力。TI公司的 TMS320C6713对外的数据接口主要有外部存储器接口(EMIF)以及多通道同步串行接口(McBSP)。使用EMIF接口扩展存储器来实现多DSP之间数据交换是一个比较普遍的思路,但是这只适用于DSP数量较少的情况,当DSP数量增加时,一方面会占用FPGA较多的RAM资源,提高了系统成本,另一方面由于并行高速数据传输,抗干扰能力较差,传输的可靠性降低。因此,在数据交换带宽满足系统要求的情况下,合理利用同步串行接口进行内部数据交换具有占用FPGA资源少,数据传输稳定可靠、控制较简单等优点。基于网络交换机的设计思想,文中设计了基于FPGA的串口数据交换机,将多片DSP均通过各自的McBSP连接到串口交换机,从而实现各只DSP之间数据的灵活交换。

1 多DSP并行处理系统的硬件设计

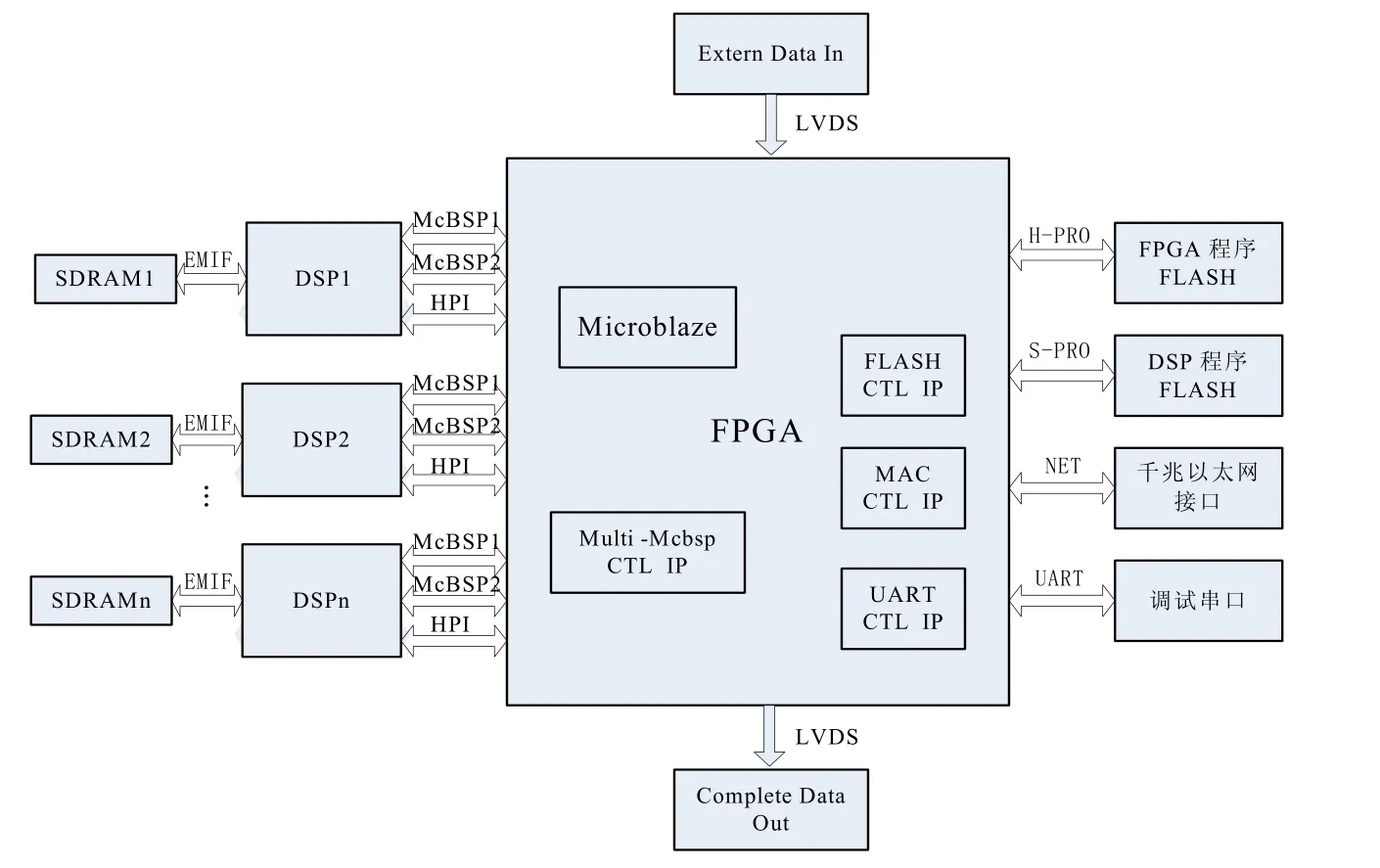

图1是通用多DSP并行处理系统的结构框图,由大规模可编程器件FPGA、多只DSP及外挂SDRAM存储器、FPGA程序FLASH、DSP程序FLASH、千兆以太网口、调试串口、数据输入及数据输出接口等组成。FPGA作为系统的控制核心,内嵌了 CPU(Microblaze),用来管理系统的外部设备,多只DSP作为从设备,主要完成信号处理的任务。各只DSP的主机口都映射到CPU的空间中,作为CPU的从设备。CPU可以通过主机口来访问各只 DSP的存储空间和资源。以太网口主要实现与外部设备的通信。

图1 通用信号处理模块系统结构框图

上述数据处理系统设计的核心是如何实现多只DSP之间的通信控制及数据交换,即如何建立起多DSP之间的数据通信通道,这也是本文讨论的重点。数据交换的性能、数据交换的灵活性以及可靠性是决定数据处理性能至关重要的因素。

2 FPGA内部高速串行互联的实现

2.1 概述

随着 DSP器件技术的发展,同步串行接口(SPORT)作为标准外设出现在各种型号的DSP中,为DSP之间的通信提供了方便。每个同步串行接口均由发送器和接收器构成,一般有6根信号线组成,分别为发送数据(DT)、接收数据(DR)、发送时钟(TCLK)、接收时钟(RCLK)、发送帧同步(TFS)和接收帧同步(RFS)。

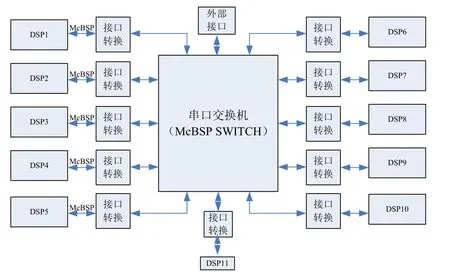

图2 系统同步串行接口交换的连接框图

使用时,在FPGA内部通过开关将不同DSP的同步串行接口的相应信号互联,配置相关寄存器以确保收发时钟、同步信号和数据帧长度的正确合理,便可以实现同步串行接口的数据通信。

2.2 同步串行接口交换机在FPGA中的实现

本系统FPGA选用Xilinx 公司的XC2V3000,是Virtex-II家族的成员之一,具有64*56个逻辑阵列,1728Kbit的块RAM、18*18的嵌入式乘法器、4个时钟管理器,最大达720个I/O口。

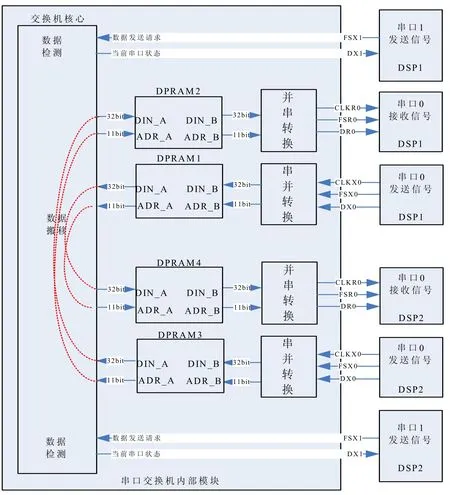

图2所示为系统同步串行接口交换的连接框图,串口交换机采用VHDL语言编写,核心是一种状态机,是系统多只DSP数据交换的核心部件。外部各片DSP都通过自己的同步串行接口连接到一个接口转换模块上,接口转换模块再链接到串口交换机上。接口转换模块主要完成同步串行接口数据的串并转换或者并串转换,以便和串口交换机内部进行数据通信。

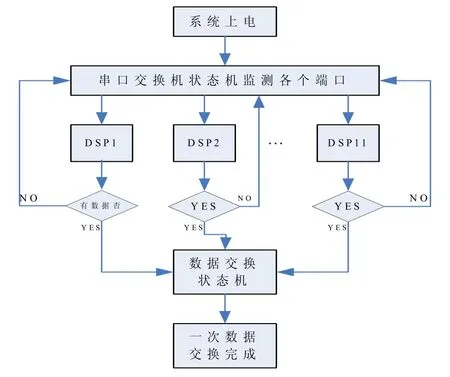

图3 串口交换机工作流程图

串口交换机内部主要包括三个功能模块:数据接收模块、数据检测和搬移模块(串口交换机核心),以及数据发送模块。数据接收模块完成串行端口数据的串并转换并将数据写入到双端口的缓存中;数据检测及搬移模块完成数据包帧头的解析以及数据在不同串行端口缓存之间的数据搬移;数据发送模块完成数据从双端口缓存的读取及数据的并串转换,并发送到相应的串行端口。

图4给出了串口交换机内部结构示意图。由于所有 TMS320C6713共有两个高速串行端口,其中串行端口0的发送和接收端都经过双端口RAM挂接在交换机上,而串口1的发送帧标志管脚和发送数据管脚设置为通用的GPIO管脚,作为交换机的控制和状态信号。其中,串口1的发送帧标志管脚作为DSP数据交换时的请求信号;串口1的发送数据管脚作为当前该片DSP串口0状态指示信号。从图4中可以看出,当DSP1要发送数据给DSP2时,DSP1先检测其DX1的状态,当DX1允许时,则通过FSX1向串口交换机发出数据交换请求,串口交换机接收到数据请求后,查询DSP2的DX1状态,当其DX1允许时,则开始把DSP1串行端口0的接收缓存(DPRAM1)的数据搬移到DSP2串行端口0的发送缓存(DPRAM4)中,通过串行端口发送到DSP2中,完成本次数据通信;以此类推,其他DSP之间进行数据交换时也采取类似的过程。

图4 串口交换机内部结构示意图

3 串口交换机软件实现

本设计中的软件基于TI公司CCS开发环境,开发环境提供了DSP芯片支持库CSL,缩短了软件的开发周期。具体配置和收发程序如下。

串口交换机的数据包格式为:

其中,0x5555555D为发送数据帧头。DST是目的节点号,SRC是源节点号,CNT为发送数据长度,中间四个32位字为保留字,最后是数据区。

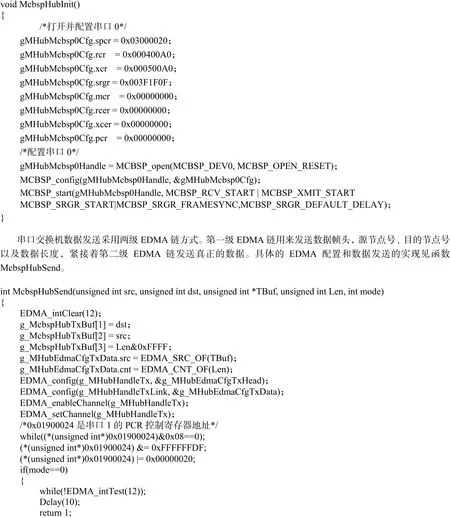

串口交换机初始化:

串口交换机使用串口0作为数据交换的通道,大部分参数配置都参考默认配置,需要注意的两个地方是:在对串口0的配置中将PCR(串口控制寄存器)寄存器的 FSXM 位设置为 0(MCBSP_PCR_FSXM_EXTERNAL),即发送由外部提供帧信号;在对串口1的配置中,将 PCR寄存器的 RIOEN为设置为 1(MCBSP_PCR_RIOEN_GPIO),即将FSR和CLKR管脚作为GPIO使用,用于触发串口0的数据发送。初始化代码见函数McbspHubInit。

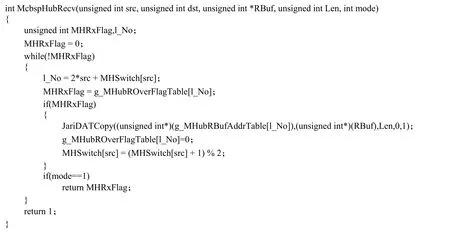

串口交换机数据接收采用双缓冲EDMA传输链结构。EDMA控制器提供了一种灵活的传输机制,称为“连接”(linking),可以将不同EDMA传输参数组连接起来,组成一个传输链,为同一个通道服务。在传输链中,一个传输的结束会导致自动从参数RAM中装载下一次传输需要的事件参数。在EDMA链接收完数据后,会相应的置上接收标志,当用户程序需要接受相应节点的数据时,只需判断相应节点的数据标志位,如果标志位准备好,则应用程序可以在相应的缓冲区读取数据,否则,等待数据接收好标志,直到标志已好,接收数据。接收函数代码见函数McbspHubRecv。

4 结束语

基于串口进行数据交换的多DSP并行综合处理平台作为一种通用的数据处理平台,在提供高性能的信号处理能力的同时,可实现多片DSP之间的较为有效的数据交互,实现过程简单、易行,具有连线简单、通信速度快、可靠性高等特点,是一种解决多片DSP并行处理与信息交互的有效方法。该方法在某型信号处理机中得到应用。实际应用证明该方法简单、可靠,满足了系统的数据实时交换要求。

[1]TMS320C6713BGDP300 data sheet [M].Texas Instrument,2005.

[2]Virtex-II Platform FPGAs complete data sheet[M].Xilinx,2007.

[3]黄飞,乔纯捷,王跃科.网络互联型多DSP并行处理系统设计[J].计算机工程,2007,23(33):230-232.

[4]夏军营,乔纯捷,王刚.基于以太网接口的多DSP监控技术研究[J].计算机测量与控制,2007,15(7):913-915.

[5]李方慧,王飞,何佩琨,等.TMS320C6000系列 DSP原理与应用 [M].2版.北京:机械工业出版社,2000.