数字化短波发射机功率反馈控制系统的设计与实现

2011-03-21崔浩贵屈晓旭

崔浩贵,高 俊,屈晓旭

(海军工程大学电子工程学院,武汉 430033)

1 引 言

随着微电子技术的发展,以及数字信号处理器(DSP)和FPGA性能的提升,传统的短波发射机正在朝着数字化方向发展。短波发射机的数字化能显著提高设备的小型化、集成化和通用化,并能有效降低生产成本。在实际中,短波发射机的功放输出功率并不稳定:一方面,由于温度、电流等因素的影响,当短波发射机功放的输出端通过天线调谐器连接天线时,要防止因反向功率过大而损坏天线调谐器和功放;另一方面,短波发射机发射的射频频段为2~30MHz,约有15倍频程,短波功放在不同频点上的输出功率并不平坦[1]。在短波发射机的使用过程中,保持发射机发射功率的稳定性具有重要意义,尤其是在信道探测等特殊场合中。

为此,本文设计了一种功率反馈控制系统,该系统通过在功放输出端采样射频信号进行功率的反馈控制,能保护发射机并保证其输出功率的稳定性。

2 功率反馈控制系统的总体设计

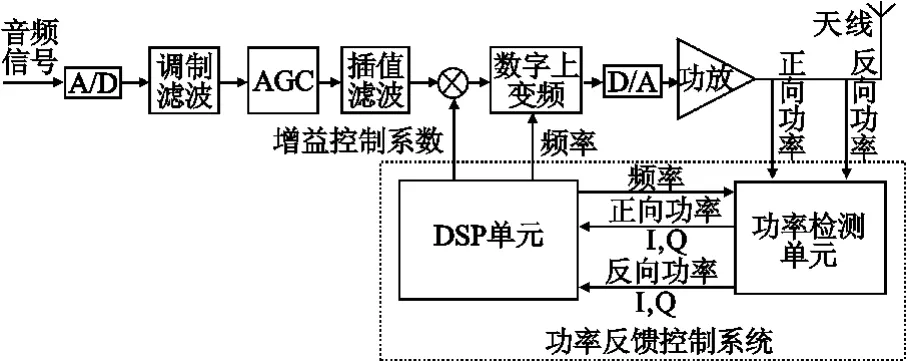

数字化短波发射机功率反馈控制系统的总体设计框图如图1所示。

图1 功率反馈控制系统总体设计框图Fig.1 The design block diagram of power feedback control system

图1中从音频信号输入到天线输出部分是短波发射机的发射通路,音频信号通过A/D采样调制滤波、AGC、插值滤波、数字上变频、D/A等模块之后,再经过功放,最后通过天线发射出去。在发射通路中,增益控制系数β通过与基带信号相乘控制发射机的发射功率,β的值由DSP计算得到。

图中虚线框部分为功率反馈控制系统,主要由功率检测单元和DSP单元组成,功率检测单元实现功率采样,DSP单元主要功能是功率计算和增益控制系数的计算。

3 功率检测单元设计

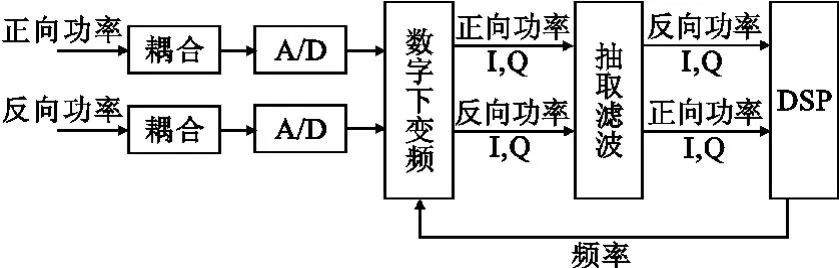

功率检测单元的主要功能是在功放输出端采样正向功率和反向功率,进行频谱搬移和降低数据采样率,最后将采样率较低的正向功率和反向功率的I、Q值传给DSP单元。功率检测单元主要由射频A/D采样模块、数字下变频模块和抽取滤波模块组成,通过A/D芯片和FPGA电路实现,功率检测单元的设计框图如图2所示。

图2 功率检测单元的设计框图Fig.2 The design block diagram of power detection unit

3.1 射频A/D采样

从发射机功放输出端耦合回来的正向功率和反向功率都是发射机发射的射频信号,短波发射机射频频率为2~30MHz,所以对A/D器件的采样速度有较高的要求,本系统采用的射频 A/D芯片为AD9233,AD9233的采样率设计为100MHz。

3.2 数字下变频

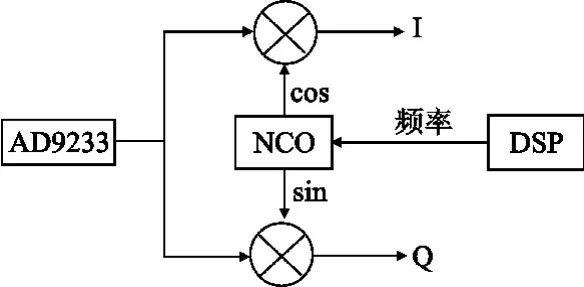

AD9233采样到射频信号后将进入数字下变频模块进行频谱搬移,将信号频谱从短波射频频率搬移到基带上。图3是数字下变频的原理框图[2],数字下变频NCO的频率字由DSP给出,由于在发射机发射通路中数字上变频的频率字也是由DSP给出,这样就保证了上变频的频率和下变频频率的一致性,从而实现准确的频谱搬移。

图3 数字下变频原理框图Fig.3 Block diagram of DDC

本系统中数字下变频模块由FPGA完成,采用NCO IP核产生离散的正弦波,NCO的频率字由DSP给出,NCO的频率字计算如下:

式中,fc为频率字,f0为频率,fclk=100MHz。

3.3 抽取滤波

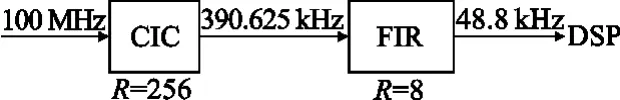

经下变频模块出来的I、Q数据的采样速率仍然为100MHz,为了能将此数据送入DSP处理,必须先对数据进行降采样处理。抽取滤波器的作用是降低数据采样率的同时滤除带外的杂波分量,该模块如图4所示。

图4 抽取滤波器Fig.4 Decimation filter

本系统的抽取滤波模块采用CIC抽取滤波器和FIR抽取滤波器级联的方法实现,CIC抽取滤波器实现256倍抽取滤波,FIR滤波器实现8倍的抽取滤波,最终将数据的采样率从100MHz降到48.8kHz后送到DSP进行下一级的处理。

CIC抽取滤波器的零极点相消,只需要用加法器、积分器和寄存器就能实现,不需要乘法,在高速抽取中非常有效[3]。CIC滤波器由积分部分和梳状滤波部分组成,CIC抽取滤波器由FPGA通过IP核实现。本设计中,CIC滤波器抽取256倍,将采样率从100MHz降到390.625kHz。

FIR抽取滤波器抽取8倍,将采样率降到48.8kHz后将数据传给DSP进行下一步的处理,FIR滤波器采用分布式算法[4]。分布式算法可以减小硬件规模,提高电路的执行速度。FIR抽取滤波器也在FPGA中用IP核实现。

4 DSP单元算法设计

4.1 功率计算

驻波比是常用的射频技术参数,是衡量天馈效率的重要指标,当发射机与天线完全匹配时,两者的电阻分量相同,感抗分量相互抵消,此时反向功率为0,驻波比为1,即当驻波比等于1时,发射机的能量能最有效地传到天线上去。在实际中驻波比并不时时都为1,因此要根据驻波比控制发射机的发射功率,防止功放因反向功率过大而烧坏,在驻波比较大时要对电路重新调谐。

DSP在接收到功率检测单元送来的速率为48.8kHz的I、Q数据之后,首先要将此I、Q数据计算成功率的电平值,功率的电平值的计算公式为

式中,m表示功率的电平值。

计算得到的正向功率电平值mf和反向功率电平值mr用于增益控制单元的输入信号和电压驻波比的计算。电压驻波比的计算公式为[5]

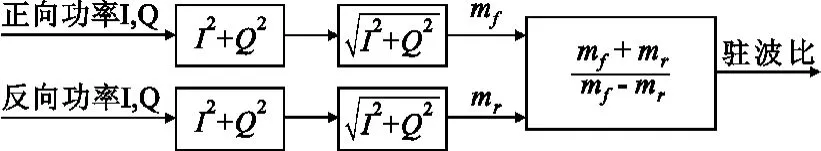

DSP功率计算单元主要实现驻波比和正、反向功率的计算,DSP功率计算的算法流程如图5所示。

图5 DSP功率计算算法Fig.5 Power calculation in DSP

4.2 增益控制

DSP增益控制模块能实时地根据功率计算单元得到的驻波比和正、反向功率电平值调节功放的输出,以防止因反向功率过大而损坏天线调谐器和功放,保持发射机发射功率的稳定性。增益控制模块通过改变增益控制系数 β来实现对发射机发射功率的控制。

在增益控制算法中,首先要根据驻波比的大小进行增益控制,防止因反向功率过大而烧坏功放;其次,为了使功放的输出稳定在期望值,还要根据正向功率值进行增益控制。假设通过驻波比增益控制得到的系数为α,通过正向功率增益控制得到的系数为 γ,最后DSP输出给发射机发射通路的增益控制系数β为这两项的乘积,即:

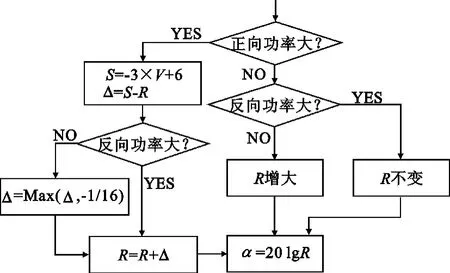

4.2.1 驻波比增益控制

在实际控制过程中,当正向功率较大时,若反向功率也较大,表示此时功放和天线调谐失调,应迅速降低增益,使功放输出幅度减小;若反向功率较小则适当降低增益值。当正向功率较小时,若反向功率较大,则保持增益值不变;若反向功率较小,则逐渐提高增益值,使功放输出幅度恢复到理想值。

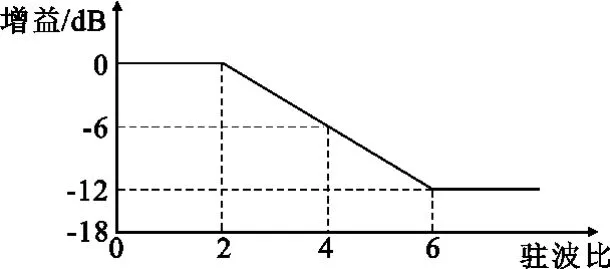

驻波比增益控制算法在驻波比较大时降低功放的输出幅度,驻波比对应的增益值算法如图6所示。

图6 驻波比对应的增益值算法Fig.6 Gain calculation corresponding to standing wave ratio

DSP中的驻波比增益控制程序流程如图7所示。

图7 驻波比增益控制程序流程Fig.7 Processing flow chart of gain control to standing wave ratio

4.2.2 正向功率增益控制

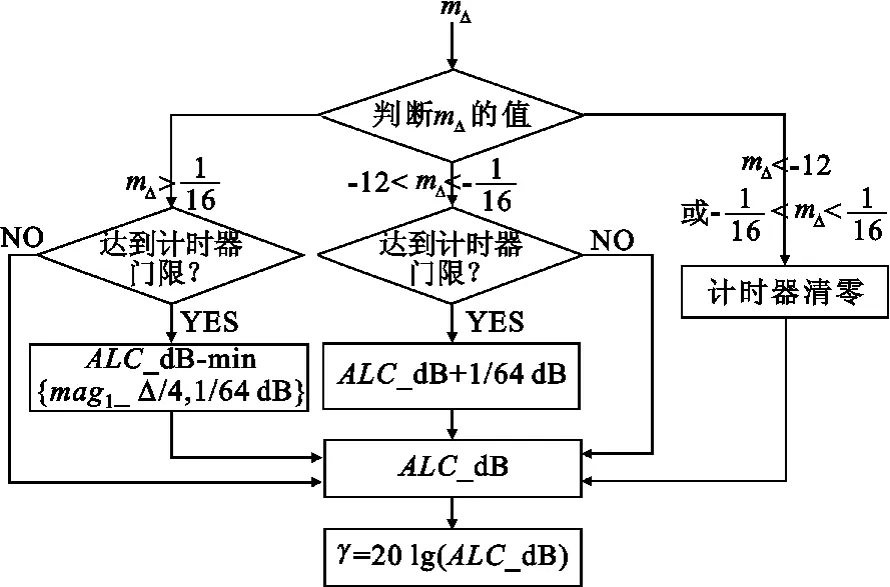

为了保持短波发射机发射功率的恒定,在根据驻波比调节发射机增益之后,还要根据正向功率的电压值来调整发射机增益。假设当发射机发射功率为1 kW时对应的正向功率对数形式的理想值为mi,将发射端反馈的正向功率mf转换成对数值mfdB,定义mf与理想值mi的差值mΔ为

通过比较采样回来的正向功率值mfdB和理想值mi的差值mΔ的大小,可以得到正向功率的增益控制系数 γ,当差值mΔ过大时,表示功放的输出过大,要减小 γ,γ的减小过程是渐进的,需要计时器来实现;当差值mΔ过小时,表示功放的输出过小,要增大 γ;当差值mΔ在合理范围内时,无需调整γ。根据反馈的正向功率值进行增益控制得到增益因子 γ的程序流程如图8所示。

图8 正向功率增益调整流程图Fig.8 Gain adjusting flow chart by the forward power

5 结束语

本文设计和实现了数字化短波发射机的功率反馈控制系统,详细分析了功率反馈控制系统中各模块的信号流程和算法。功率反馈控制系统在功放输出端直接采样射频信号[6],通过FPGA和DSP来实现,易于移植,可以用于不同的数字化短波电台。

本文设计的功率反馈控制系统在国内某厂生产的数字化短波发射机上进行了试验,实测结果表明该系统能使功放的输出功率稳定在期望值的±0.25dB范围内,并且能有效防止因功率过冲烧毁功放。功率反馈控制系统提升了数字化短波发射机的性能,在保护功放的同时保证了发射机发射功率的稳定性,是数字化短波发射机的必要组成部分。

[1] 龙剑飞,曹燕,宁更新.基于零中频的短波发射机DSP单元的设计与研究[J].科学技术与工程,2009,9(7):1706-1711.LONG Jian-fei,CAO Yan,NING Geng-xin.Design of High Frequency Transmitters DSP Unit Basedon Zero-intermediate Frequency Technology[J].Science Technology and Engineering,2009,9(7):1706-1711.(in Chinese)

[2] Girau G,Martina M,Molino A,et al.FPGA digital down converter IP for SDR terminals[C]//Proceeding of the Thirty-Sixth Asilomar Conference on Signals,Systems and Computers.Pacific Groove,USA:IEEE,2002:1010-1014.

[3] Jovanovic Dolecek,Mitra S K.Simple method for compensation of CIC decimation filter[J].Electronics Letters,2008,44(19):1162-1163.

[4] 陈亦欧,李广军.采用分布式算法的高速FIR滤波器ASIC设计[J].微电子学,2007,37(1):144-146.CHEN Yi-ou,LI Guang-jun.Design of a High Speed FIR Filter ASIC Using Distributed Arithmetic[J].Microelectronics,2007,37(1):144-146.(in Chinese)

[5] Carbonini L,Manara A.A procedure to evaluate the output VSWR of high power amplifier[C]//Proceeding of1998 IEEE International Symposium on Electromagnetic Compatibility.Gaithersburg,USA:IEEE,1998:241-244.

[6] 李忠琦,凌翔,胡剑浩.软件无线电构架研究[J].电信科学,2007(7):73-78.LI Zhong-qi,LING Xiang,HU Jian-hao.Introduction of the Ar chitecture of Software Radio[J].Telecommunications Science,2007(7):73-78.(in Chinese)