基于CPLD的彩色线阵CCD驱动设计

2011-03-16侯作凤陶宗慧温彬曾佑洪姚建波安志勇

侯作凤,陶宗慧,温彬,曾佑洪,姚建波,安志勇

(长春理工大学 光电工程学院,长春 130022)

随着彩色扫描仪市场的迅速增长,人们对彩色图片采集系统的主要指标,如采样速率、分辨率、精度等方面,都提出越来越高的要求[1]。彩色线阵CCD(Charge Coupled Device)芯片TCD2703D是一种光电转换式图像传感器。以其高速度、高灵敏度、低暗电流等一系列特点,而成为现代图像扫描系统中的优秀传感器代表,日益得到广泛应用。在其应用过程中,其驱动时序的设计,是 CCD数据采集电路设计的关键之一;CPLD是一种多用途、高密度的复杂可编程逻辑器件,可将系统的部分或全部功能集成在一块芯片上,并且具有设计方便灵活、易于修改等特点,可大大缩短研制时间,并减小系统硬件复杂度。在 CCD驱动时序设计中,传统方法是采用74系列的电子元器件,获得的结果往往线路复杂、干扰严重、不便修改。相比之下,基于CPLD技术的线阵CCD驱动电路的设计方案,具有功耗低、速度快、体积小、抗干扰强的特点。可提高工作频率,而且在设计完成后,可随时对CPLD重新编写来产生不同的时序,以满足CCD应用开发的需要,而不必更改与CPLD的外部连线,有利于驱动电路的调试和升级。

1 TCD2703D主要特点和驱动时序分析

1.1 TCD2703D主要特点

TCD2703D是一种高灵敏度、低暗电流,三行各为7500像元的彩色CCD,主要用于彩色图像扫描。像元为光电二极管;单像敏元尺寸为 9.325m×9.325;像元间距为 9.325;像元行间距37.3;有效长度为69.9mm;内置嵌位电路;封装类型为 68-pin CERDIP;色彩滤光片:红、绿、蓝;两相5V脉冲驱动,14路驱动信号的最高频率为25MHz;三色信号奇偶并行,共六路输出信号;供电电源为12V。扫描A3页面可以有24lines/mm的分辨力。

1.2 驱动时序分析

高速CCD的驱动时序是一组周期性且关系比较复杂的脉冲信号,它是影响CCD器件的信号处理能力、转移效率、信噪比等性能的一个重要因素[1,8]。

图1 TCD2703D的主要时间关系图Fig.1 The main time diagram of TCD2703D

TCD2703D正常工作时需要14路驱动信号,即两相各四路时钟信号1A、1A以及一路2B、像元复位信号RS、嵌位脉冲CP、三路行同步信号SH。除此14路信号外,为了数据采集接口同步驱动还需要设置如下信号:行同步采样信号 FC[3]。整个驱动信号的工作过程如下:当SH的高电平到来时,CCD传感器曝光的光敏单元会将采集到的光信号转移到相应的移位单元中。SH为低电平时候上述转移过程完成,光敏单元进入下一行周期感光积分,而进入移位单元中的信号将在两相操作时钟的作用下移出。RS信号的作用是减小两像元之间的相关信号,可在当前像元信号输出后到下一个像元信号到来前,对残余信号进行清除。当在最高25M驱动频率下,各驱动脉冲必须严格满足相位时序要求,才能保证高速CCD器件TCD2703D的正常工作,依据除了其时序关系图之外,更主要的是各时序信号的时间关系要求。如图1所示,规定了这些时间意义。注意:在“note”标示的时间内保持RS、CP引脚为低电平。在表1中给出了具体的时间值。

表1 TCD2703D的时间匹配要求Tab.1 Time to match the requirements of TCD2703D

2 应用原理图和VHDL语言的驱动时序设计

QuartusⅡ软件有多种输入方式:原理图输入方式、状态图输入方式、VHDL语言输入方式。且支持层次化设计输入方式,这种灵活性使设计者可以采用最适合各部分的设计方法[4-5]。其中原理图方式类似于硬件电路设计情况下的原理图设计,利用基本的门电路符号或模块完成设计;VHDL作为一种硬件描述语言,其编程结构类似于计算机中的C语言,在描述复杂逻辑设计时非常简洁,具有很强的逻辑描述和仿真能力,是当前系统硬件设计语言的主流[6,7]。运用VHDL语言设计系统能够高效直接地描述设计。上述两种方法结合使用能够直观、快速建立设计,并高效地调整和修改方案的整体和细节。在ALTERA公司的QuartusⅡ开发环境下,采取自顶向下的设计方法。在完成程序的输入,在Quartus软件平台进行编译和仿真从而验证设计的功能和时序特性是否符合设计目标,同时进行逻辑优化;反复上述过程完成设计实现过程,则可以通过JTAG接口为硬件芯片进行编程,进入到实体电路功能验证阶段。

2.1 驱动时序和功能仿真

根据驱动脉冲的时序关系,可以确定CCD基本驱动信号的参数,各路脉冲参数如下:为频率25MHz,占空比为1:2的方波;RS的频率25MHz,占空比约为 1:5的方波;光积分时间内,至少有3822个RS脉冲。PHI的频率25MHz,占空比约为1:5的方波;但是其相位与RS信号不同。在保证基本光积分时间下,积分时间的改变可通过VHDL程序内改变SH周期来实现,光积分时间为SH下降沿与SH上升沿之间的时间,可以通过编程设置[8]。

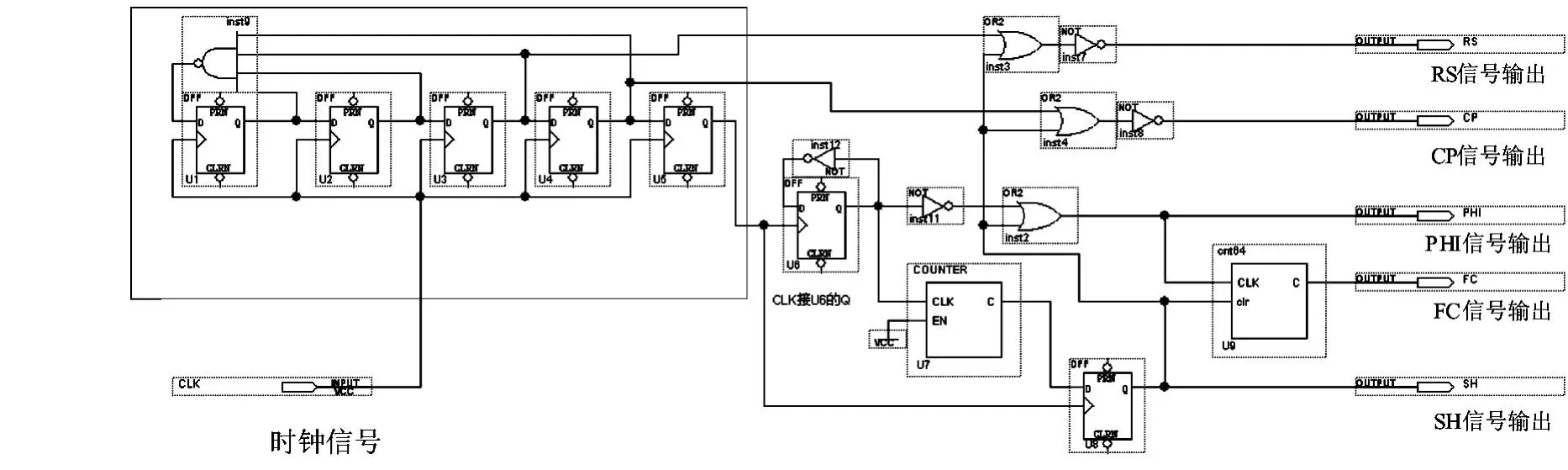

经过设计 CCD时序发生器的主要程序如图2所示。输入信号为CPLD的输入主时钟信号;输出信号为HS、RS、CP、PHI和FC,前4路信号在后面的硬件电路中触发产生 CCD芯片直接驱动所需要的14路信号。这个时序发生器主体由环形计数器产生主时钟分频信号,同时提供5个不同相位信号。取其中U4、U5作为RS、CP信号的源,当然可以根据需要选择计数器中其他的信号结点。这样的设计结构就是为了灵活选择相位。

FC信号是为信号采集系统提供的信号,并不是驱动 CCD的信号,需要根据实际信号采集的需要和经验判断来确定时序关系。

COUNTER单元是由VHDL语言设计的,完成积分时间的设置功能。HS信号保持高电平150个周期,然后变为并保持低电平4000个周期,而后立即变为高电平。

CON64单元是采用VHDL语言设计的,完成延时直到第一个有效像元输出,然后令保持高电平,需要注意的是 TCD2703D的前端哑输出为64个。

经过设计确立的程序,需要在Quartus平台下进行了仿真,输出波形报告。每个积分时间内,各信号总体波形满足要求。细节上各信号的相位关系满足要求。

图2 Quartus环境下的原理图Fig.2 The schematic in Quartus environment

2.2 驱动电路硬件设计

由于产生 CCD的驱动时序的信号不能直接驱动TCD2703D,需要相应的电源、驱动增强和输出放大电路,因此TCD2703D的驱动电路主要由下列模块组成:时序产生模块,增强驱动模块、输出放大模块等。

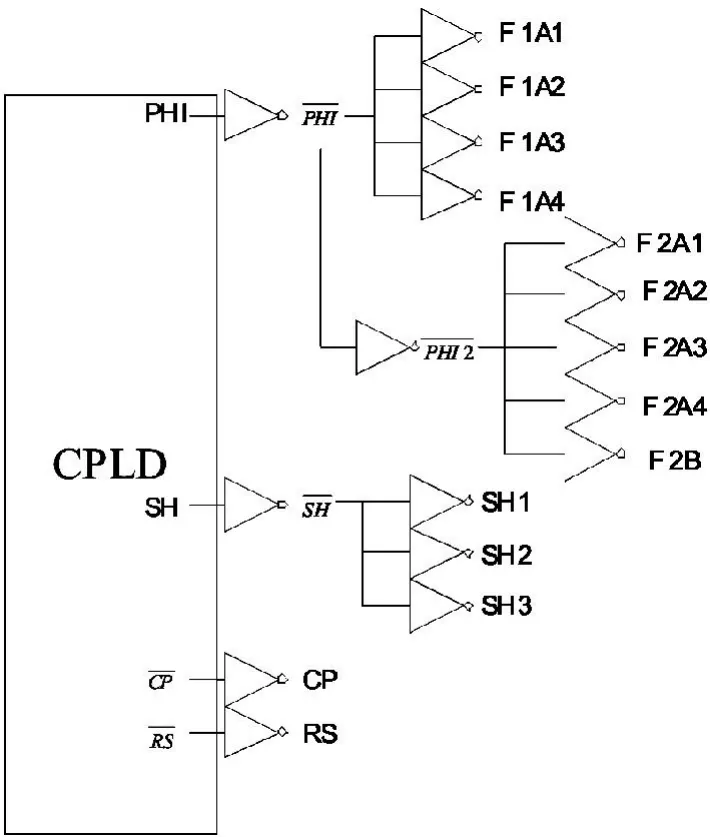

时序产生模块即为CPLD芯片,其内部的时序发生器产生 CCD驱动信号。需要重点说明的是增强驱动模块:为了匹配 CCD对信号驱动能力的需要,工程上常常使用CMOS工艺的门电路来增强驱动能力。考虑到速度要求,以74AHC04芯片为信号做增强驱动,它的延迟时间小于3ns,输出电流达到20mA,是较好的一颗增强驱动器。

图3 增强驱动的信号流程图Fig.3 Enhanced driver's signal flow graph

如图3所示,CPLD输出信号HS和RS的输出引脚各接一个74AHC04的反相器增强驱动,为了做到相位一致,CP和PHI在CPLD内部程序应首先各反向一次,然后在输出引脚各接一个74AHC04的反相器增强驱动;PHI信号经过CPLD输出引脚的反向器,输出 PHI需要进行二次的反向驱动得到1A1、1A2、1A3、1A4、1A1和 PHI2;PHI2进一步进行反向驱动增强得到2A1、2A2、2A3、2A4、1B;SH经过输出CPLD对应引脚上连接的反相器反向得到 SH,再经过三个反相器输出增强后的 SH1、SH2和 SH3。CPLD 晶振为125MHZ。上述过程产生的 14路驱动信号输入到TCD2703D的对应信号引脚端,完成对芯片的驱动。

输出信号的放大器接法为增益可调的差动放大器接法,反馈环路的四个电阻要求相等[9]。运算放大器信号输入的负端接基准电压,作为参考暗电压。运算放大器需要100 MHz的带宽,选用 ADI公司出品的AD8061运算放大器。

3 CCD驱动时序的实验测试

在进行了上述设计和仿真验证之后,为了准确验证上述的功能仿真,在设计中根据TCD2703D的技术参数,选用ALTERA公司的MAX7000S系列芯片EPM7064STC-10。该器件可通过JTAG接口实现在线编程(ISP)功能。引脚到引脚的逻辑延时为 10.0ns,工作频率可达 175.4MHz,完全满足设计要求。以本文的方案设计硬件电路,外部时钟信号为100MHz作为CPLD的基准信号,其它时序信号的产生都是以此为基础。

图4 KCHPCI数据采集卡采集到的视频输出信号波形Fig.4 Image the video output signal waveforms by acquisition card KCHPCI

使用PCI数据采集卡,在PC上位机上安装的KCHPCI软件环境中,CCD实验视频信号波形如图4所示。

4 结论

本文在分析TCD2703D型CCD驱动时序的基础上,结合CPLD和VHDL语言,设计了一个高速 CCD驱动电路。仿真和测试结果表明,本文设计的CCD驱动时序发生器符合TCD2703D芯片的驱动要求。由于驱动电路的结构是可再编程,如果要改变某些功能,则可在不改变任何硬件的情况下,只需对器件重新编程,就可实现驱动电路的升级。

[1]王庆有.CCD应用技术[M].天津:天津大学出版社,2000:46-491.

[2]孟颖,王陆,赵馨,等.基于TCD1200的直径测量系统研究[J].长春理工大学学报:自然科学版,2009,32(2):542-544.

[3]黄进,郭立红,李岩,等.高速CCD数字视频采集和并行存储技术[J].长春理工大学学报:自然科学版,2004,27(3):104-106.

[4]常丹华.一种新的CCD外围电路设计方法[J].传感器技术,2001,20(6):32-341.

[5]张勇,唐本奇,肖志刚.基于CPLD的CCD通用驱动电路设计方法[J].核电子学与探测技术,2005,25(2):214-217.

[6]邢建平,曾繁泰.VHDL程序设计教程[M].北京:清华大学出版社,2005:31-191.

[7]兰荣清.线阵CCD驱动设计新方法[J].光电子激光,1997,8(4):295-2971.

[8]虞益挺,饶伏波,乔大勇.一种新型CCD驱动电路设计方法[J].传感技术学报,2005,18(2):388-390.

[9]佟首峰,刘金国,阮锦,等.CCD视频信号处理电路应用分析[J].激光与红外,2000,30(6):373-375.