高度综合总线技术硬件平台设计

2011-03-05黄润龙

黄润龙

(中国西南电子技术研究所,成都 610036)

1 引 言

随着电子技术的迅速发展,航天、航空和舰载电子通信系统的高度综合化是当今各自领域发展并且提升系统性能的主要途径之一,而高度综合化的电子通信系统其重要的支撑技术之一是高速的数据总线技术。当前,国内在各电子系统领域其综合化和通用化的快速发展,在机架与综合核心处理器(ICP[1])之间、现场可更换模块之间(即LRM[2]之间)以及模块内部(处理器与处理器、处理器与总线接口芯片)交互的数据量已是爆炸式增长,尤其是机架与ICP和LRM之间,其传递的数据除了一般的控制指令和一般的状态信息外,还传输大量的实时控制消息,再加上有些系统需要传输视频、图像和语音等数据,由此,机架与ICP之间和LRM之间的数据传输应具有高带宽、低延迟、高可靠性的特点,而传统的传输总线技术由于其低带宽、高延迟的局限性,已难以满足当今各个领域电子系统性能提升的综合化和通用化的需求。鉴于当前形式需求并结合工作的需要,成功研制了一种通用化、高度综合集成的总线技术硬件平台,本文将详细讨论硬件实现的方案、原理框图、性能分析及应用领域。

2 方案设计

2.1 硬件平台设计指导思想

一个系统的高度综合反映在组成系统的子系统内(机架内),并最终体现在构筑机架灵魂的LRM上,由此,组成系统的机架内部的LRM的模块化设计更是需要追求其综合化和通用化。随着实现LRM功能的超大规模的ASIC SoC和FPGA内晶体管更缩密化,制造ASIC SoC和FPGA工艺的更先进化,并依托表面贴装(SMT)[3]等先进工艺装配技术,当前国内设计出更先进的高速总线集成平台将成为现实。

笔者根据以上理论分析,罗列出以下硬件设计指导思想:

(1)尽量提供硬件电路的灵活性、可扩充特性;

(2)避免复杂的总线仲裁、冲突结构,在硬件设计时尽量将各总线分开,简化设计,提高电路可靠性;

(3)充分发挥各芯片的特性,将各芯片有机地组合在一起,保证高效率、高可靠地完成电路功能;

(4)硬件模块化、综合化、通用化。

2.2 主要总线选择情况

2.2.1 机架与ICP之间总线选择

为了使机架与ICP之间具有高带宽、低延时和低误码率,参考国外已应用、较成熟且先进的网络总线技术,并结合工作需求,选择了由美国国家标准委员会(ANSI)于1988年负责制定的一种高速串行通信协议的光纤通道(Fibre Channel,FC)作为机架与ICP之间传输的总线,其具有在航天、航空和舰载领域所需求的高带宽、低延时、低误码率的优越性能。芯片上,选择了采用多模光纤传输、光波长为850nm 、光纤 芯径为62.5μm /125μm 的光数转换 芯片进行接收和发送,其传输速率在1.0625~4.25 Gbit/s可选,该设计中使用了2.125 Gbit/s速率,其代表芯片是法国RADIALL公司的D-Light和重庆光电技术研究所的D-Light。

2.2.2 LRM级间总线选择

为了兼顾LRM模块间总线通信适合于各个领域,考虑到高可靠性,LRM级间总线选择了高、低速率搭配的总线形式,其中具有代表性的有CAN总线、基于TIA/EIA-644 LVDS规范的LVDS电平的同步串行点对点总线、基于TIA/EIA-899 M-LVDS规范的总线型的M-LVDS电平总线和异步RS485总线及高速率的RapidIO总线。为了保证硬件平台传输的可靠性,其总线速率可在如下范围内选择:

(1)CAN总线:512 kbit/s或1Mbit/s,遵循CAN2.0B技术规范;

(2)LVDS点对点型同步串行总线:1~200Mbit/s,遵循TIA/EIA-644 LVDS规范;

(3)LVDS总线型同步串行总线:1~100Mbit/s,遵循TIA/EIA-899 M-LVDS规范;

(4)异步RS485总线:2400bit/s~10Mbit/s;

(5)RapidIO 总线:1.25Gbit/s、2.5 Gbit/s或3.125Gbit/s,与RapidIO 1.2版本兼容。

2.2.3 板级内总线选择

该硬件平台采用了当前主流且功能强大的ASIC(PPC处理器)+FPGA构架,其中FPGA主要完成多种类低速总线的采集、串并转换、校验及存储工作并完成基于FPGA的RapidIO总线软核设计工作,PPC主要完成数据协议解析和转发工作。

如何使FPGA和PPC之间的数据在更高带宽和更低延时内完成,成为该硬件平台具有高性能设计的关键之处,由于对外连接的总线为FC总线,其速率为2.125Gbit/s,根据当前高速串行总线的成熟应用情况,在此选择了RapidIO总线作为FPGA和PPC之间传输的桥梁,其RapidIO交换式结构网络局部框图如图1所示。

图1 RapidIO交换网络框图Fig.1 Block diagram of RapidIO exchange network

其中FPGA与交换芯片之间采用两路1x模式,速率分别为3.125 Gbit/s;MPC8548与交换芯采用了4x模式,速率为3.125 Gbit/s,总带宽可达12.5 Gbit/s;同时引出两路1x模式速率分别为3.125 Gbit/s的RapidIO总线到接插件,与机架内其它LRM进行数据交互传输。

2.3 硬件平台原理框图设计

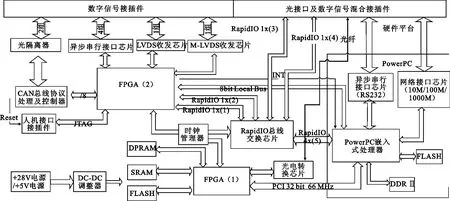

硬件平台原理框图如图2所示,主要由6部分组成。

图2 硬件平台原理框图Fig.2 Principle diagram of hardware platform

(1)FPGA及外围接口

此部分主要功能是完成一组CAN总线、一组总线型LVDS总线、RS485总线、一组点对点LVDS同步串行总线和一些离散信号的数据收发、串并转换及缓存,再由FPGA的RapidIO软核进行对外数据转发。

(2)RapidIO交换芯片

此部分完成硬件平台内部具有RapidIO总线接口芯片之间和外部模块之间的RapidIO总线数据交换。

(3)FC网络功能块

此部分完成ICP过来的光信号转PCI总线功能。

(4)MPC8548功能块

MPC8548是协议处理的核心部分,是整个硬件平台软件管理中心。

(5)面板人机接口

引出FPGA的JTAG口以及外部手动复位等信号,便于调试。

(6)电源

需要完成外部输入+28 V或+5 V电源的转换,得到所需要的+1 V、1.5 V、+1.8 V、+2.5 V、+3.3 V和+5 V(+28V供电的情况下)电源。

2.4 工作流程

2.4.1 下传数据流

硬件平台的FC网络功能块接收到外部FC总线下发的数据流后,经PCI总线给MPC8548处理器进行处理、解析并分发,经TSI578交换芯片,依据用户所需的相应功能,通过RapidIO总线、CAN总线、M-LVDS总线、LVDS同步串行总线分发给机架内其它模块,其流程图如图3所示。

图3 硬件平台传输流程图Fig.3 Transmission flowchart of hardware

2.4.2 上传数据流

硬件平台接收到机架内其它模块过来的各种不同总线类型(CAN、M-LVDS、LVDS同步串行及RS485)的数据后,通过各自转换电路转换成FPGA所需电平格式,在FPGA内部进行缓存或串并转换,通过FPGA的RapidIO总线接口经RapidIO总线交换芯片转发给MPC8548处理器,经光电转换后通过FC总线与外部机架交联。其流程图与图3相反。

2.5 硬件设计

2.5.1 FPGA及外围接口

FPGA采用了V5系列SX95T的内部可集成与1.2版本兼容的RapidIO软核,与外部LVDS、MLVDS接口芯片和CAN总线协议芯片及光隔组成该硬件平台低速总线与高速RapidIO总线的衔接。

2.5.2 RapidIO总线交换部分

RapidIO总线交换芯片采用当前电子应用领域较为主流的美国IDT公司的TSI578交换芯片,该芯片集成了16路1x通路或8路4x RapidIO总线接口,能够很好地完成主、从RapidIO总线节点高速交换通信。

2.5.3 FC网络功能块

FC功能块采用了光电转换芯片+FPGA框架完成,其中光电转换芯片(D-Light)完成光信号转换数字信号,FPGA(内嵌PowerPC核)完成高速、大容量的数字信息转换为66 MHz、32 bit的PCI总线形式的数字信号。

2.5.4 MPC8548功能块

MPC8548功能块采用了货架产品,其实现框图如图4所示。

图4 MPC8548硬件框架Fig.4 MPC8548 hardware framework diagram

MPC8548功能块对外接口主要有如下方式:

(1)SRIO接口:采用 4x方式,速率为3.125 Gbit/s;

(2)PCI接口:66 MHz时钟,32 bit数据位宽;

(3)Local Bus:8 bit,异步模式;

(4)RS232调试口:两路;

(5)以太网接口:两路,要求10Mbit/s、100Mbit/s、1000Mbit/s自适应,可作为调试口或平台维护口。

3 性能测试及应用

3.1 性能测试

为了验证硬件平台性能指标,FC网络模拟器通过FC总线与硬件平台交互数据,另一端用一块具有RapidIO总线的收发板卡来模拟机架内部其它LRM模块来交互数据,其测试框图如图5所示。

图5 硬件平台测试示意图Fig.5 Illustration of hardware platform test

图5中分三阶段来验证FC总线、RapidIO总线以及FC总线到RapidIO总线的有效带宽。

3.1.1 FC总线验证

环境需求:控制及监视计算机1(PC1)、FC模拟器、总线硬件平台、控制及监视计算机2(PC2)。

验证过程:通过PC1向FC模拟器发送指令,FC模拟器组帧并周期向总线硬件平台发送块数据,总线硬件平台接收到数据后进行数据解析及CRC校验,再将接收数据的状态通过PC2显示及记录。

额外开销:

发送端:应用层的组帧、FC-AE-ASM协议处理、8B/10B编码、底层传输;

接收端:FC-AE-ASM协议处理、8B/10B解码、FC功能块内PCI总线传输、MPC8548处理器解析及处理。

验证结论:有效带宽达640Mbit/s。

3.1.2 RapidIO总线验证

环境需求:PC2、总线硬件平台、RapidIO总线收发板卡、PC3。

验证过程:通过PC1向FC模拟器发送指令,FC模拟器组帧并周期向总线硬件平台发送块数据,总线硬件平台进行数据解析及CRC校验后转发给RapidIO总线接收板卡,RapidIO总线接收板卡对数据进行解析、CRC校验,并将接收数据的状态通过PC3显示及记录。

额外开销:

发送端:应用层的组帧、RapidIO协议处理、8B/10B编码、底层传输、RapidIO交换转发;

接收端:RapidIO交换转发、8B/10B解码、RapidIO协议处理、MPC8548处理器解析及处理。

验证结论:有效带宽达1024Mbit/s。

3.1.3 FC总线到RapidIO总线验证

环境需求:PC1、FC模拟器、总线硬件平台、RapidIO总线收发板卡、PC3。

验证过程:通过PC2向总线硬件平台发送指令,总线硬件平台组帧并周期向RapidIO总线收发板卡发送块数据,RapidIO总线接收板卡接收到数据后进行解析、CRC校验,将接收数据的状态通过PC3显示及记录。

额外开销:

发送端:应用层的组帧、RapidIO协议处理、8B/10B编码、底层传输、RapidIO交换转发;

中间件:FC-AE-ASM协议处理、8B/10B解码、FC功能块内PCI总线传输、MPC8548处理器解析及处理;应用层的组帧、RapidIO协议处理、8B/10B编码、底层传输、RapidIO交换转发;

接收端:RapidIO交换转发、8B/10B解码、RapidIO协议处理、MPC8548处理器解析及处理。

验证结论:有效带宽达640Mbit/s;FC总线经过应用层、协议层再通过PCI总线传输转发,降低了其有效传输带宽。

低速总线与高速总线的交互在工程领域得到了充分验证,在此不再论述。

3.2 应用情况

综合化总线技术硬件平台已应用到几个子系统工程领域,并通过了相应的环境试验验证,满足了当前我国综合化雷达、CNI和EW[4]应用需求。

4 结 论

通过研究、设计和验证,表明了硬件平台在集成了FC、RapidIO和PCI高速总线设计的正确性,在与低速总线的配套交互,作为通用件应用到不同的子系统领域,虽然其高速总线通信有效数据带宽仍然偏低,但能满足当前系统需求。后续研究将着重考虑在FC总线解析后不再采用2.112 Gbit/s的PCI总线转发到MPC8548功能块,而考虑采用3.125 Gbit/s的RapidIO总线与MPC8548功能块交互,并优化应用层面的时延,更大提高有效数据带宽。

高度综合总线技术硬件平台的研制成功,依托的是更先进电子技术的发展和芯片工艺的提升,为今后一段时期总线集成技术提供了一定的参考价值,为航天、航空和舰载的综合化、小型化及通用化的发展具有一定的借鉴意义,并为今后向更高速总线技术研究开发奠定了坚实基础。

[1]罗巧云,高勇强.美军第四代战斗机F-35“联合攻击战斗机”最卓越的航空电子系统[J].电子科学技术评论,2005(4):5-8.LUO Qiao-yun,GAO Yong-qiang.The Superexcellent Avionics System of F-35[J].Review of Electronics Sciece and Technology,2005(4):5-8.(in Chinese)

[2]金延中,卢永吉,杨林.军机LR M及其关键技术研究[J].飞机设计,2009(6):33-36.JIN Yan-zhong,LU Yong-ji,YANG Lin.Research on LR M andIt′sKey Technologies ofMilitary Aircraft[J].Aricraft Design,2009(6):33-36.(in Chinese)

[3]郭延涛,徐克林,李振飞.SMT生产线生产配置策略选择研究[J].现代制造工程,2009(7):62-64.GUO Yan-tao,XU Ke-lin,LI Zhen-fei.Research on the decisionof the setupstrategies for a SMT production line[J].Modern Manufacturing Engineering,2009(7):62-64.(inChinese)

[4]车颖秋.航空电子传感器的综合化[J].电讯技术,2002,42(3):145-151.CHE Ying-qiu.An Overview of Avionic Integrated Sensor[J].Telecommunication Engineering,2002,42(3):145-151.(in Chinese)